計數器種類

1、如果按照計數器中的觸發器是否同時翻轉分類,可將計數器分為同步計數器和異步計數器兩種。

2、如果按照計數過程中數字增減分類,又可將計數器分為加法計數器、減法計數器和可逆計數器,隨時鐘信號不斷增加的為加法計數器,不斷減少的為減法計數器,可增可減的叫做可逆計數器。

計數器應用

計數器應用包括通話、短信、數據等類別的記錄,并支持用戶自主選擇清零日期,以及按照類別添加提醒數值,如用戶可以選擇每月任一一天,或者第一天、最后一天作為記錄循環清零日,同時添加通話時長、短信條數、數據流量數量的提醒節點。

計數器的應用極為廣泛,不僅能用于計數,還可用于分頻、定時,以及組成各種檢測電路和控制電路。

計數器設計前言

計數器是數字邏輯系統中的基本部件, 它是數字系統中用得最多的時序邏輯電路,其主要功能就是用計數器的不同狀態來記憶輸入脈沖的個數。除此以外還具有定時、分頻、運算等邏輯功能。 計數器不僅能用于對時鐘脈沖的計數, 還可使用于定時、分頻、產生節拍脈沖以及進行數字運算等。只要是稍微復雜一些的

數字系統, 幾乎沒有不包含計數器的。通常把滿足N=2n的計數器稱為二進制規則計數器, 有些數字定時、分頻系統中,常需要N≠2n 的任意進制計數器。

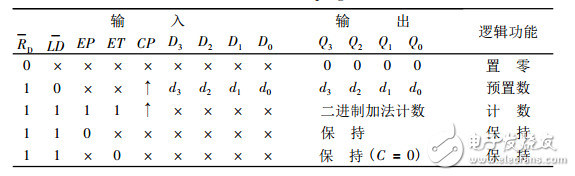

當我們在設計任意進制計數器 (即計數模不是 2及10)時, 一般采用現有的中規模集成電路( Medium Scale Integration, MSI)芯片, 通過適當的反饋連接加以實現。而市場上現成的中規模集成電路芯片常見的只有十進制計數器和十六進制計數器,而在實際應用中,如數字鐘電路中,卻需要二十四進制和六十進制計數器,因此要將現有計數器改造成任意進制計數器。利用MSI芯片進行適當的連接就可以構成任意進制計數,所使用的方法主要有反饋置零法、反饋預置法和級聯法。

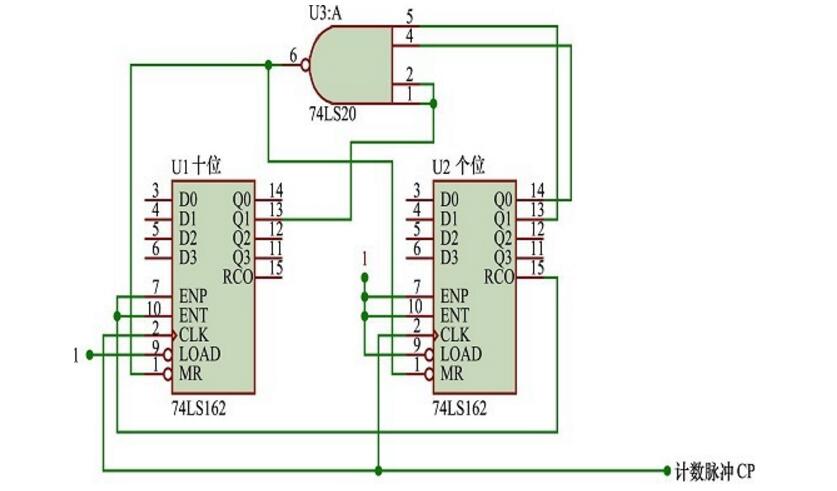

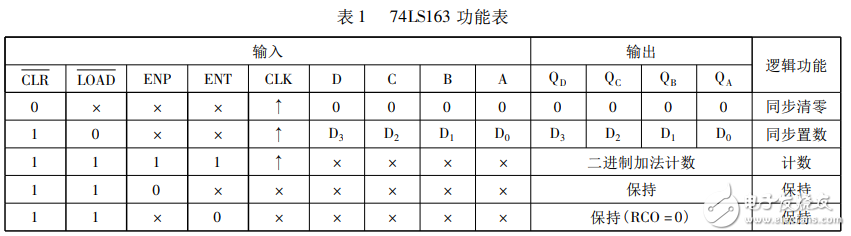

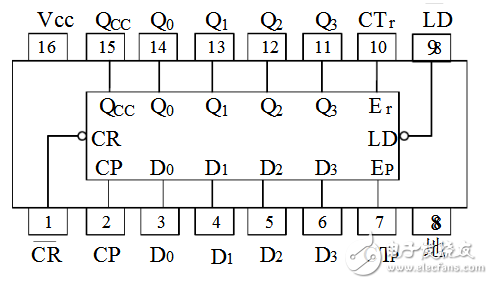

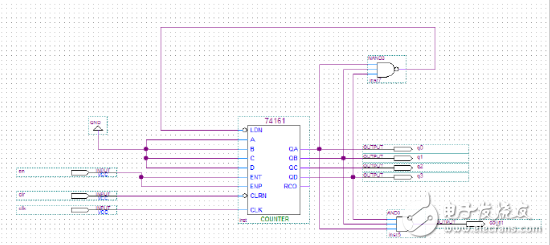

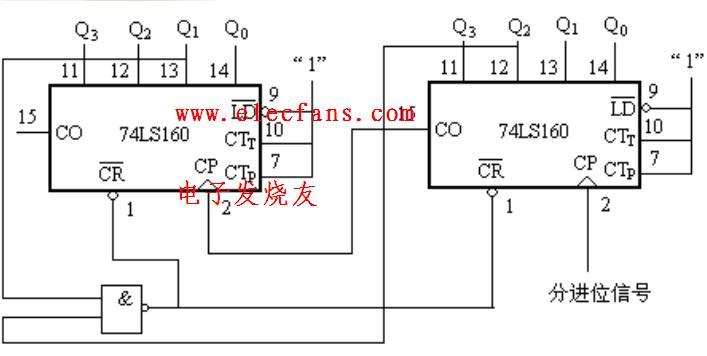

74LS160并行置零法設計24進制計數器電路

用 74LS160并行置零法設計 24進制計數器的電路圖如圖 1所示。此電路的工作原理: 先假設兩芯片的置零輸入端為 1, 則個位芯片由于計數控制端 ENP = ENT = 1, 故該芯片始終處于計數狀態; 而十位芯片的 ENP、ENT連接的是個位芯片的進位控制端 RCO, 只有當個位芯片的計數狀態 Q 3Q 2 Q1 Q0為 1001時, RCO 才為 1.十位芯片才能計數。如果沒有反饋置零 (即 MR 端恒接高電平 )則電路是一個 100進制計數器。現在電路中加上了反饋, 當計數狀態 ( 00100100) 8421BCD碼 = ( 24) 10時, 與非門輸出為零。由于 74LS160 屬于異步置零, 且復位控制端 MR低電平有效, 所以計數器立即置零。由于電路中的狀態 ( 24 ) 10轉瞬即逝, 顯示不出。故電路的有效狀態從 ( 00) 10到 ( 23) 10共 24個, 故此電路為24進制計數器。

圖1 用74LS160并行置零法設計24進制計數器

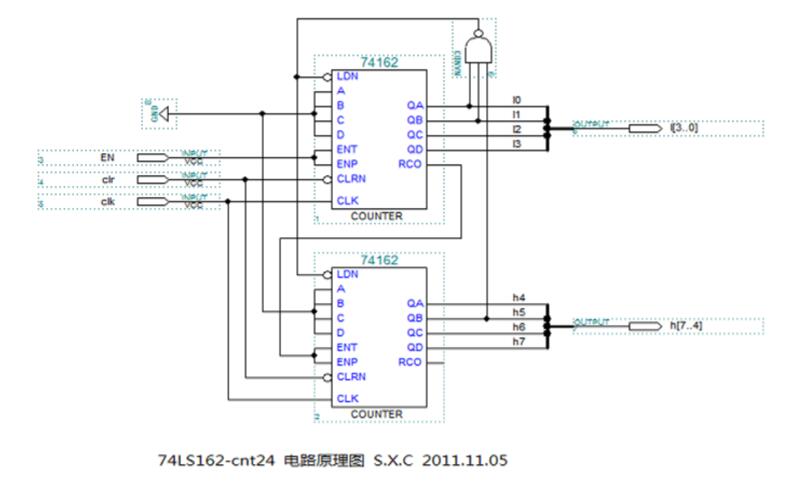

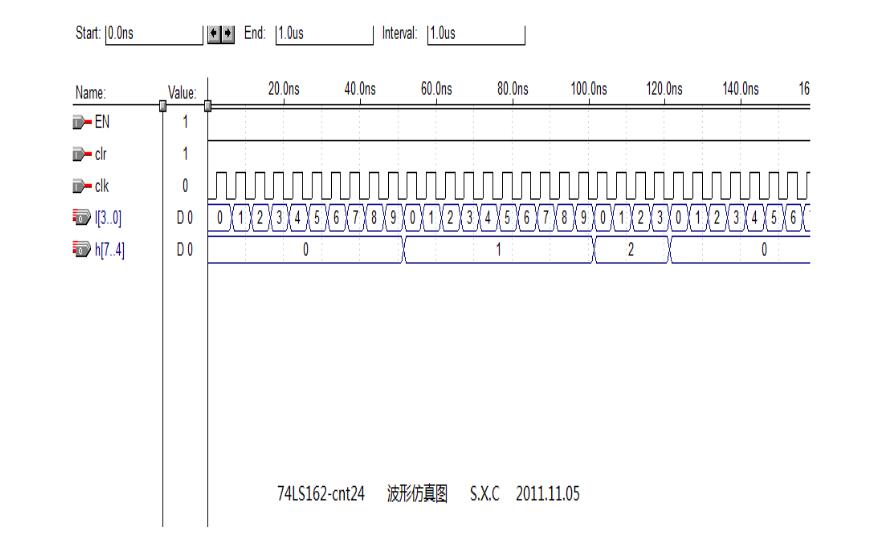

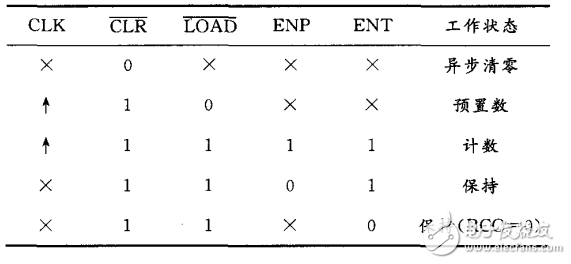

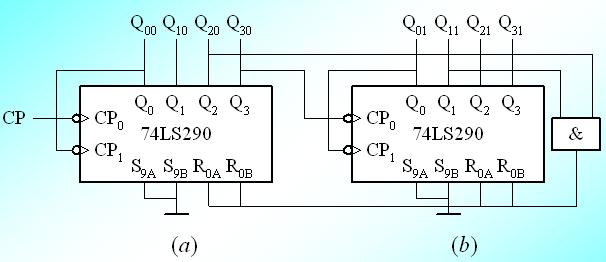

同步計數器74ls162設計24進制計數器原理圖

74LS162計數器是十進制計數方式的計數器,且其實同步清零方式。所以設計24進制計數器,則Sn.1=100011的非。

注意:

1.在文件名必須與VHDL文件中的設計實體名保持一致。

2.低位的清零輸出端(CO端)要連接高位的使能端。

3.低位端和高位端的輸出端統一接地或輸入置零。

4.低位端和高位端的的置數端要統一。

74ls162設計24進制計數器

采用同步置零 74LS162計數器來設計24進制計數器, 反饋代碼必須是 ( 23) 10相應的8421BCD 碼為 00100011.由此可見反饋信號應取自十位芯片的 Q1 及個位芯片的 Q1 和 Q0, 相應的與非門應改成四輸入端與非門。用 74LS162并行置零法設計 24進制計數器的電路圖如圖 2所示。

圖2 用74LS162并行置零法設計24進制計數器

電子發燒友App

電子發燒友App

評論