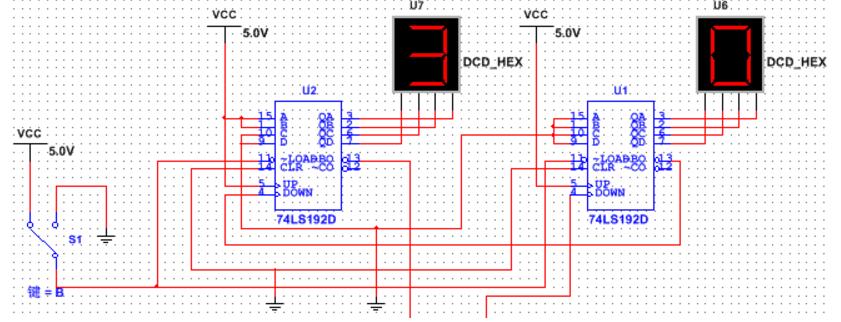

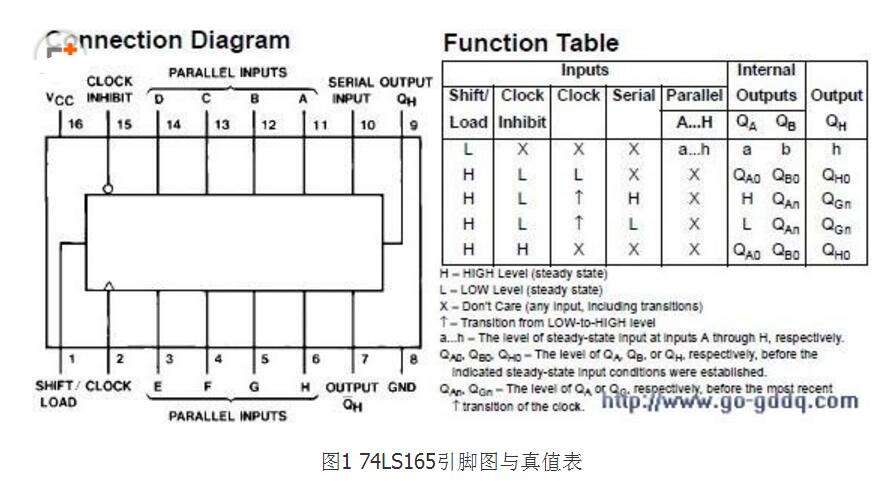

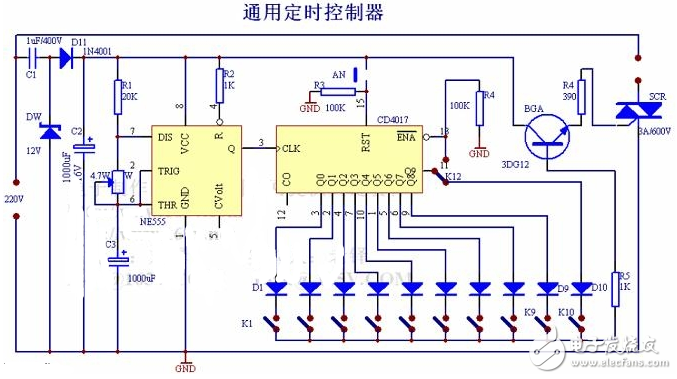

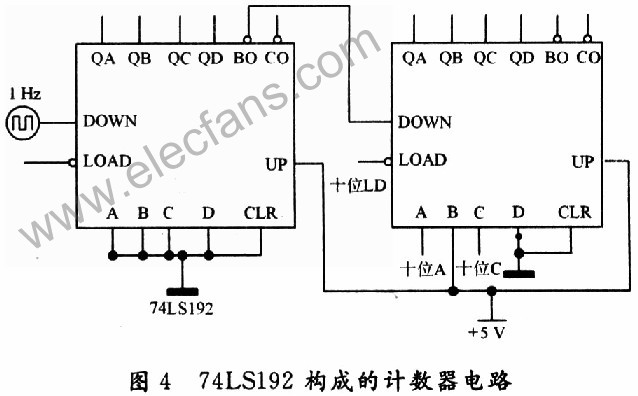

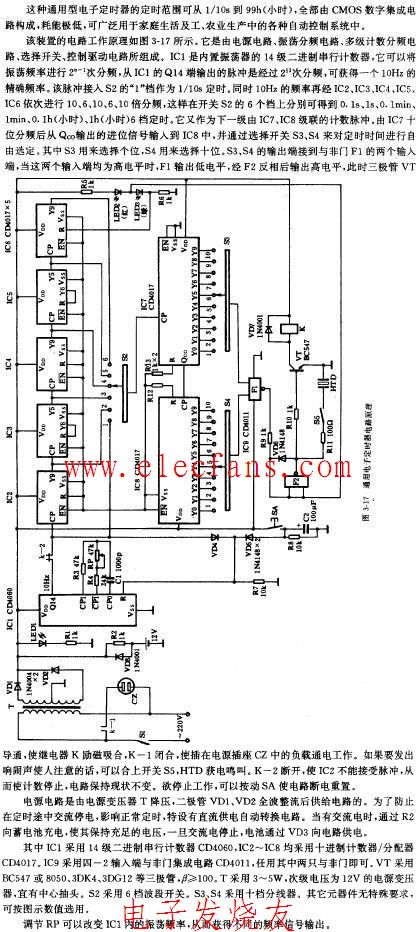

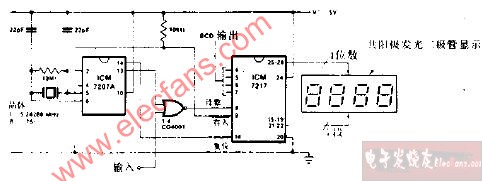

74ls192計(jì)數(shù)器應(yīng)用電路圖四:30進(jìn)制計(jì)數(shù)器電路

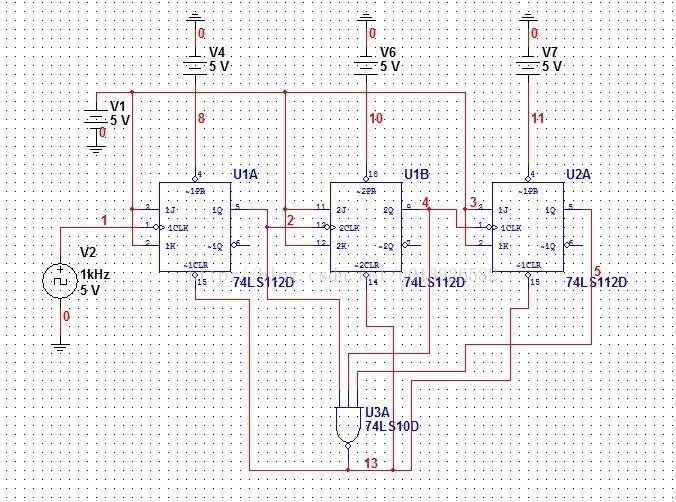

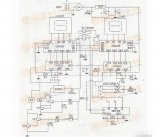

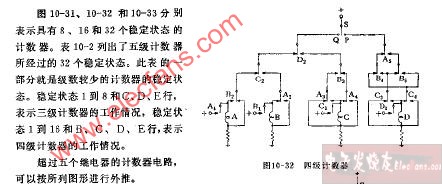

本實(shí)驗(yàn)采用74LS192芯片作為計(jì)數(shù)器,74LS192是同步的加減計(jì)數(shù)器,其具有清除和置數(shù)的功能。本實(shí)驗(yàn)選擇兩片74LS192作為分別作為30的十位和個(gè)位。本實(shí)驗(yàn)中將作為十位的計(jì)數(shù)器輸入端置為0011而將個(gè)位的輸入端置為0000。將兩片74LS192的置數(shù)端連出來與開關(guān)B相連,開關(guān)B控制置數(shù)端與高電平還是低電平,從而實(shí)現(xiàn)當(dāng)30倒計(jì)時(shí)到00時(shí),通過手動(dòng)操作開關(guān)B而可以重新開始倒計(jì)時(shí),計(jì)數(shù)器的電路連接如下圖所示:

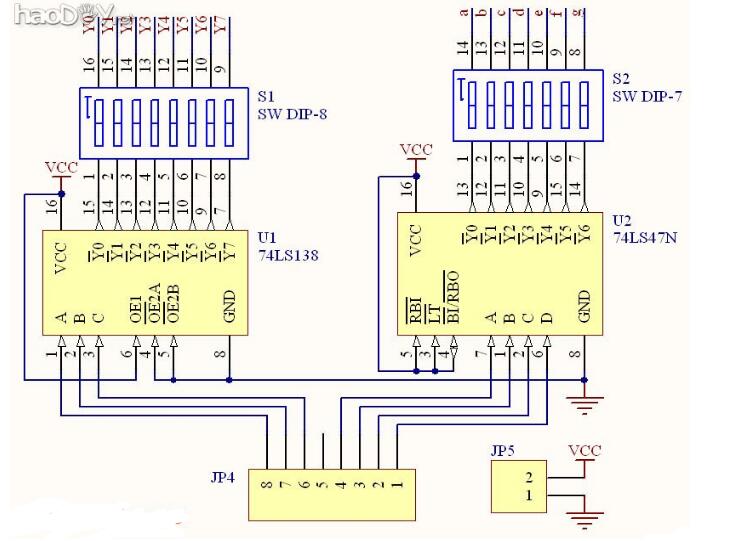

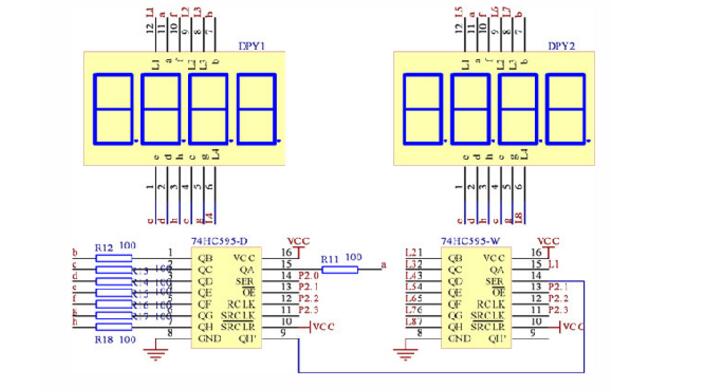

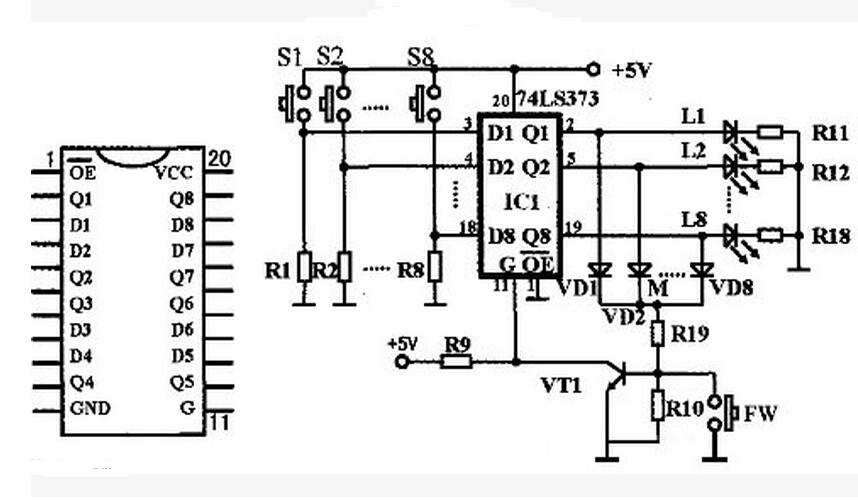

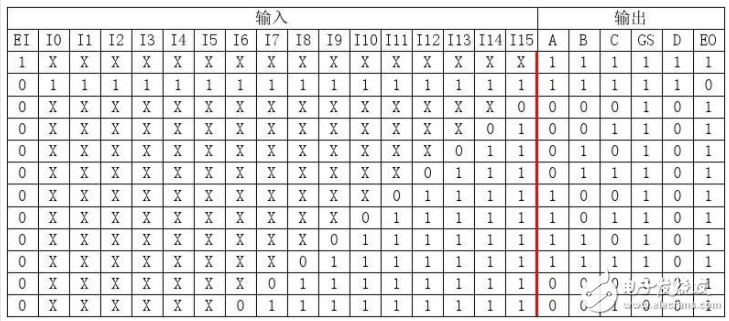

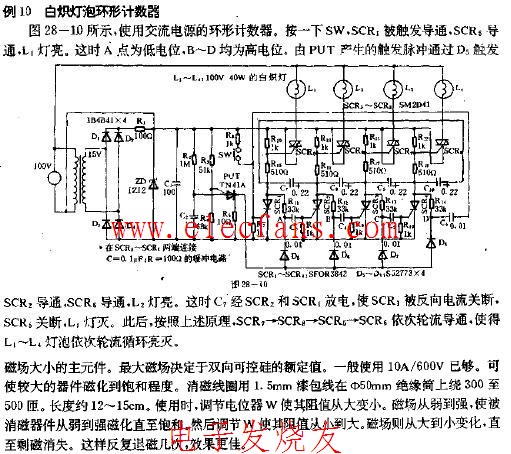

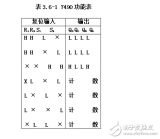

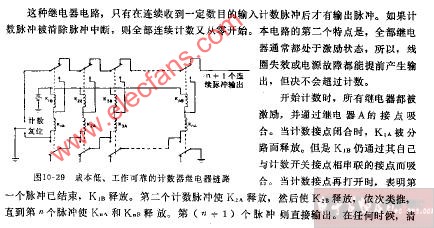

74ls192計(jì)數(shù)器應(yīng)用電路圖五:兩位十進(jìn)制計(jì)數(shù)器

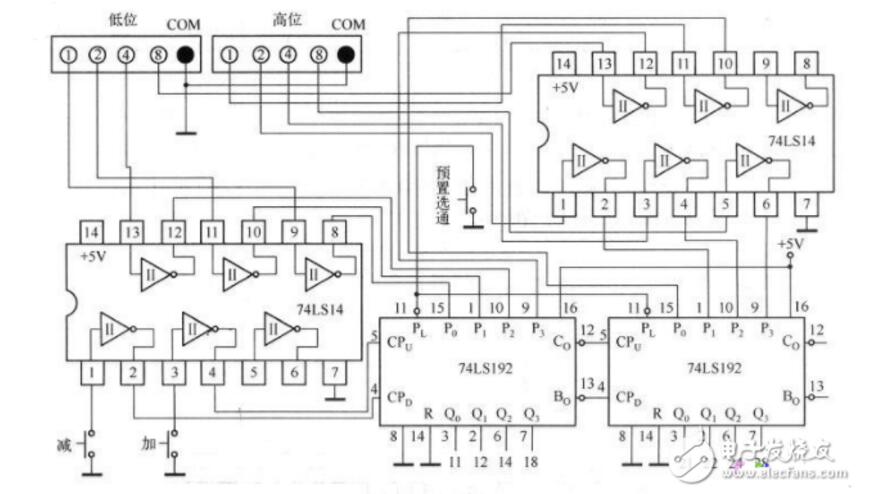

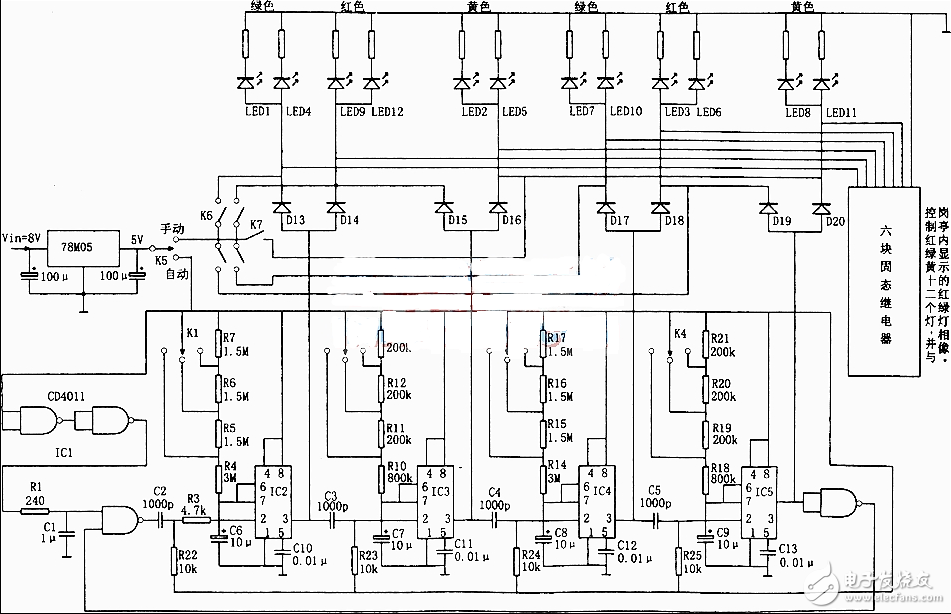

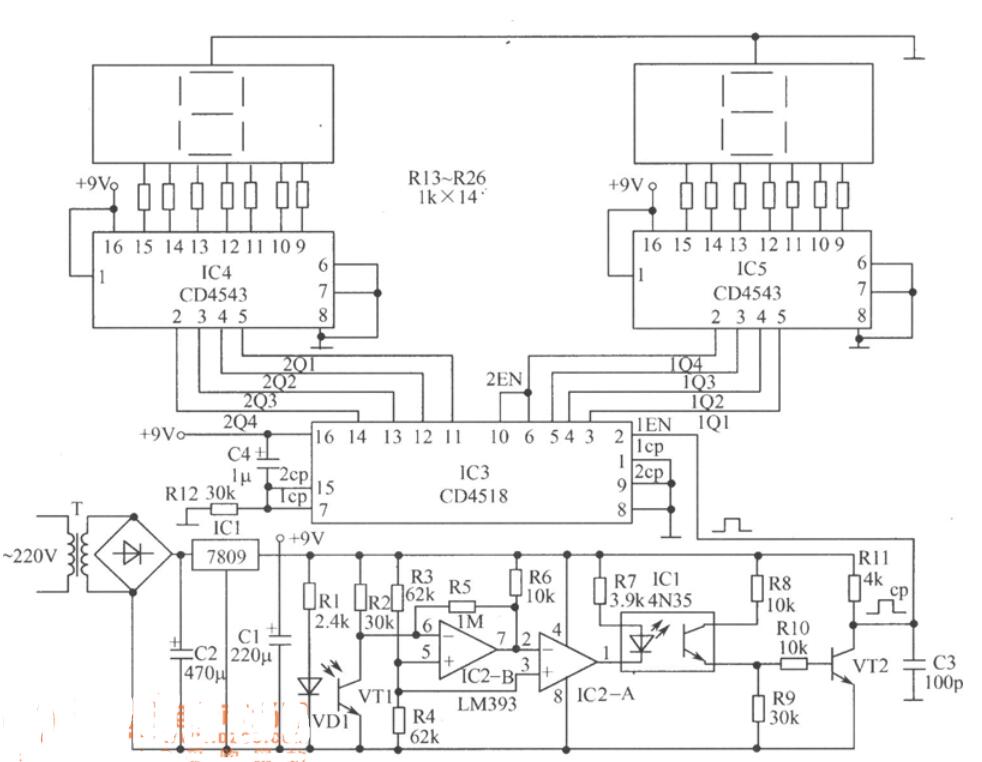

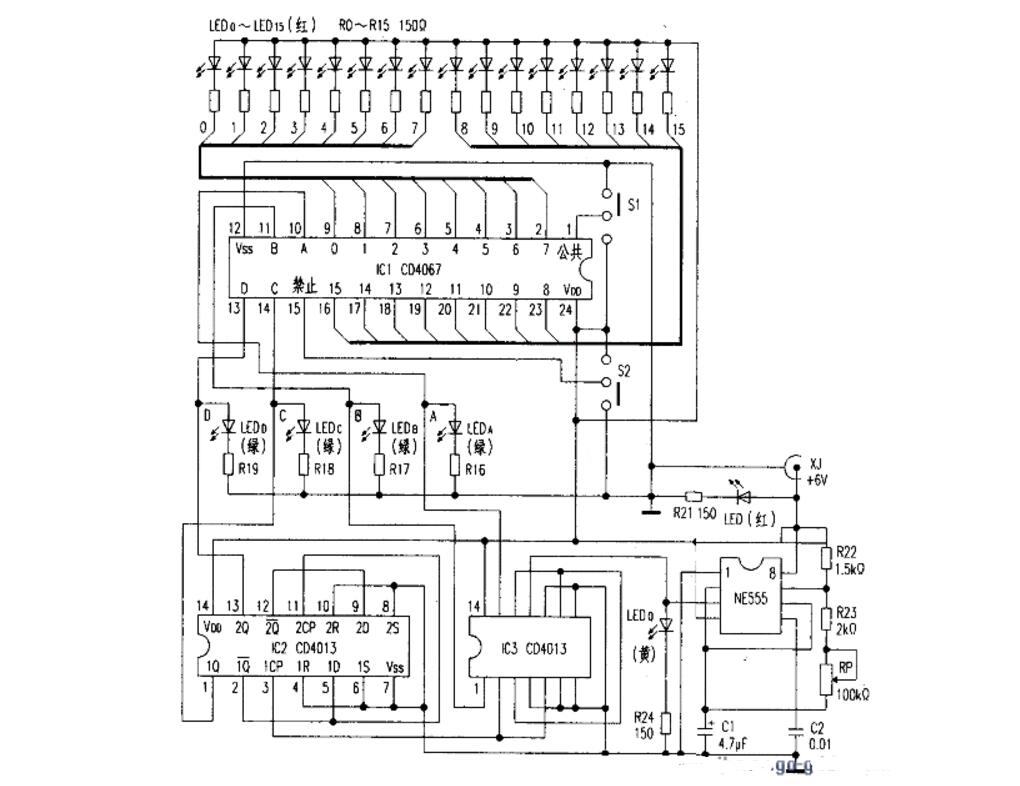

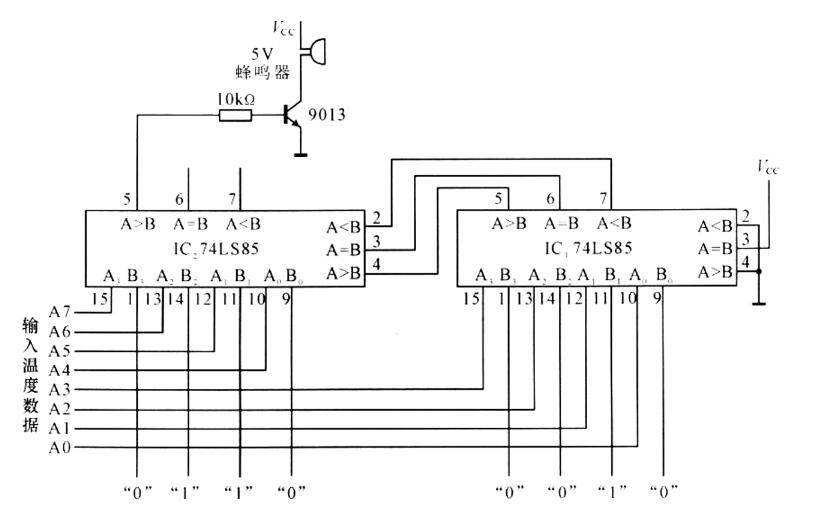

下面以兩個(gè)74LS192級(jí)聯(lián)構(gòu)成兩位十進(jìn)制計(jì)數(shù)器控制實(shí)現(xiàn)0.0~9.9V的切換為例。低位計(jì)數(shù)器輸出Qo、Qi、Q2、Q3分別提供0.1V、0.2V、0.4V、0.8V的控制信號(hào);高位計(jì)數(shù)器輸出Qo.Qi、Q2、Q3分別提供1V、2V、4V、8V的控制信號(hào)。采用按鍵作為步進(jìn)加、步進(jìn)減的控制按鈕;為了防止在按鈕過程中出現(xiàn)振鈴現(xiàn)象,在計(jì)數(shù)器加計(jì)數(shù)、減計(jì)數(shù)時(shí)鐘脈沖端與加、減計(jì)數(shù)按鈕之間接入施密特觸發(fā)器74LS14,以消除振鈴現(xiàn)象。

預(yù)置數(shù)選通端可以接撥碼開關(guān),以實(shí)現(xiàn)預(yù)置數(shù)的設(shè)置;用開關(guān)控制預(yù)置數(shù)選通端的選通狀態(tài),開關(guān)閉合時(shí)預(yù)置數(shù)選通端為低電平,選通端有效,預(yù)置數(shù)送到輸出端;開關(guān)斷開時(shí)預(yù)置數(shù)選通端為高電平,選通端無效,不能將預(yù)置數(shù)送到輸出端。

由兩個(gè)74LS192級(jí)聯(lián)構(gòu)成兩位十進(jìn)制計(jì)數(shù)器的電路如下圖所示。

在圖中,1V以下的計(jì)數(shù)器74LS192的時(shí)鐘可以由“+”、“-”兩鍵分別控制輸出電壓步進(jìn)增減,1V以上的計(jì)數(shù)器74LS192的加、減計(jì)數(shù)時(shí)鐘則由低位的進(jìn)、借位輸出提供。

如果需要3位以上的減計(jì)數(shù)和預(yù)置數(shù),則可以在圖中的基礎(chǔ)上繼續(xù)級(jí)聯(lián)192、相應(yīng)的撥碼開關(guān)及相應(yīng)的74LS14,直到滿足要求為止。

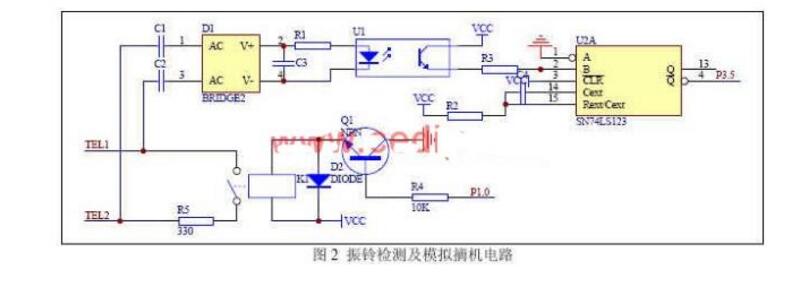

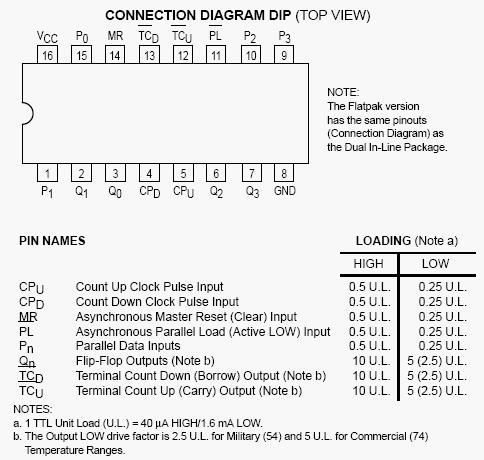

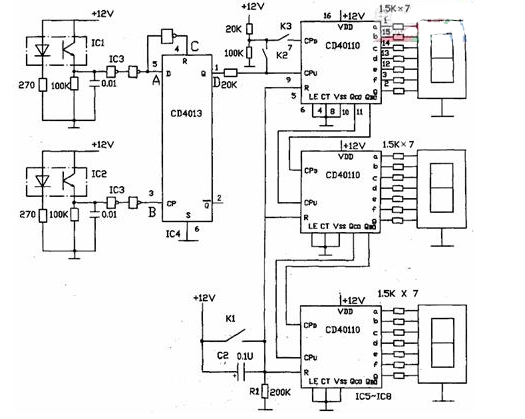

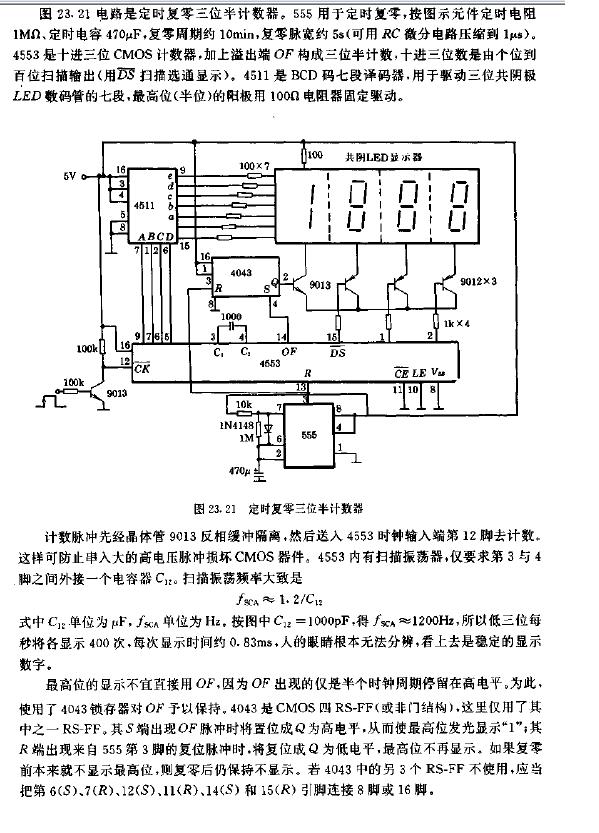

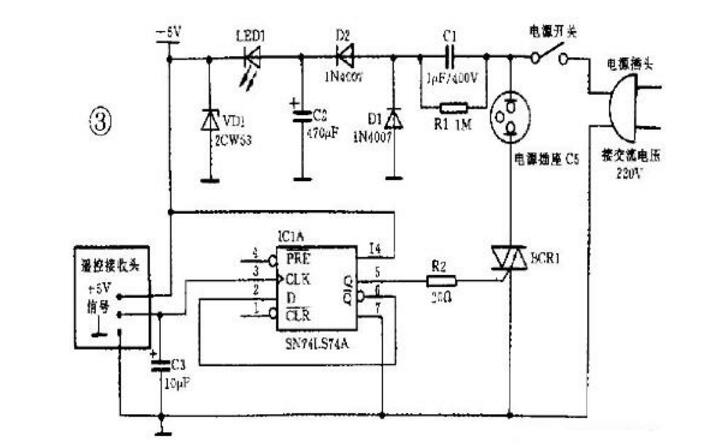

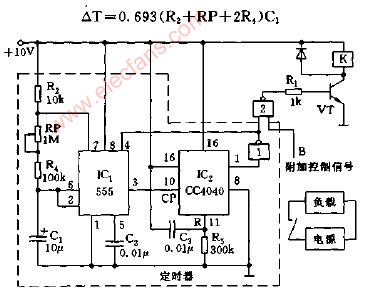

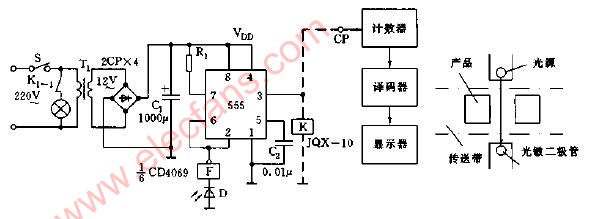

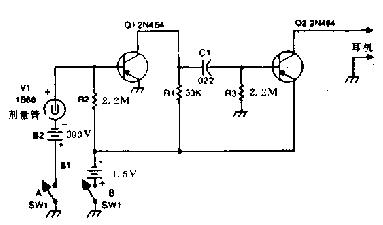

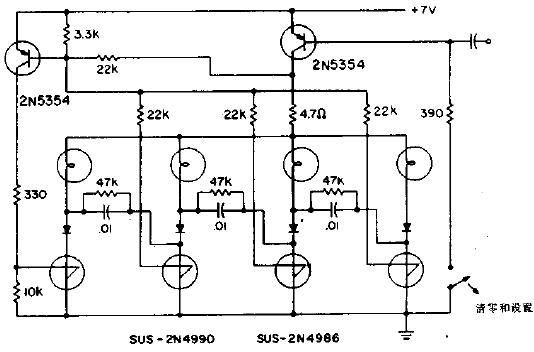

74LS192的輸出接驅(qū)動(dòng)繼電器激磁線圈的晶體管基極,如下圖所示。

為了使晶體管與TTL電平匹配,需要在74LS輸出與晶體管基極之間串聯(lián)適當(dāng)?shù)碾娮瑁?5~20kΩ的電阻,同時(shí)在晶體管基極與發(fā)射極之間并聯(lián)lOkΩ的電阻,以確保在74LS192輸出低電位時(shí)晶體管處于關(guān)斷狀態(tài)。

電子發(fā)燒友App

電子發(fā)燒友App

評論