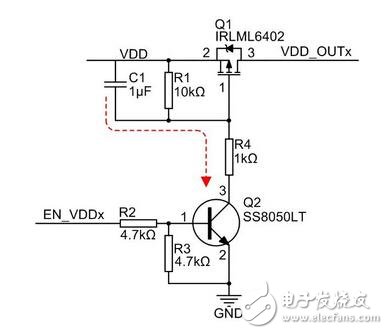

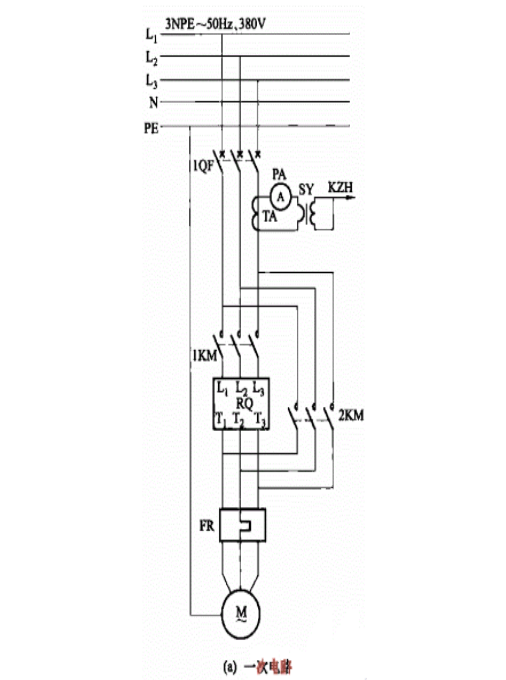

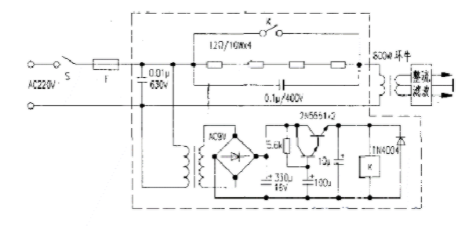

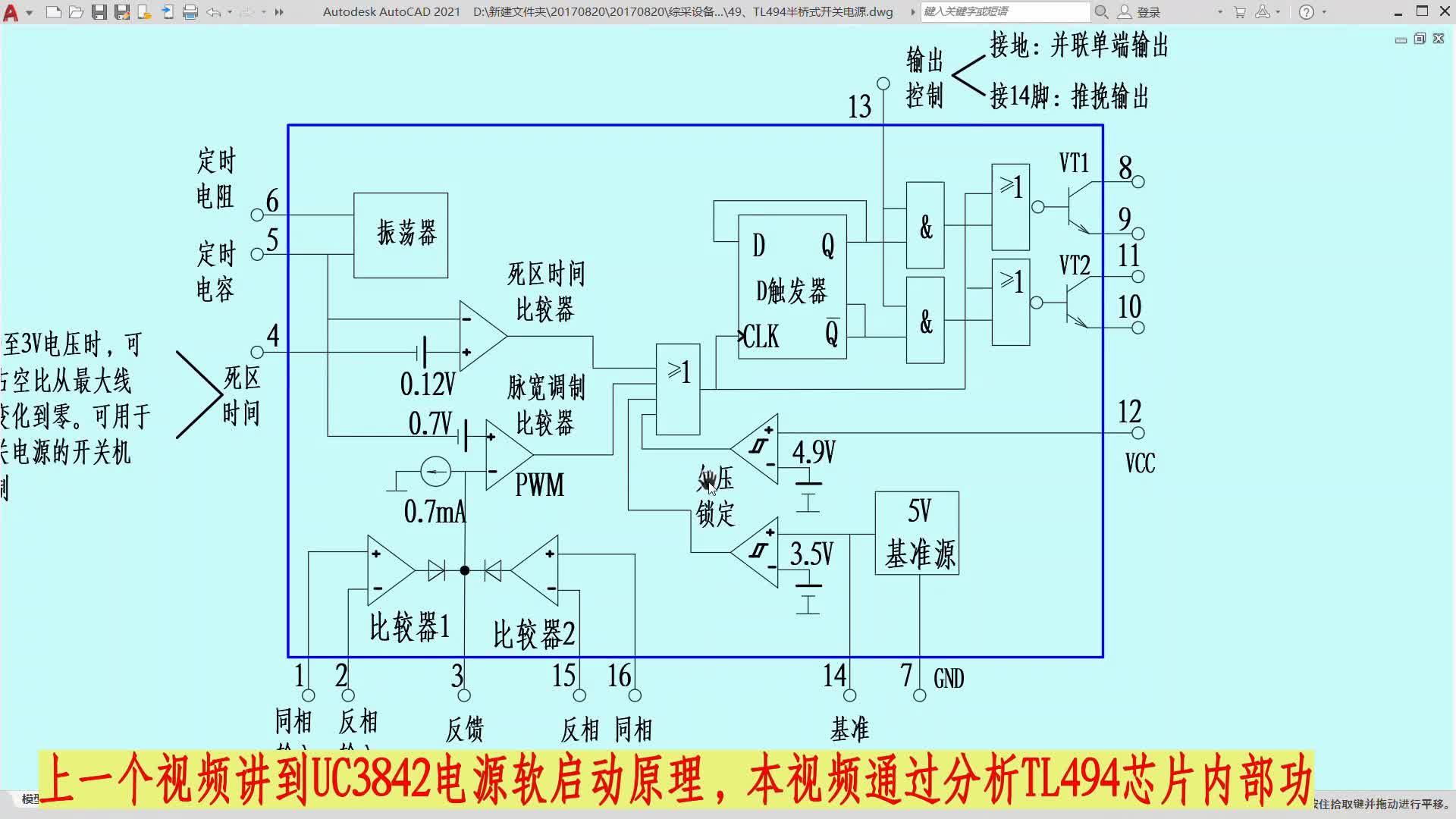

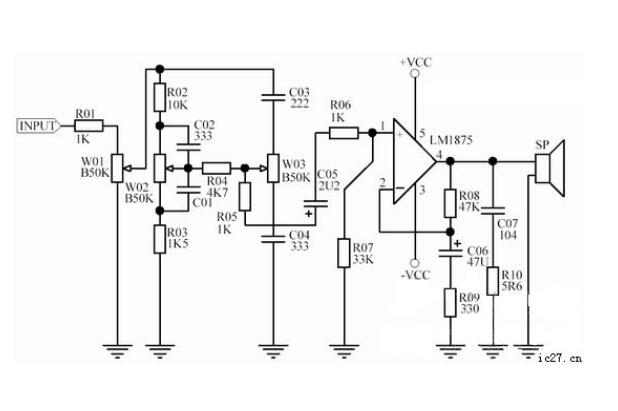

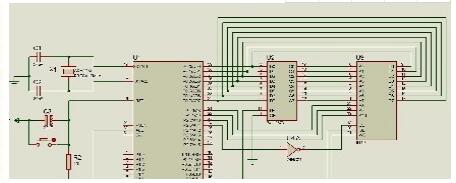

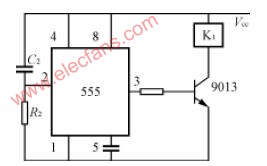

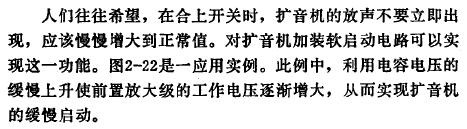

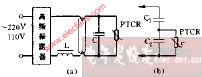

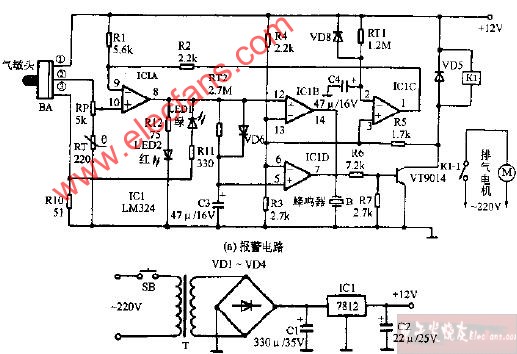

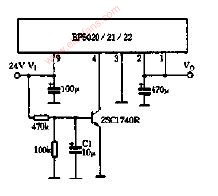

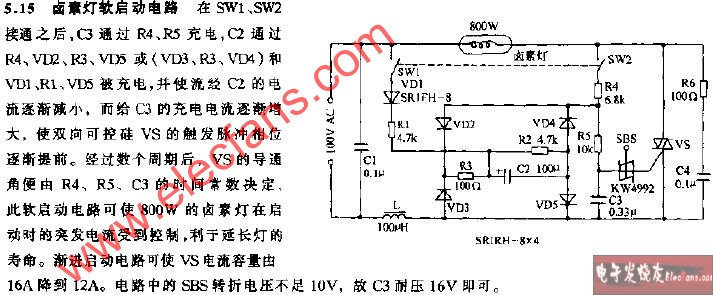

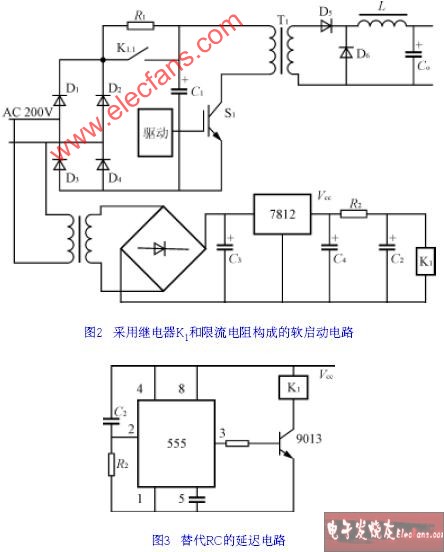

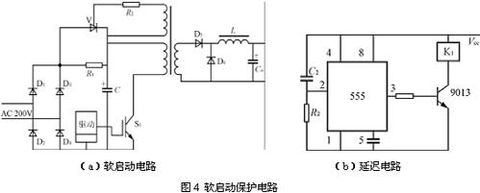

從波形圖可以看到,在VDD_OUTx上升過程中,VDD從3.12V瞬間跌落至2.14V,再緩慢回升至3.12V,最大跌落幅度達 980mV.由于另外3個通道的電源也由VDD提供,因此這3個通道在線燒寫失敗也就在所難免。VDD_OUTx的上電為什么會造成VDD跌落呢?觀察波形圖我們還可以發現,VDD_OUTx從0V上升到2V只用了3μs,根據電容充電公式:I=C×dU / dt,VDD_OUTx的去耦電容4.7μF,據此估算出浪涌電流達3A!正如前面所述,過大的浪涌電流最終造成了輸入電源的降低。為了限制浪涌電流,可以將軟啟動引入開關電路中,利用Q1的導通阻抗RDS(on)隨VGS變化的特性,通過延緩Q1導通的速度,使VDD_OUTx緩慢上升到VDD.引入的軟啟動電路如下圖的C1、R4所示。

當Q2集電極變低時,C1通過R4放電,Q1柵極電壓隨之緩慢下降,從而控制Q1緩慢導通,使VDD_OUTx不會發生突變。用示波器ZDS2022觀察VDD_OUTx上電過程中VDD的變化,得到如下波形。

和加入軟啟動之前的波形圖對比可以看到,VDD_OUTx的上升時間延長到了400μs,VDD的跌落問題也得到明顯改善。經過長時間反復測試,都沒有再出現燒錄失敗現象。就是這樣一個不起眼的軟啟動電路,卻大大提升了編程器燒錄的穩定性。生活中的一些小細節總能給人帶來意想不到的驚喜,工作也是如此。

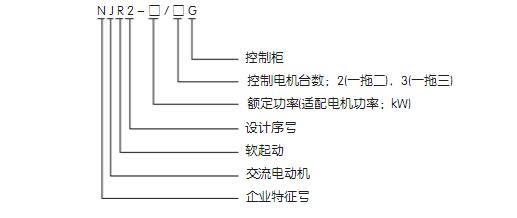

編輯點評:本文主要介紹了軟啟動電路設計,具體作用就是用于電源啟動時,減小浪涌電流,使輸出電壓緩慢上升,減小對輸入電源的影響。請看軟啟動是如何幫助燒錄器,提高燒錄的穩定性和可靠性的。

電子發燒友《無線通信特刊》,更多優質內容,馬上下載閱覽

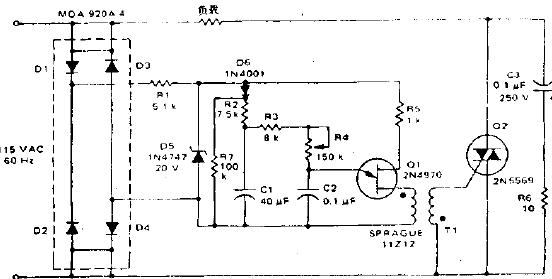

電子發燒友App

電子發燒友App

評論