電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 0

0 數字濾波器是數字信號處理中最常用的一種技術,可以對數字信號進行濾波、降噪、增強等處理,其中最常見的兩種數字濾波器是IIR濾波器和FIR濾波器。本文將從IIR濾波器和FIR濾波器的原理、特點和應用等方面進行詳細介紹,以便更好地理解兩種濾波器的區別。

2023-06-03 10:21:43 6407

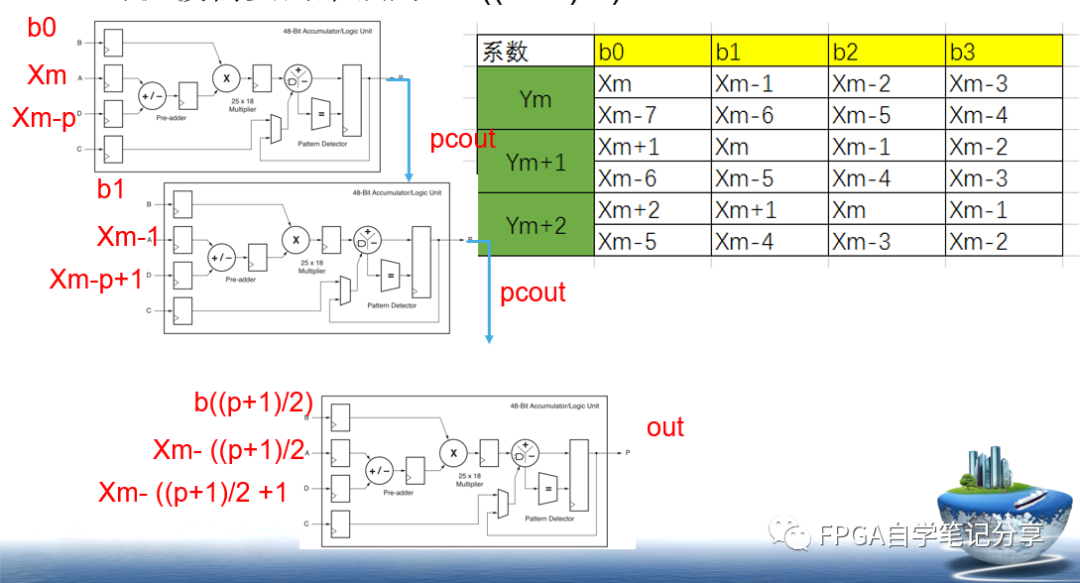

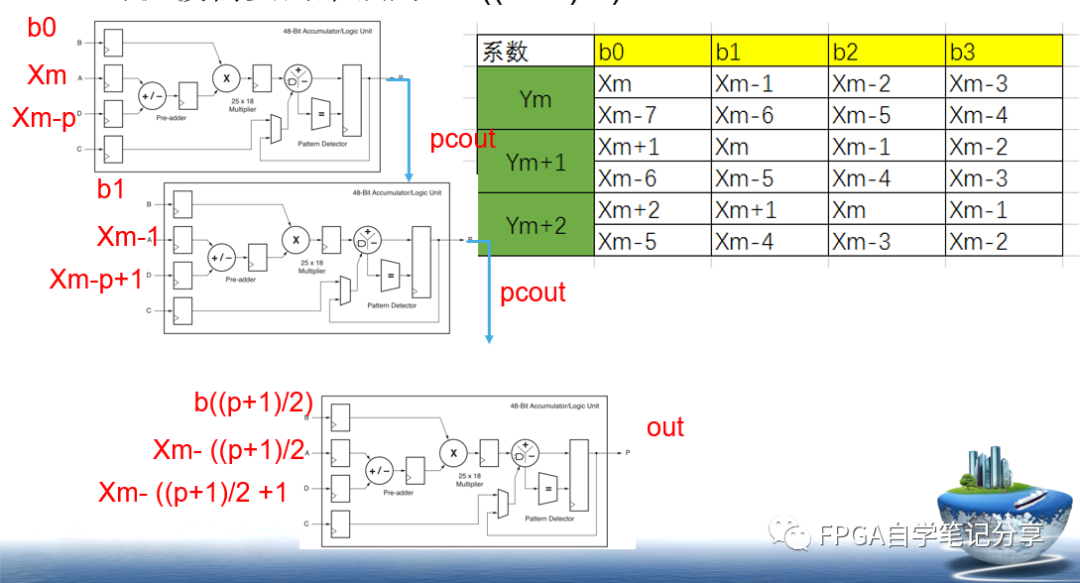

6407 上文 FPGA數字信號處理之濾波器2_使用dsp48e1的fir濾波器設計完成了結構設計。

2023-06-02 12:36:22 360

360

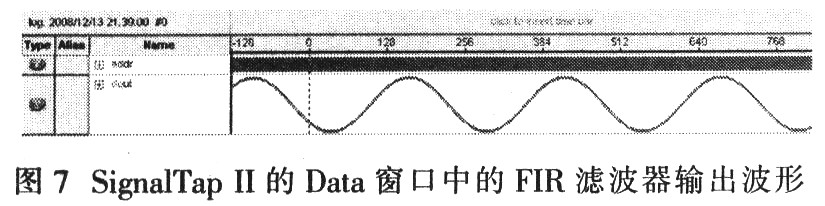

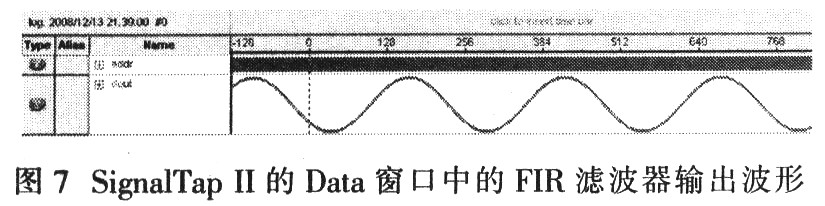

DSPBuilder設計了一個4階FIR濾波器,并用QuartusII進行硬件仿真,仿真結果表明設計FIR濾波器的正確性。同時使用IPCore開發基于FPGA的FIR數字濾波器,利用現有的IPCore在FPGA器件上實現濾波器設計。

2012-08-11 15:32:34

點擊上方 藍字 關注我們 本文將回顧對稱 F IR ? 濾波器 的高效 FPGA 實現的注意事項。 本文將推導對稱 FIR 濾波器的模塊化流水線結構。我們將看到派生結構可以使用? Xilinx

2023-05-26 01:20:02 228

228

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的并行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了復現以及解讀,并進行了仿真驗證。

2023-05-24 10:57:36 331

331

本文介紹了設計濾波器的FPGA實現步驟,并結合杜勇老師的書籍中的串行FIR濾波器部分進行一步步實現硬件設計,對書中的架構做了簡單的優化,并進行了仿真驗證。

2023-05-24 10:56:34 343

343

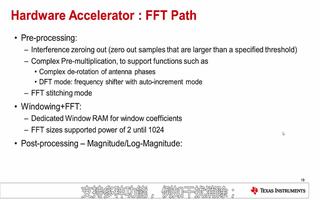

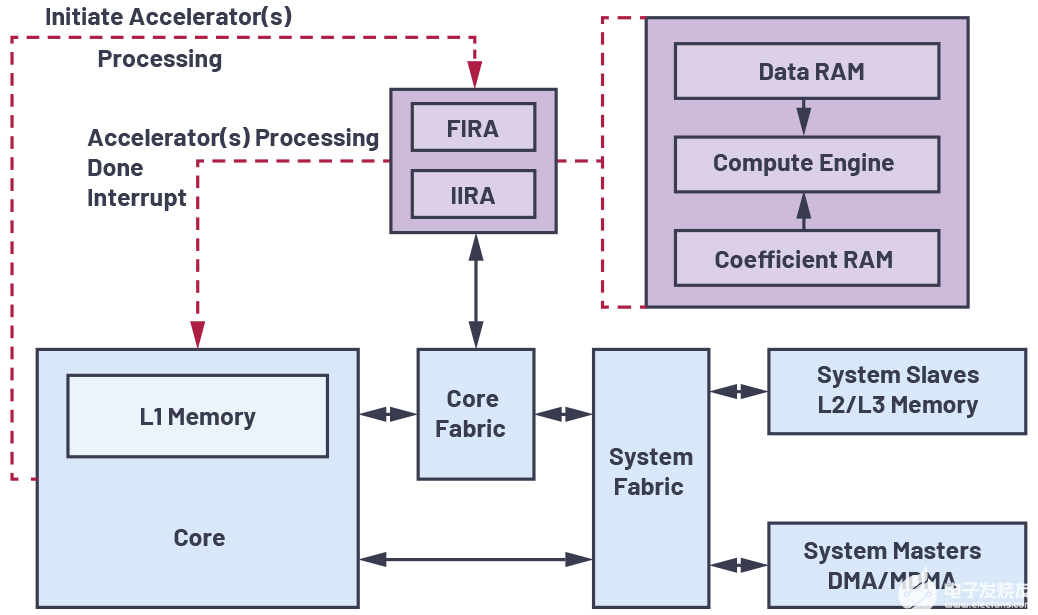

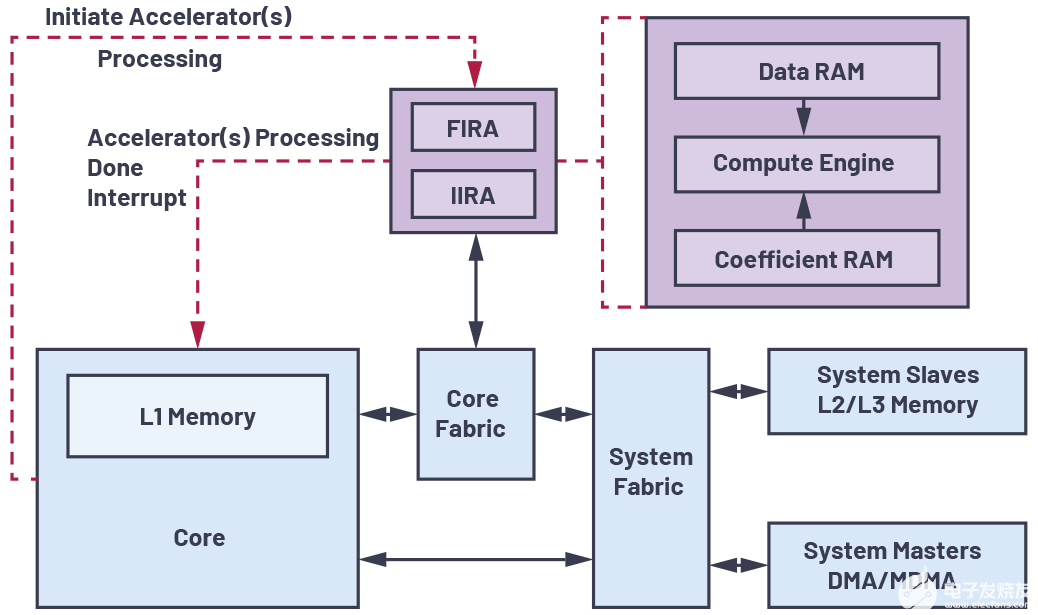

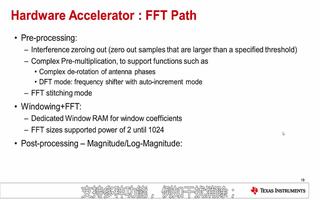

SHARC ADSP-2146x處理器集成了硬件加速器,可實現三種廣泛使用的信號處理操作:FIR(有限脈沖響應)、IIR(無限脈沖響應)和FFT(快速傅里葉變換)。加速器卸載了核心處理器,并有可能使處理器的計算吞吐量增加一倍以上。本文以加速器在下一代音頻系統中的應用為例。?

2023-03-03 14:46:51 458

458

借助硬件加速器開發您的設計

2023-01-03 09:45:15 384

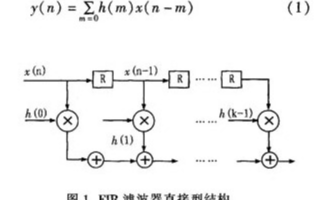

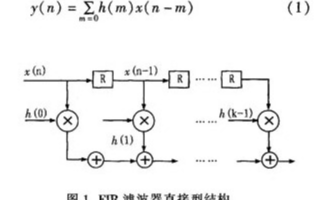

384 1.根據沖激響應的不同,將數字濾波器分為有限沖激響應(FIR)濾波器和無限沖激響應(IIR)濾波器。對于FIR濾波器,沖激響應在有限時間內衰減為零,其輸出僅取決于當前和過去的輸入信號值。對于IIR

2022-12-30 23:45:05 1347

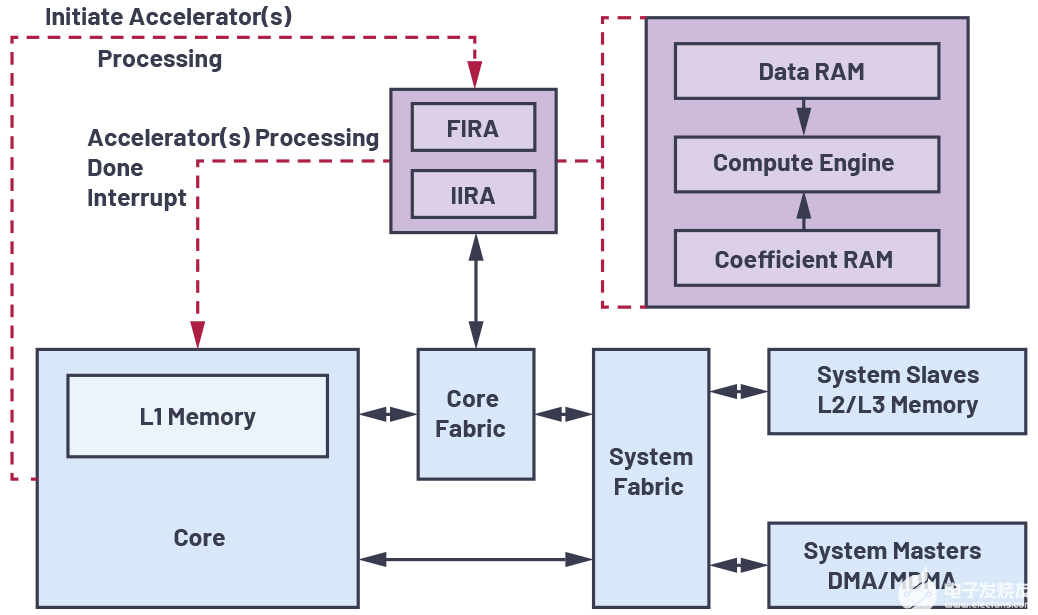

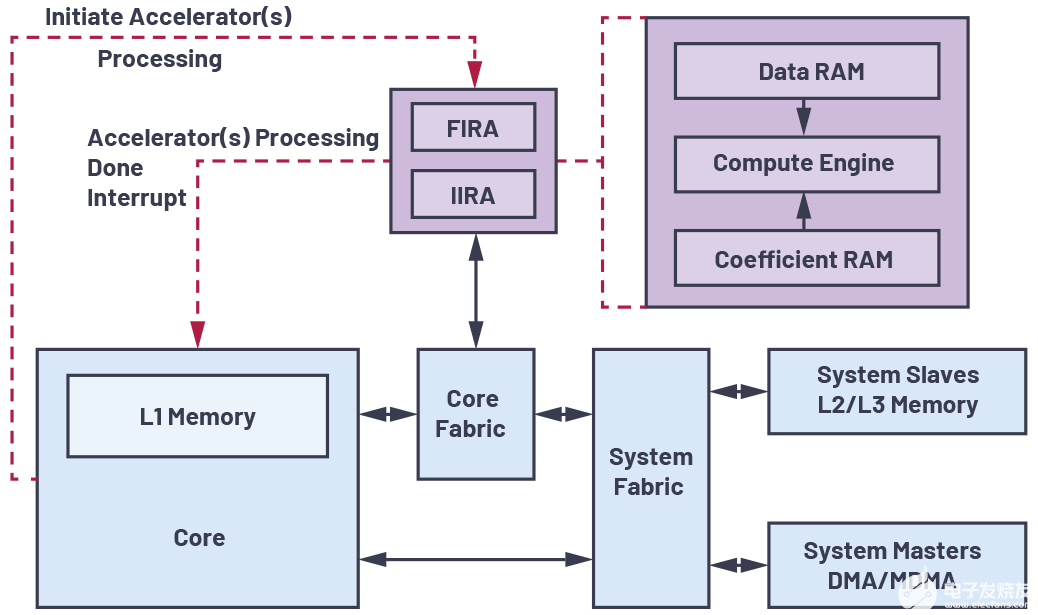

1347 處理器上的片上FIR和IIR硬件加速器(也稱為FIRA和IIRA)可用于卸載FIR和IIR處理任務,從而騰出內核用于其他處理。在本文中,我們將討論如何借助經過測試的實時示例說明的不同使用模型在實踐中使用這些加速器。

2022-12-20 11:39:25 535

535

處理器上的片上FIR和IIR硬件加速器(也稱為FIRA和IIRA)可用于卸載FIR和IIR處理任務,從而騰出內核用于其他處理。在本文中,我們將討論如何借助經過測試的實時示例說明的不同使用模型在實踐中使用這些加速器。

2022-12-20 11:22:36 575

575

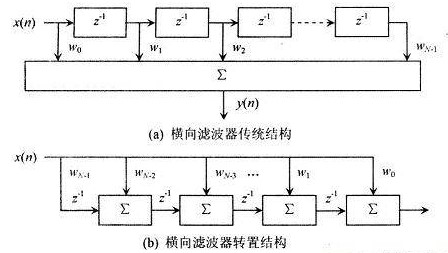

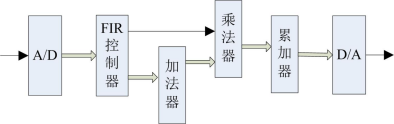

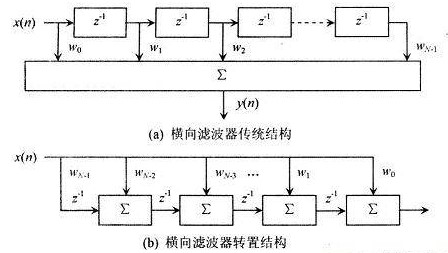

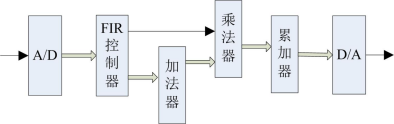

和移位操作。這些結構需要占用器件較多的LE(邏輯元件)資源,設計周期長,工作頻率低,實時性差。本文提出一種基于Stratix系列FPGA器件的新的實時高速脈動FIR濾波器的快速實現方法。利 用FGPA集成的DSP(數字信號處理器)乘加模塊定制卷積運算單元,利用VHDL(甚高速集成電路硬件描述

2022-12-01 10:20:05 482

482 當 AI 設計人員將硬件加速器整合到用于訓練和推理應用的定制芯片中時,應考慮以下四個因素

2022-08-19 11:35:55 1125

1125

數字濾波器從實現結構上劃分,有FIR和IIR兩種。FIR的特點是:線性相位、消耗資源多;IIR的特點是:非線性相位、消耗資源少。由于FIR系統的線性相位特點,設計中絕大多數情況都采用FIR濾波器。

2022-04-24 14:40:16 2166

2166 OpenHarmony Dev-Board-SIG專場:OpenHarmony 新硬件加速器

2021-12-28 15:12:30 969

969

硬件加速器提升下一代SHARC處理器的性能

2021-04-23 13:06:32 6

6 提出一種新的高階FIR濾波器的FPGA實現方法。該方法運用多相分解結構對高階FIR濾波器進行降階處理,采用改進的分布式算法來實現降階后的FIR濾波器。設計了一系列階數從8到1 024的FIR濾波器

2021-03-23 15:44:54 30

30 倍,其中L為并行的路數,并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經典符號數表示以及優化定點濾波器系數,并針對濾波器系數設計了流水線結構。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 13

13 倍,其中L為并行的路數,并且運算延遲小。首先從理論上分析了基于多相濾波器的并行濾波原理,并以八路并行為例,對FIR濾波運算做了浮點仿真驗證。然后用經典符號數表示以及優化定點濾波器系數,并針對濾波器系數設計了流水線結構。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2020-09-25 10:44:00 3

3 必要在性能和實現復雜性之間做出選擇,也就是選擇不同的濾波器實現結構。這里運用并行流水線結構來實現速度和硬件面積之間的互換和折衷。

2020-03-04 09:22:01 2800

2800

2.6 mmWave波形傳感器簡介1443硬件加速器

2019-05-08 06:20:00 2598

2598

。常系數FIR濾波器的系數固定不變,可根據其特點采用分布式算法進行設計,故實現起來速度快,消耗的資源少。變系數FIR濾波器的系數是不斷變化的。當前含有變系數FIR濾波環節的芯片普遍存在速度與處理級數的矛盾,有效解決此問題具有重要的現實意義。

2019-04-22 08:07:00 4654

4654

本教程討論基于Xilinx FPGA的Memcached硬件加速器的技術細節,該硬件加速器可為10G以太網端口提供線速Memcached服務。

2018-11-27 06:41:00 3259

3259 在數字信號處理中,數字濾波器的應用是極其廣泛和重要的單元。與模擬濾波器相比,數字濾波器可以克服模擬濾波器所無法克服的電壓漂移,溫度漂移以及噪聲等問題。數字濾波器根據沖擊響應函數的特性,可以分為IIR濾波器和FIR濾波器兩種。由于FIR濾波器只有零點、系統穩定等諸多優點。

2018-07-20 14:32:00 4898

4898

用FPGA實現抽取濾波器比較復雜,主要是因為在FPGA中缺乏實現乘法運算的有效結構,現在,FPGA中集成了硬件乘法器,使FPGA在數字信號處理方面有了長足的進步。本文介紹了一種采用Xilinx公司的XC2V1000實現FIR抽取濾波器的設計方法。

2018-04-28 11:50:00 980

980

文介紹了FIR抽取濾波器的工作原理,重點闡述了用XC2V1000實現FIR抽取濾波器的方法,并給出了仿真波形和設計特點。

2018-04-19 11:34:00 1701

1701

很多人認為硬件加速器無非是一種速度更快的仿真器而已。毫無疑問,由于硬件加速器使用物理硬件進行仿真,使用硬件加速器驗證復雜的集成電路和大型片上系統(SoC)能比軟件仿真器快若干數量級。與仿真用通用計算機相比,仿真用單一功能計算機能提供更高容量、更高效的系統。

2018-03-28 14:50:00 3018

3018

設計時鐘的速度運行相關設計。硬件加速器的運行速度則是每秒lM左右個時鐘,因此可以將原始性能提高1000倍。原始性能相當于硬件加速器在無需等待驗證平臺或外部事件的條件下自由運行時的性能。 驗證平臺對硬件加速性能影響很大。

2018-03-05 10:13:13 3

3 本文針對快速、準確選擇參數符合項目要求的濾波器設計方法的目的,通過系統的介紹有限脈沖響應( Finite Impulse Response,FIR)濾波器的原理、結構形式以及幾種FIR濾波器設計方法

2017-12-21 14:53:14 14

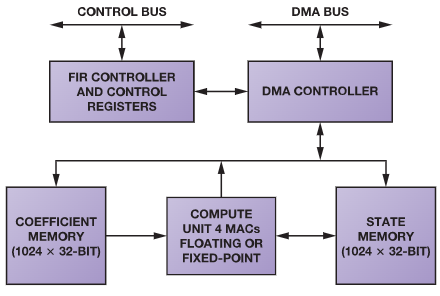

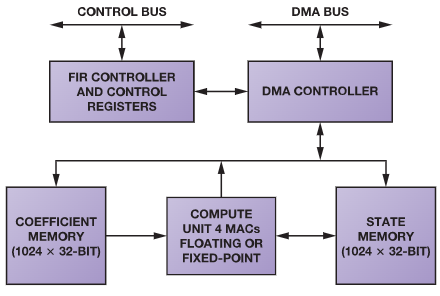

14 超過兩倍。本文以下一代音頻系統為例,說明硬件加速器在這方面的應用。 為什么使用硬件加速器 FIR濾波器、IIR濾波器和FFT操作在數字信號處理器中應用十分普遍,且具有規則的結構,因此可以用硬件直接實現,特別是用硬件加速器。硬件加速器是專用

2017-12-04 15:22:36 913

913 線性相位FIR濾波器的對稱性減小了硬件規模;利用分割查找表的方法減小了存儲空間;采用并行分布式算法結構和流水線技術提高了濾波器的速度,在FPGA上實現了該濾波器。

2017-11-24 15:17:27 2799

2799 針對傳統的FIR 濾波器的缺點,介紹了一種基于FPGA 乘法器的FIR 濾波器設計方法,該濾波器利用FPGA 自帶的18位乘法器MULT18 × 18SIO 進行乘法計算,利用寄存器對相乘結果進行

2017-11-22 07:39:45 2378

2378

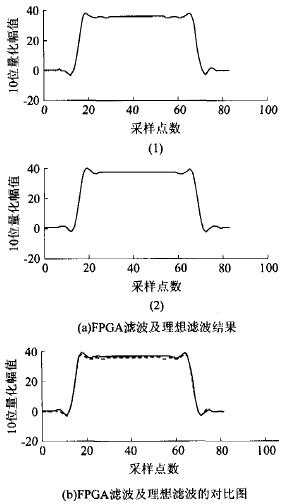

研究了一種采用FPGA實現32階FIR濾波器硬件電路方案;討論了窗函數的選擇、濾波器的結構以及系數量化問題;研究了FIR濾波器的FPGA實現,各模塊的設計以及如何優化硬件資源,提高運行速度等

2017-11-10 16:41:57 15

15 基于MATLAB與QUARTUS+II的FIR濾波器設計與驗證

2017-09-18 10:17:37 11

11 數字濾波器廣泛應用于硬件電路設計,在離散系統中尤為常見,一般可以分為FIR濾波器和IIR濾波器,那么他們有什么區別和聯系呢。

2017-05-04 15:52:17 5712

5712

數字濾波器廣泛應用于硬件電路設計,一般分為FIR濾波器和IIR濾波器。那么FIR濾波器和IIR濾波器有什么區別呢?本文通過幾個例子做一個簡單的總結。

2017-05-03 11:36:31 18

18 FIR濾波器,即有限脈沖響應濾波器,顧名思義,是指單位脈沖響應的長度是有限的濾波器。而根據FIR濾波器的結構形式,分為直接型、級聯型、頻率取樣型和快速卷積型。其中直接型又可以采用串行結構、并行結構、分布式結構。本案例實現了具有線性相位的半串行結構的FIR濾波器。

2017-04-20 14:42:14 2095

2095 基于FPGA實現變采樣率FIR濾波器的研究

2017-01-08 15:59:09 19

19 基于位并行DA結構的高速FIR濾波器_周云

2017-01-07 21:39:44 2

2 基于FPGA的FIR濾波器設計與實現,下來看看

2016-05-10 11:49:02 38

38 基于matlab和fpga的FIR濾波器設計,有興趣的同學可以下載學習

2016-04-27 15:51:58 55

55 本文簡要介紹了FIR數字濾波器的結構特點和基本原理,提出基于FPGA和DSP Builder的FIR數字濾波器的基本設計流程和實現方案。##FIR 數字濾波器的詳細設計。

2014-07-24 15:30:05 8207

8207

FIR 濾波器廣泛應用于數字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##脈動型(Systolic)FIR濾波器設計

2014-06-30 09:47:40 1723

1723 FIR 濾波器廣泛應用于數字信號處理中,主要功能就是將不感興趣的信號濾除,留下有用信號。##全并行FIR濾波器結構

2014-06-27 10:02:56 7800

7800 在數字濾波器中,FIR濾波器是一種結構簡單且總是穩定的濾波器,同時也只有FIR濾波器擁有線性相位的特性。傳統的直接型濾波器運算速度過慢,而改進型的DA結構的濾波器需要過高的

2013-08-07 19:04:56 36

36 描述了基于FPGA的FIR濾波器設計。根據FIR的原理及嚴格線性相位濾波器具有偶對稱的性質給出了FIR濾波器的4種結構,即直接乘加結構、乘法器復用結構、乘累加結構、DA算法。在本文中給

2012-11-09 17:32:37 121

121 數字濾波器是數字信號處理領域內的重要組成部分。FIR濾波器又以其嚴格的線性相位及穩定性高等特性被廣泛應用。本文結合MATLAB工具軟件介紹了FIR數字濾波器的設計方法,并在Xilinx的

2012-09-25 11:34:08 120

120 針對復雜算法中矩陣運算量大, 計算復雜, 耗時多, 制約算法在線計算性能的問題, 從硬件實現角度, 研究基于FPGA/Nios-Ⅱ的矩陣運算硬件加速器設計, 實現矩陣并行計算。首先根據矩陣運算

2011-12-06 17:30:41 89

89 目前數字濾波器的硬件實現方法通常采用專用DSP芯片或FPGA,本文從FIR濾波器的系數考慮,采用CSD編碼,對FIR數字濾波器進行優化設計。

2011-08-16 10:54:41 3448

3448

充分利用有限沖擊響應數字濾波器(Finite Impulse Response digital filter ,FIR)系數的對稱特性,借助于MATLAB語言和現場可編程門陣列(FPGA)實現了一種高效的 低通濾波器 。設計過程中通過

2011-08-05 14:23:07 82

82 基于流水線技術,利用FPGA進行并行可重復配置高精度的 FIR濾波器 設計。使用VHDL可以很方便地改變濾波器的系數和階數。在DSP中采用這種FIR濾波器的設計方法可以充分發揮FPGA的優勢。

2011-07-18 17:09:28 63

63 本文通過改變通常FIR處理結構,有效地節省了資源,只使用了一套乘加器,一套FIR濾波器結構,就完成了兩套FIR濾波器的功能,

2011-05-13 09:32:32 4050

4050

分析了FIR數字濾波器的基本原理,在MATLAB環境下利用窗函數設計FIR低通濾波器,實現了FIR低通濾波器的設計仿真。將設計的符合要求的濾波器在TI公司DSPTMS320LF2407A上實現。通過

2009-12-18 15:53:56 101

101 :FIR 數字濾波器由于具有諸多優點,因而在數字信號處理中得到了十分廣泛的應用。介紹了MATLAB 環境下FIR 數字濾波器的設計、仿真和基于TMS320VC5416DSP 硬件平臺的實現。詳細描述

2009-12-16 13:31:22 58

58 基于MATLAB與QUARTUS II的FIR濾波器設計與驗證

1 引言 FIR數字濾波器能夠滿足濾波器對幅度和相位特性的嚴格要求,避免模擬濾波器的溫漂和噪聲等問題,

2009-12-12 11:23:42 2317

2317

本文綜合介紹了基于FPGA 軟件Quartus II 和MATLAB 的FIR 濾波器的設計仿真,將兩大軟件綜合運用后大大縮減了設計研發的時間,在算法結構上利用了流水線等優化方式。

2009-11-30 14:21:09 117

117 FIR帶通濾波器的FPGA實現

引 言??? 在FPGA應用中,比較廣泛而基礎的就是數字濾波器。根據其單位沖激響應函數的時域特性可分為無限沖擊響應(Infinite

2009-11-13 09:55:18 6439

6439

基于FPGA對稱型FIR濾波器的設計與實現:在基于FPGA的對稱型FIR數字濾波器設計中,為了提高速度和運行效率,提出了使用線性I相位結構和加法樹乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 本文提出了一種采用現場可編程門陣列器件 FPGA 實現FIR 字濾波器硬件電路的方案,該方案基于只讀存儲器ROM 查找表的分布式算法。并以一個十六階低通FIR 數字濾波電路在ALTERA 公

2009-08-31 16:47:47 44

44 摘要: 針對在FPGA中實現FIR濾波器的關鍵--乘法運算的高效實現進行了研究,給了了將乘法化為查表的DA算法,并采用這一算法設計了FIR濾波器。通過FPGA仿零點驗證

2009-06-20 14:09:36 646

646

摘要: 提出了一種采用現場可編碼門陣列器件(FPGA)并利用窗函數法實現線性FIR數字濾波器的設計方案,并以一個十六階低通FIR數字濾波器電路的實現

2009-06-20 14:05:46 952

952

如何用用FPGA實現FIR濾波器

你接到要求用FPGA實現FIR濾波器的任務時,也許會想起在學校里所學的FIR基礎知識,但是下一步該做什么呢?哪些參數是重

2009-03-30 12:25:45 4408

4408

基于流水線技術的并行高效FIR濾波器設計

基于流水線技術,利用FPGA進行并行可重復配置高精度的FIR濾波器設計。使用VHDL可以很方便地改變濾波器的系數和階數。在DSP中采用

2009-03-28 15:12:27 714

714

高效FIR濾波器的設計與仿真-基于FPGA

摘要:該文在介紹有限沖激響應(FIR)數字濾波器理論及常見實現方法的基礎上,提出了一種基于FPGA的高效實現方案。

2008-01-16 09:56:02 1373

1373

電子發燒友App

電子發燒友App

評論