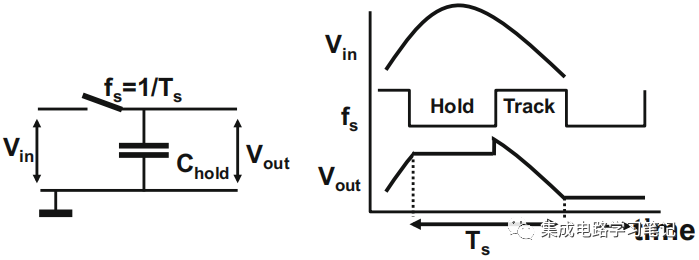

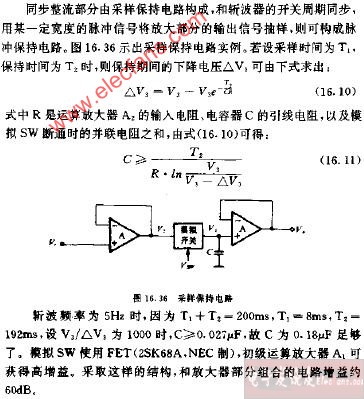

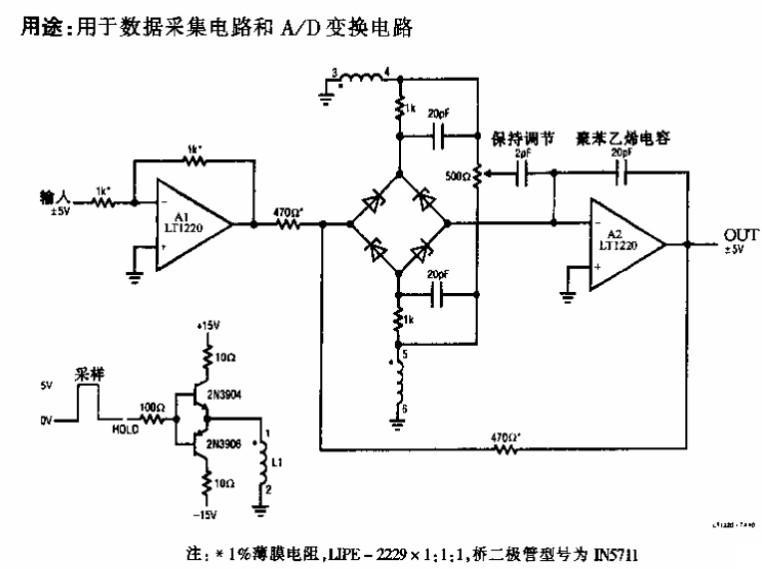

采樣保持電路原理

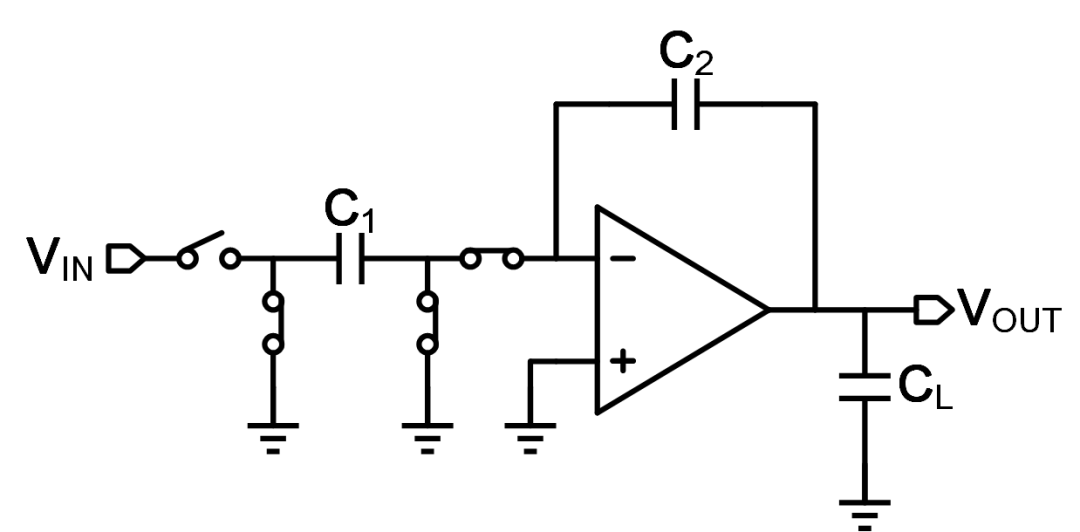

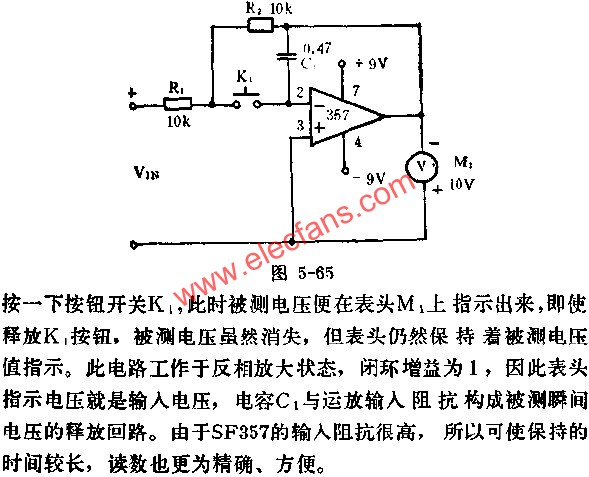

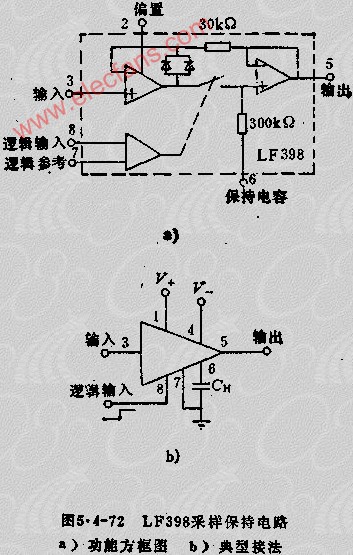

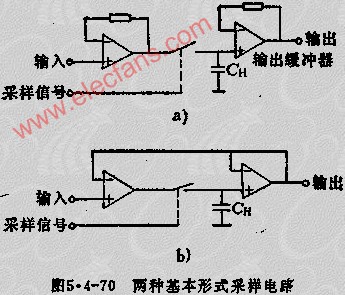

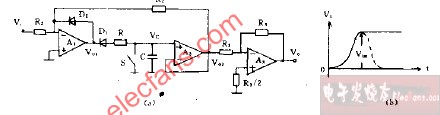

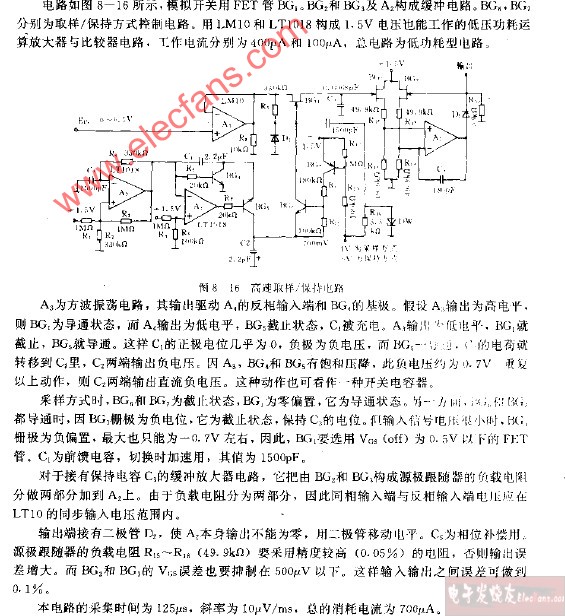

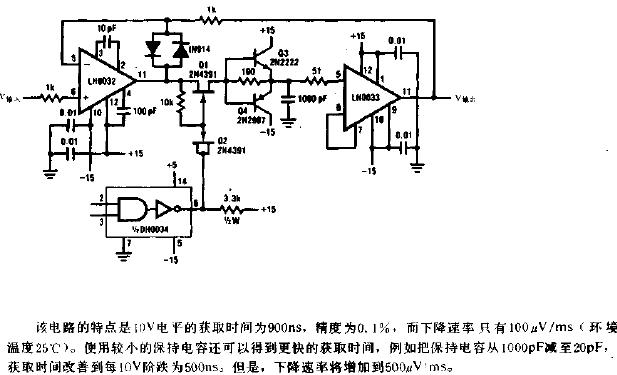

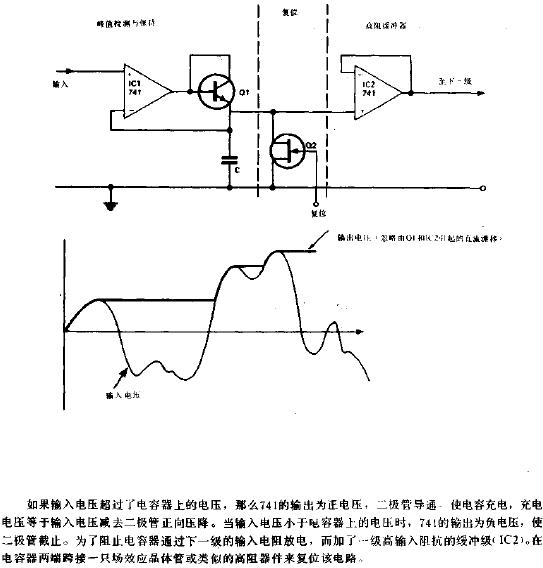

采樣保持電路能夠跟蹤或者保持輸入模擬信號的電平值。在理想狀況下,當處于采樣狀態時,采樣保持電路的輸出信號跟隨輸入信號變化而變化;當處于保持狀態時,采樣保持電路的輸出信號保持為接到保持命令的瞬間的輸入信號電平值。當電路處于采樣狀態時開關導通,這時電容充電,如果電容值很小,電容可以在很短的時間內完成充放電,這時,輸出端輸出信號跟隨輸入信號的變化而變化;當電路處于保持狀態時開關斷開,這是由于開關斷開,以及集成運放的輸入端呈高阻狀態,電容放電緩慢,由于電容一端接由集成運放構成的信號跟隨電路,所以輸出信號基本保持為斷開瞬間的信號電平值。

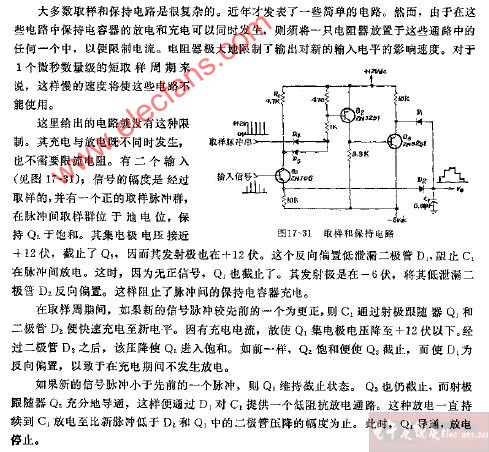

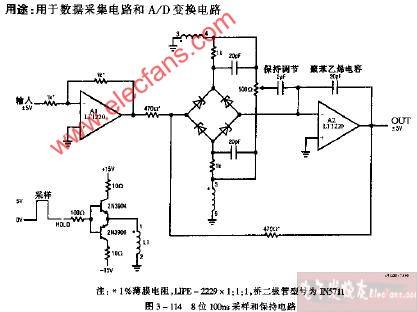

采樣保持電路圖設計(一)

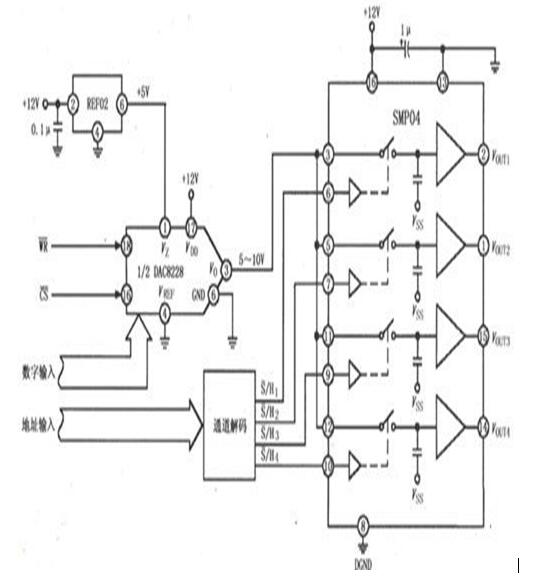

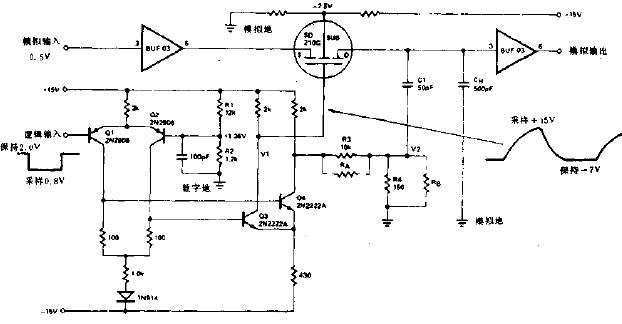

采樣保持放大器SMP04用做多路輸出選擇器電路圖。

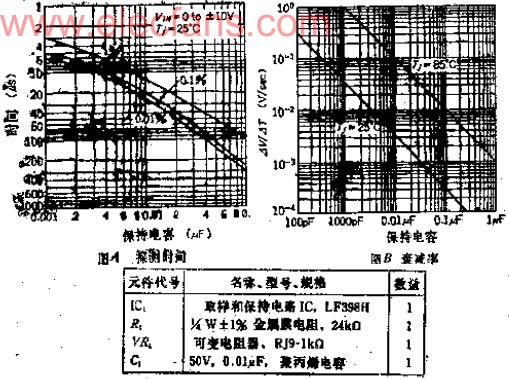

如圖所示為SMP04用做多路輸出選擇器,與解碼器、D/A轉換器構成的四路數字-模擬轉換電路。數字信號輸入模數轉換器DAC8228,輸出產生5~10V模擬電壓送副SMP04,地址輸入通道解碼器,不同的地址解碼后分別控制四路開關,以分別輸出四模擬信號。采用DAC8228產生DAC電壓輸出可以使電路得以最大的簡化。為了將輸出電壓干擾減小到最小,在采樣信號被確認之前,必須保證有5μs的最后電壓建立時間。每一個采樣保持放大器必須在每一秒鐘或更低時問刷新一次,以確保輸出電壓下降率不超過10mV或1/2LSB(最小有效位)。

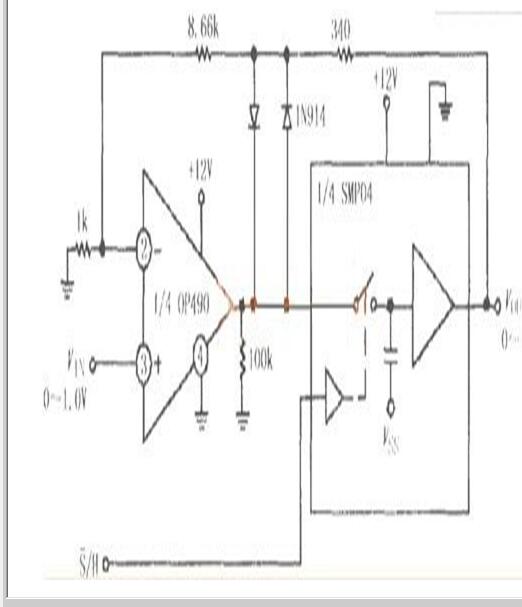

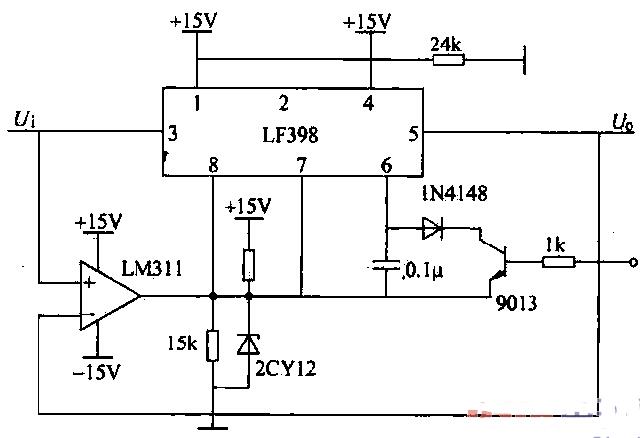

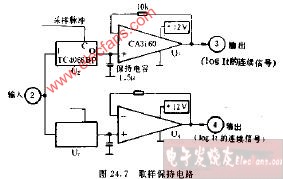

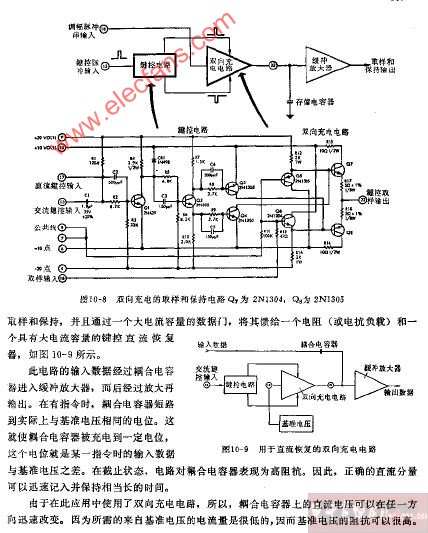

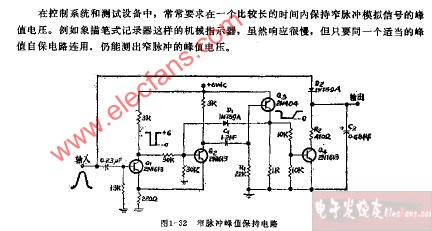

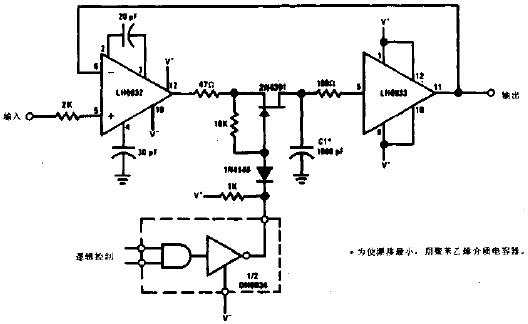

采樣保持電路圖設計(二)

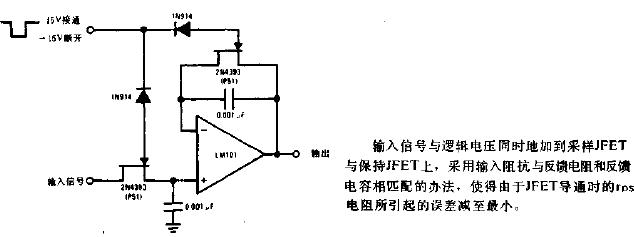

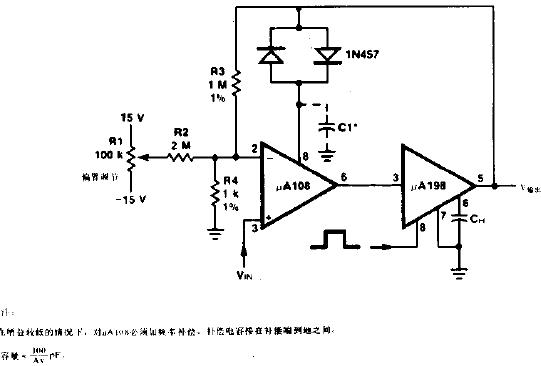

如圖所示為由SMP04與運放構成的增益為10的采樣保持放大電路。電路中將SMP04置于運放OP490的反饋回路中,當S非/H=0時,SMP04內部開關閉合,運放OP490的反饋回路接通,電路增益由運放本身及反饋電阻決定,圖中增益設置為10,輸出端輸出放大后的采樣電壓。當S非/H=1時,SMP04內部開關斷開,運放OP490反饋回路也無法形成,輸出端輸出保持在內部保持電容上最近一次的采樣電壓,且不受輸入端信號影響。運放輸出端的兩個二極管1N914起鉗位作用,防止當SMP04保持狀態時造成運放飽和。

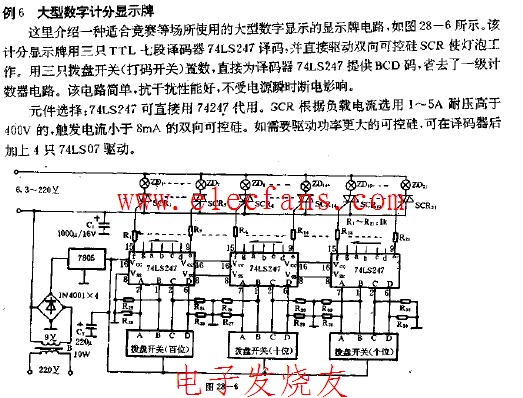

電子發燒友App

電子發燒友App

評論