0 引言

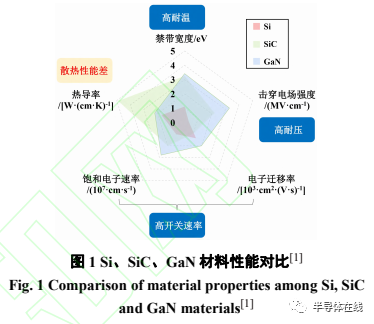

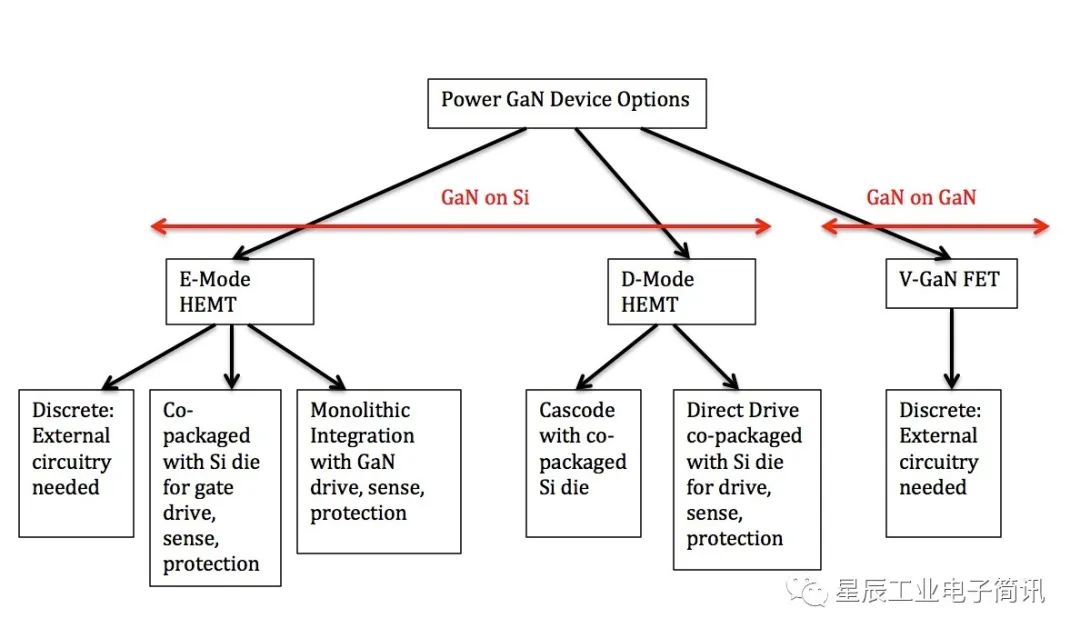

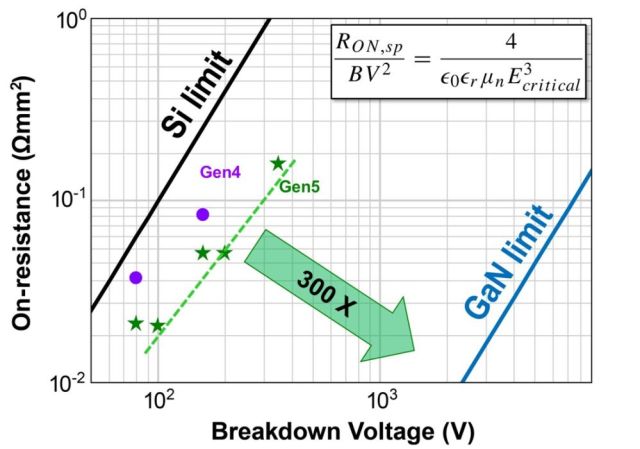

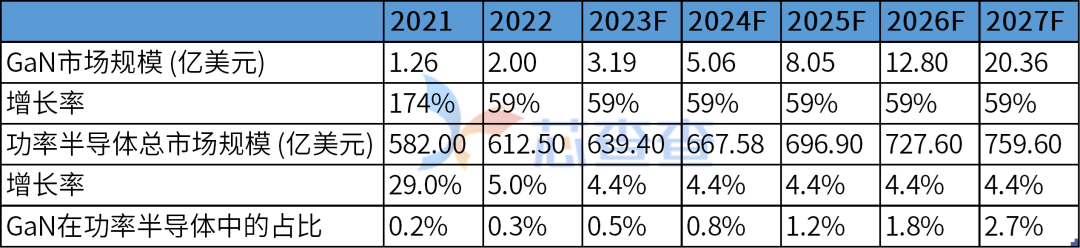

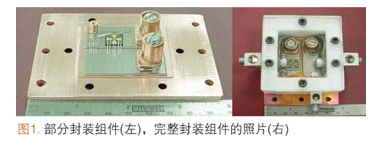

近年來,電動汽車、高鐵和航空航天領(lǐng)域不斷發(fā)展,對功率器件/模塊在高頻、高溫和高壓下工作的需求不斷增加。傳統(tǒng)的 Si 基功率器件/模塊達到其自身的材料性能極限,氮化鎵(GaN)作為第三代寬禁帶半導(dǎo)體材料具有高耐溫、高耐壓及高開關(guān)速率的優(yōu)點逐漸成為研究熱點。圖 1所示是三代半導(dǎo)體材料性能對比圖。然而封裝技術(shù)為充分發(fā)揮 GaN 的材料優(yōu)勢帶來了挑戰(zhàn)。

首先,GaN 器件的開關(guān)速度極高,如果使用傳統(tǒng)引線鍵合封裝型式會帶來較大的封裝雜散電感,繼而產(chǎn)生顯著的開關(guān)損耗、電壓過沖等問題。這無法滿足 GaN 器件的高頻應(yīng)用需求。為此,國內(nèi)如北京工業(yè)大學(xué)(Beijing University of Technology, China),國外如韓國電子通信研究院 (Electronic Technology Research Institute, Korean)、美國弗吉尼亞理工大學(xué)(Virginia Tech, USA)等高校和研究機構(gòu)相繼提出了調(diào)整引線級聯(lián)的方式降低雜散電感的研究思路,但效果有限。隨后為進一步解決這一突出難題,美國弗吉尼亞理工大學(xué)、德國埃爾朗根-紐約堡大學(xué)(Erlangen Nurnberg University, German)和韓國漢陽大學(xué)(Hanyang University, Korean)等相繼提出了二維平面型無引線封裝型式。為進一步縮短電流環(huán)路面積,德國弗勞恩霍夫可靠性與微集成研 究 所 (Fraunhofer Institute for Reliability and Microintegration IZM, German)、美國東哈特福德聯(lián)合技術(shù)研究中心(Systems Department United Technologies Research Center East Hartford, USA)、 丹 麥 奧 爾 堡 大 學(xué) (Aalborg University, Denmark)和美國弗吉尼亞理工大學(xué)等進一步探索了三維集成型無引線封裝型式。此外,美國弗 吉尼亞 理工大 學(xué) 、美 國 EPC(Efficient Power Conversion)公司、韓國漢陽大學(xué)等公司和高校基于磁相消設(shè)計的理念提出降低雜散電感的優(yōu)化方案。

其次,隨著 GaN 功率器件/模塊朝著高功率密度化、高集成化方向發(fā)展,其熱流密度越來越大。而且加之 GaN 材料本身熱導(dǎo)率低,由此引發(fā)的封裝引線熱燒損和 GaN 芯片熱擊穿等問題突出。因此,GaN 功率器件/模塊封裝需要具備快速、高效散熱能力。欲加入三代半交流群,加微信:tuoke08。國內(nèi)如西安交通大學(xué)(Xi’an Jiaotong University, China),國外如法國巴 黎 第 十 一 大 學(xué) (University Paris-Sud, France)、 美 國 威 斯 康 星 大 學(xué) 麥 迪 遜 分 校(University of Wisconsin-Madison, USA)、德國英飛凌公司(Infineon, German)等高校和公司分別對傳統(tǒng)遠結(jié)被動冷卻封裝形式改進設(shè)計優(yōu)化GaN 功率器件/模塊的散熱,但是依然不能滿足其更高熱流密度的工作需求。為此,美國休斯研究室(Hughes Research Laboratories, USA)和德國弗勞恩霍夫可靠性與微集成研究所相繼提出以扇出式晶圓級封裝結(jié)構(gòu)為主的近結(jié)被動冷卻封裝形式,已經(jīng)引起廣泛的關(guān)注。此外,日本松下電氣公司(Panasonic, Japan)和美國洛克希德·馬丁任務(wù)系統(tǒng)與訓(xùn)練分公司(Lockheed Martin Mission System and Training, USA)還提出將散熱系統(tǒng)與 GaN 功率器件集成的改良型近結(jié)主動冷卻封裝形式,散熱效率大幅提升。

最后,芯片封裝互連材料是保證 GaN 功率器件/模塊高溫下可靠使用的關(guān)鍵。然而功率器件/模塊中常用的釬料合金在高溫工作條件下存在抗蠕變疲勞性能和抗機械疲勞性能差等問題。為了解決這些問題,德國弗萊堡大學(xué)(UniversityFreiburg, German)講錫銀合金的瞬時液相連接應(yīng)用在 GaN 芯片封裝中,并獲得高連接質(zhì)量的接頭,但是工藝復(fù)雜,成本高。近年來,低溫?zé)Y(jié)銀互連由于具有低燒結(jié)工藝溫度、高允許工作溫度的優(yōu)勢而被廣泛關(guān)注。日本大阪大學(xué)(Osaka University, Japan)將燒結(jié)銀作為連接材料,應(yīng)用在 GaN 芯片的封裝中,并分別針對芯片連接層結(jié)構(gòu)和基板表面鍍層做了相關(guān)研究。

綜上,本文以 GaN 芯片的封裝技術(shù)為核心,基于現(xiàn)有文獻資料,總結(jié)分析 GaN 功率器件/模塊在雜散電感、散熱設(shè)計以及可靠性方面遇到的問題及解決方案,同時分析并指出未來GaN 功率器件/模塊封裝技術(shù)的熱點研究方向。期望通過提出該領(lǐng)域亟待解決的問題以及研究展望,為今后研究提供思路。

1 GaN 基功率器件/模塊封裝需求

雖然 GaN 基功率器件/模塊的封裝研究剛起步,但 Si 基、SiC 基功率器件/模塊的封裝研究趨于成熟。三者之間存在顯著差異,亦有相互借鑒之處。

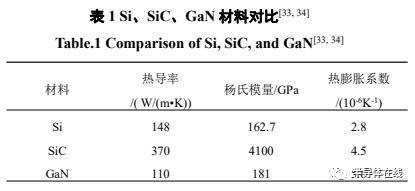

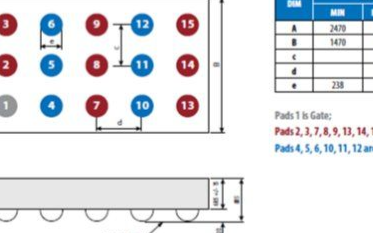

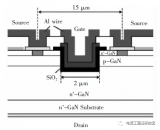

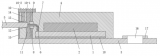

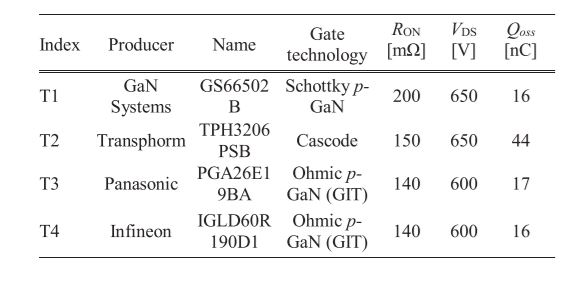

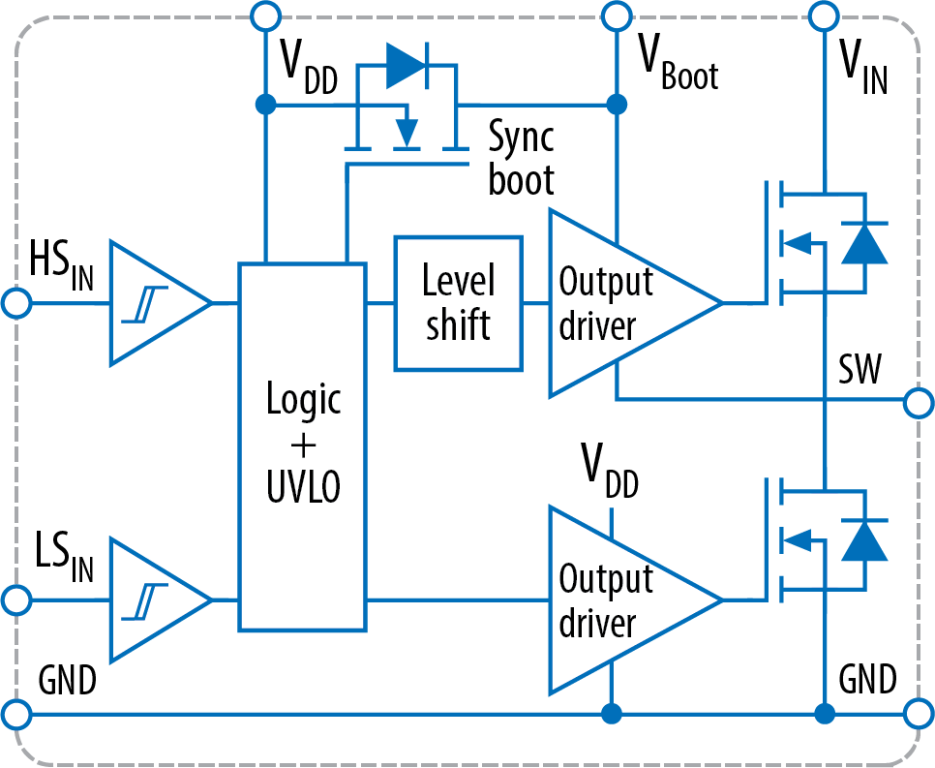

首先在減小封裝雜散電感方面,SiC 和 GaN基功率器件/模塊相比于 Si 基,其開關(guān)速度更快,同時伴隨著更高的 dv/dt 和 di/dt。此外,兩者的開關(guān)頻率也更高。因此,SiC 和 GaN 更易產(chǎn)生電壓過沖和電磁干擾等問題。以 GaN 器件為例,其 dv/dt 一般可以超過 100V/ns。例如,2016 年,美國弗吉尼亞理工大學(xué)制作的無引線封裝 Cascode GaN HEMT 器件具有極高的開關(guān)速度,關(guān)斷時的 dv/dt 和 di/dt 分別可達 100V/ns和 3A/ns。由于該器件是分立 GaN 器件,其開關(guān)速度依然有提升的潛力。2021 年,美國紐約州立大學(xué)石溪分校(The State University of NewYork at Stony Brook, USA)將柵極驅(qū)動集成到模塊中去,縮短驅(qū)動環(huán)路和功率環(huán)路,進一步提高開關(guān)速度。該成果是目前開關(guān)速度最快的 GaN功率模塊:關(guān)斷時間小于 15ns,關(guān)斷時 dv/dt 達192V/ns,電壓過沖僅為 58V,低于直流母線電壓的 15%。引線鍵合封裝型式雖然可以滿足 Si基器件/模塊的使用要求,但不能滿足 SiC 基和GaN 基器件/模塊。而且,在 Cascode GaNHEMT 中,由于涉及到 GaN HEMT 與 MOSFET的級聯(lián),雜散電感會更大。因此,GaN 基功率器件/模塊對低雜散電感封裝需求更加迫切。其次在封裝散熱管理方面,GaN 材料熱導(dǎo)率在三者之中最低,而且同功率等級下 GaN 器件的面積往往更小。雖然當(dāng)前 GaN 功率器件/模塊的功率等級低于 SiC 基功率器件/模塊,但為降低封裝雜散電感,GaN 功率器件/模塊通常要求將其驅(qū)動電路部分甚至完全與 GaN 功率器件/模塊一體化集成,并且隨著 GaN 功率器件/模塊不斷發(fā)展,功率等級不斷提升,因此其熱流密度非常高。而且加之目前 GaN 芯片多為平面型結(jié)構(gòu),其散熱形式主要為單面散熱,散熱效率低,當(dāng)前封裝無法滿足高熱流密度下快速、高效的散熱要求。因此,不難看出 GaN 功率器件/模塊對快速、高效封裝散熱技術(shù)的需求甚至要高于 SiC 基功率器件/模塊。此外,商用的 GaN 芯片在使用過程中通常將源極與芯片襯底相連,以降低動態(tài)導(dǎo)通電阻,獲得最好的電性能。因此,在多芯片功率模塊的散熱設(shè)計中,既要保證 GaN 芯片位置合理分布而減小芯片間溫差,又要保證基板的線路布局合理降低阻抗,這不同于垂直型Si 基和 SiC 基 MOSFET 器件。最后在封裝可靠性方面,雖然 GaN 芯片與封裝互連材料間的熱膨脹系數(shù)(CTE)失配相比于 Si 和 SiC 芯片更小,且 GaN 芯片彈性模量比 SiC 低,與 Si 近似,相對不易產(chǎn)生封裝互連失效,但以往研究發(fā)現(xiàn)在功率循環(huán)和溫度循環(huán)等老化條件下,熱失配造成封裝互連失效問題依然嚴(yán)重。如表 1 所示為Si、SiC 和 GaN 熱導(dǎo)率、楊氏模量和熱膨脹系數(shù)的對比。這可能是由于 GaN 功率器件/模塊的高熱流密度帶來的大溫度梯度加劇了封裝連接層產(chǎn)生顯著的熱機械應(yīng)力和應(yīng)變,因此,針對GaN 功率器件/模塊的封裝可靠性研究仍然非常迫切。

2 封裝雜散電感

2.1 雜散電感的來源與影響

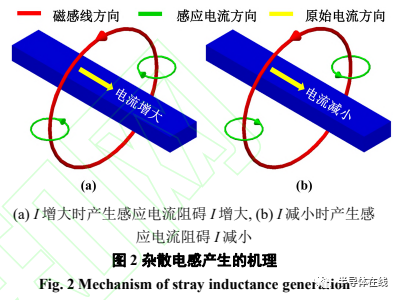

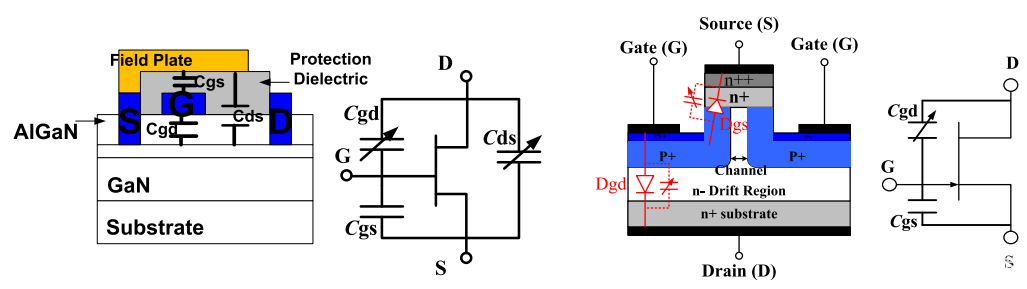

雜散電感是由于不同線路之間存在自感和互感現(xiàn)象而呈現(xiàn)出來的等效電感。如圖 2 所示,在閉合的電流環(huán)路中,變化的電流會產(chǎn)生感應(yīng)磁場,繼而產(chǎn)生感應(yīng)電動勢阻礙原始電流的變化,這就是自感現(xiàn)象。雜散電感是閉合環(huán)路的固有屬性,有電流通過的地方就有雜散電感,所以只能通過封裝技術(shù)將其減小而不能完全消除。

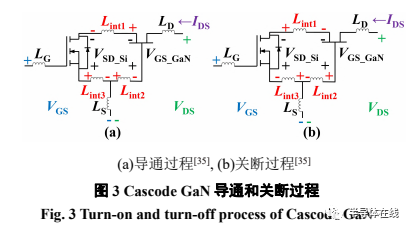

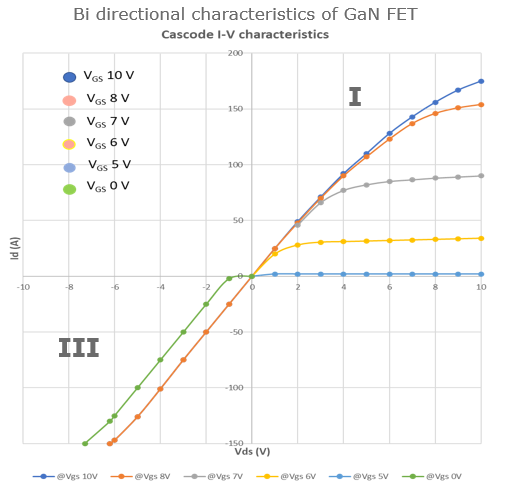

雜散電感對 GaN 功率器件/模塊產(chǎn)生的影響:降低開關(guān)速度,產(chǎn)生開關(guān)延時,增加開關(guān)損耗。此外,在關(guān)斷過程中會產(chǎn)生 VGS尖峰電壓導(dǎo)致誤觸發(fā)。以 Cascode GaN HEMT 的導(dǎo)通和關(guān)斷過程為例,分析雜散電感產(chǎn)生的影響。雜散電感使得 Cascode GaN HEMT 在導(dǎo)通過程中,產(chǎn)生導(dǎo)通延時,導(dǎo)通損耗增加。圖 3(a)是 CascodeGaN HEMT 電路導(dǎo)通過程示意圖。在 Cascode結(jié)構(gòu)中,D 型 GaN HEMT 由 MOSFET 驅(qū)動控制,MOSFET 導(dǎo)通,Cascode 結(jié)構(gòu)導(dǎo)通。隨著IDS的增大,雜散電感 Lint1和 Lint3會產(chǎn)生與 IDS方向相反的感應(yīng)電動勢,從而導(dǎo)致 VGS_GaN 的變化滯后于 VSD_Si。以 Cascode GaN HEMT 制作的降壓變化器為例,在 400V/4.5A 工作條件下導(dǎo)通時,雜散電感使導(dǎo)通時間從 3.5ns 增加到 7ns,導(dǎo)通損耗從 8W 增加到 16W。

雜散電感使 Cascode GaN HEMT 關(guān)斷過程中,產(chǎn)生 VGS尖峰電壓而導(dǎo)致誤觸發(fā)。圖 3(b)是Cascode GaN HEMT 電路關(guān)斷過程示意圖。隨著IDS的減小,雜散電感 Lint1和 Lint3會產(chǎn)生與 IDS方向相同的感應(yīng)電動勢。由基爾霍夫電壓定律得:

VGS_GaN=VSD_Si+VLint1+VLint2+VLint3 (1)

式中 VGS_GaN 是 GaN 的柵-源電壓,VSD_Si 是Si MOSFET 的源-漏電壓,VLint1、VLint2、VLint3分別是雜散電感產(chǎn)生的感應(yīng)電動勢。以 CascodeGaN HEMT 制作的降壓變化器為例,在 400V/12A 工作條件下關(guān)斷時,雖然 VSD_Si因為鉗位作用被限制-30V,但是 VGS_GaN 卻產(chǎn)生-5V 的尖峰電壓,不僅會造成誤觸發(fā),還有使柵極被擊穿的危險,影響 Cascode GaN HEMT 的可靠使用。因此,要通過合理的封裝方法減小雜散電感。

2.2 如何減小封裝雜散電感

2.2.1 調(diào)整引線級聯(lián)方式

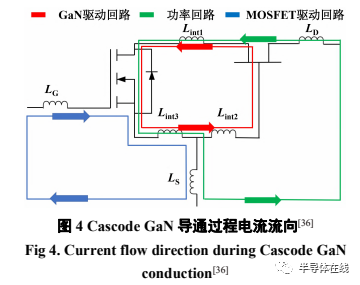

這種方法主要適用于Cascode GaN HEMT,因為其典型的級聯(lián)方式是使用引線將MOSFET的漏極、源極分別與D型GaN HEMT的源極、柵極連接。而E型GaN HEMT功率器件/模塊不涉及晶體管之間的級聯(lián),只有串聯(lián)或并聯(lián)的形式,所以無法進一步調(diào)整。在功率模塊的拓?fù)潆娐分校话銓⑼瑫r存在于功率環(huán)路和驅(qū)動環(huán)路的雜散電感定義為共源極電感(CSI),不同的共源電感對開關(guān)速度和開關(guān)過程損耗的影響程度是不同的。將共源極電感的概念應(yīng)用到Cascode GaN HEMT中同樣適用。以Cascode GaN HEMT 結(jié)構(gòu)的TO型封裝為例,圖4是其導(dǎo)通過程的電流流向。從MOSFET的角 度 看 , Lint3和 LS是 共 源 極 電 感 ;從D 型 GaN HEMT的角度看Lint3和Lint1是共源極電感。因此,從整個Cascode GaN HEMT結(jié)構(gòu)來看,Lint3同時是MOSFET和D型GaN HEMT的共源極電感,所以它的影響最大。其次是Lint2,因為它位于D型GaNHEMT的驅(qū)動環(huán)路中,會影響GaN HEMT的導(dǎo)通速度 。所 以共 源極 雜 散電 感的 影響 程 度依 次為Lint3?Lint1?LS。這就為我們提供了解決問題的思路:通過調(diào)整引線的連接方式,優(yōu)先并依次減小共源極電感Lint3、Lint1、LS。

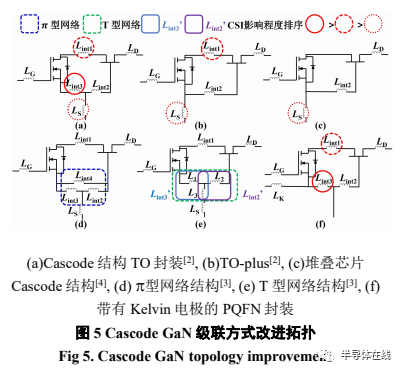

首先,應(yīng)考慮消除影響最大的共源電感Lint3。例如,2014年,北京工業(yè)大學(xué)通過改變Lint2的連接方式成功消除了共源電感 Lint3。如圖 5(a)所示,引線 Lint2的作用是連接 D 型 GaN HEMT 的柵極與 MOSFET 的源極,使 MOSFET 為 GaNHEMT 提供驅(qū)動電壓。如圖 5(b)所示,現(xiàn)將 D型 GaN HEMT 的柵極與 MOSFET 的源極直接用引線相連,再由 MOSFET 的源極引線連接到源極 的 端 子 處 。這 樣 Lint3 被 剔 除 到 D 型 GaN HEMT 驅(qū)動環(huán)路之外,共源極電感只剩 Lint1。此外,2016 年,韓國電子通信研究院通過在 D 型GaN HEMT 柵極和 MOSFET 的源極之間增加單根引線(Lint4),成功減小了共源電感 Lint3。如圖 5(d)所示,增加單根引線 Lint4以后圖中的藍色虛框線內(nèi)是一個?型網(wǎng)絡(luò)。基于戴維南定理,π型網(wǎng)絡(luò)和圖 5(e)中綠色虛框線內(nèi)的 T 型網(wǎng)絡(luò)等效。綠色框線內(nèi)的等效電感 Lint3’小于 Lint3。結(jié)果表明,改變 Lint2的連接方式這種方法簡單有效,完全消除了共源極電感 Lint3的影響,而增加單根引線 Lint4只是減小了共源極電感 Lint3的電感值,其影響仍然存在。

其次,按順序消除共源極電感 Lint1。Lint1的作用是連接 D 型 GaN HEMT 的源極和 MOSFET的漏極。如圖 5(c)所示,2016 年,美國弗吉尼亞理工大學(xué)將 MOSFET 的漏極直接焊接到 D 型GaN HEMT 的源極上,制作堆疊芯片結(jié)構(gòu)可將Lint1消除。

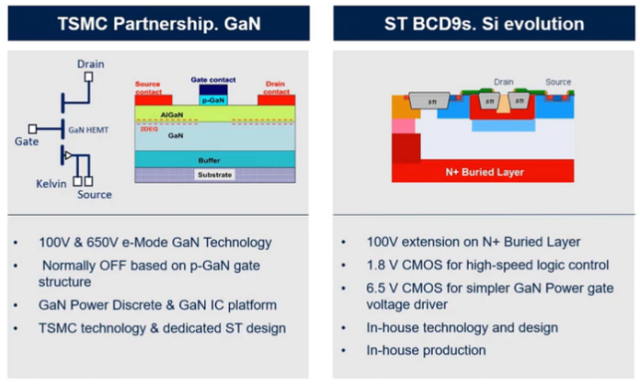

最后,Cascode GaN HEMT 結(jié)構(gòu) TO 型封裝中共源極電感只剩下 LS。LS是柵極引腳產(chǎn)生的雜散電感,使用 PQFN 型封裝可以將 LS消除。此外,如圖 5(f)所示,在 PQFN 封裝中引入開爾文(Kelvin)電極,可以將 MOSFET 的驅(qū)動環(huán)路和功率環(huán)路解耦,共源極電感只有 Lint3、Lint1,其消除方法同 TO 型封裝一致。調(diào)整引線級聯(lián)方式仍然屬于有引線封裝結(jié)構(gòu)的范疇,要想進一步降低雜散電感,勢必要開發(fā)無引線封裝型式。

2.2.2 無引線封裝型式代替引線互連

無引線封裝型式對 Cascode GaN HEMT、E型 GaN HEMT 功率器件/模塊都適用。鍵合線產(chǎn)生的雜散電感通常在納亨(nH)級別。以引線鍵合封裝型式的 TO-220 封裝為例,雜散電感?10nH,這嚴(yán)重限制了 GaN HEMT 在高頻下的開關(guān)性能。因此,許多研究人員考慮采用無引線封裝型式。無引線封裝型式能降低雜散電感的原因有二。其一,消除引線,增大了電流流過導(dǎo)體的橫截面積,電感減小。其二,減小整個電流環(huán)路的面積,電感減小。感應(yīng)電動勢的計算公式如式(2):

式中 Δ? 為磁通量的變化量, Δt 為時間的變化量。由此可知,環(huán)路面積越小,單位時間內(nèi)通過的磁感線越少,產(chǎn)生的感應(yīng)電動勢越小,電感越小。

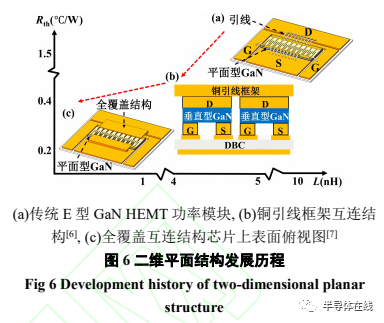

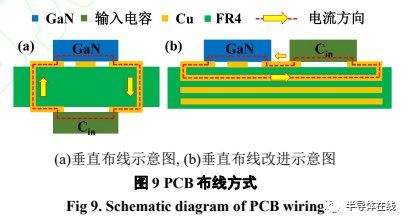

無引線封裝型式分為兩大類:二維平面結(jié)構(gòu)和三維集成結(jié)構(gòu)。二維平面結(jié)構(gòu)通過增大電流流過導(dǎo)體截面積來降低雜散電感。例如,2016年,美國弗吉尼亞理工大學(xué)提出使用薄銅片代替引線的研究設(shè)想。2018 年,德國埃爾朗根-紐約堡大學(xué)成功使用銅引線框架封裝 GaN 功率模塊。2020 年,韓國漢陽大學(xué)針對平面型 GaN芯片提出全覆蓋互連的新概念。其中,薄銅片的橫截面積最小,對雜散電感減小的效果最差。銅引線框架在薄片狀的基礎(chǔ)之上增加了厚度,在降低雜散電感的同時,提升了電極處的散熱效率。全覆蓋互連結(jié)構(gòu)在銅引線框架的基礎(chǔ)之上制作與電極形狀相近的圖形,以最大的面積覆蓋電極,增大電極處導(dǎo)體的截面積,進一步降低雜散電感。圖 6 為二維平面結(jié)構(gòu)的發(fā)展歷程。

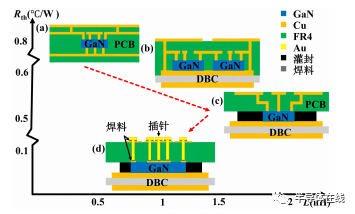

由E型GaN HEMT組成的功率模塊電流環(huán)路中會存在集成電容等分立器件,它們會占據(jù)一定空間,要想實現(xiàn)更小的電流環(huán)路面積,就要考慮三維集成結(jié)構(gòu),形成垂直電流環(huán)路。圖7為三維集成結(jié)構(gòu)的發(fā)展歷程。例如,2016年,德國弗勞恩霍夫可靠性與微集成研究所開展了GaN芯片嵌入式PCB/DBC混合結(jié)構(gòu)的研究,極大減小了電流環(huán)路面積,環(huán)路雜散電感可低至0.43nH。2018年,美國東哈特福德聯(lián)合技術(shù)研究中心也開展了將E型GaN HEMT嵌入到多層PCB基板中的研究。但是芯片嵌入式結(jié)構(gòu)的熱阻以及制造工藝復(fù)雜程度都較高。為了降低熱阻以及降低制造工藝的復(fù)雜程度,2018年,丹麥奧爾堡大學(xué)和2020年,弗吉尼亞理工大學(xué)分別針對兩種不同的三維集成的芯片非嵌入式結(jié)構(gòu)展開了研究。相比于芯片嵌入式結(jié)構(gòu),其電流環(huán)路的路徑以及面積都增大,雜散電感雖然有所增大,但增幅并不明顯。目前,美國弗吉尼亞理工大學(xué)在2020年提出的PCB插入器式結(jié)構(gòu)是GaN功率器件較為先進的封裝結(jié)構(gòu),能最大限度同時保證低熱阻和低雜散電感。

2.2.3 拓?fù)潆娐反畔嘞O(shè)計

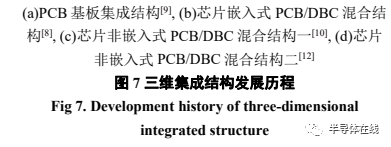

這種方法同時適用于傳統(tǒng)的引線鍵合封裝型式和無引線鍵合封裝型式。前文介紹到雜散電感分為自感和互感。互感是指當(dāng)一個電流回路中電流發(fā)生變化時,其產(chǎn)生的磁場會在臨近的電流回路中產(chǎn)生感應(yīng)電動勢,影響其電流的變化。如圖8(a), (b)所示是線路 1 產(chǎn)生的磁場對線路 2 的影響。當(dāng)線路 1 和線路 2 電流方向相同時,線路 2雜散電感為式(3):

L總 = L自 + M 互

當(dāng)線路 1 和線路 2 電流方向相反時,線路 2雜散電感為式(4):

L總 = L自-M 互 (4)

基于互感的原理,可通過設(shè)計使得相鄰的電流回路方向相反,這樣相鄰的兩個電流回路產(chǎn)生磁相消,達到降低電感的目的。

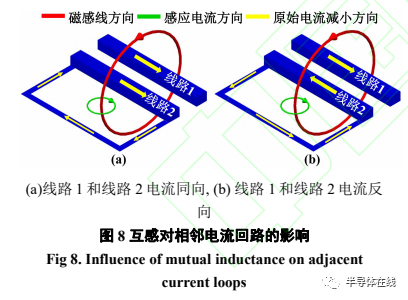

拓?fù)潆娐反畔嘞O(shè)計主要通過基板實現(xiàn)。在GaN功率器件/模塊中常用到以印制電路板(PCB)、直接覆銅基板(DBC)、絕緣金屬基板(IMS)三種基板。例如,2013年,美國弗吉尼亞理工大學(xué)基于磁相消設(shè)計原理,使用PCB基板制作了E型GaNHEMT功率模塊,環(huán)路電感低至0.2nH。如圖9(a)所示,E型GaN HEMT可以和輸入電容、驅(qū)動芯片等器件放置在PCB基板的上下兩面,既能實現(xiàn)磁相消設(shè)計,又能縮小電流回路的面積。例如,2014年,美國EPC公司提出了將多層PCB基板的第一內(nèi)層作為電流的返回路徑的方案,可減小電流線路之間的距離,起到增大互感的作用,同時大幅縮短了電流回路的面積。如圖9(b)所示。改進后雜散電感從1nH下降至0.4nH左右。同樣,2019年,韓國漢陽大學(xué)提出了在PCB基板上制作過孔,形成垂直的電流環(huán)路的新思路,并在此基礎(chǔ)上改進電路布局進一步降低了雜散電感。值得注意的是,PCB基板雖然易于實現(xiàn)磁相消設(shè)計,但是熱導(dǎo)率低的缺點是限制其在GaN功率器件/模塊中應(yīng)用的主要障礙。IMS基板與PCB基板有類似的地方,它是在金屬基板上層壓絕緣材料,繼而層壓銅箔,通過特定工藝在銅箔上刻蝕出一定走線形狀。IMS基板根據(jù)自身的特點可利用其底部的金屬基板進行電磁屏蔽,降低雜散電感的影響。IMS基板不需要復(fù)雜的布局和結(jié)構(gòu)設(shè)計就能達到低雜散電感的要求,這是其獨特的優(yōu)勢[39]。此外,DBC基板也可以通過多層制作實現(xiàn)垂直環(huán)路的磁相消設(shè)計。例如,2015年,日本富士電機公司(Fuji Electric Company)就利用了垂直環(huán)路磁相消的設(shè)計原理,已經(jīng)開展了采用多層DBC封裝硅基功率模塊的研究。但目前該方法在GaN功率器件/模塊中的研究尚未見報道。

2.3 小結(jié)與展望

雜散電感嚴(yán)重限制了 GaN 發(fā)揮其高開關(guān)速度的優(yōu)勢。為了減小雜散電感帶來的影響,在GaN 功率器件/模塊中減小雜散電感主要有三個思路,分別是調(diào)整引線的級聯(lián)方式、開發(fā)無引線封裝型式以及通過優(yōu)化拓?fù)潆娐返慕Y(jié)構(gòu),利用互感的作用降低雜散電感。調(diào)整引線的級聯(lián)方式這種思路只適用于 Cascode GaN HEMT,而且對雜散電感的減小有限,其效果也遠低于無引線封裝型式。同時,降低雜散電感影響的整個研究歷程也是從傳統(tǒng)的引線鍵合封裝型式發(fā)展到無引線封裝型式,在未來無引線封裝型式將代替?zhèn)鹘y(tǒng)的引線鍵合封裝型式。目前 Cascode GaN HEMT 的無引線封裝型式只有一種:使用薄銅片代替引線。這種方式對雜散電感的降低效果有限,有待進一步開發(fā)更多的針對 Cascode GaN HEMT 的無引線封裝型式。E 型 GaN HEMT 功率器件/模塊的無引線封裝型式目前有很多種,為進一步縮短電流環(huán)路的面積,封裝結(jié)構(gòu)從二維平面型結(jié)構(gòu)發(fā)展到三維集成結(jié)構(gòu)。三維集成結(jié)構(gòu)在降低雜散電感的同時也極大減小了模塊的尺寸,具有發(fā)展?jié)摿ΑU{(diào)整引線級聯(lián)方式和無引線封裝型式這兩種方法的思路都是從結(jié)構(gòu)設(shè)計上出發(fā),而拓?fù)潆娐反畔嘞O(shè)計則是從自感和互感的機理出發(fā)降低雜散電感,方法簡單、有效。在未來,設(shè)計制作三維集成結(jié)構(gòu),同時對拓?fù)潆娐愤M行合理布局使其產(chǎn)生磁相消,是 GaN 功率器件/模塊降低雜散電感的主要研究方向。

3 封裝散熱設(shè)計

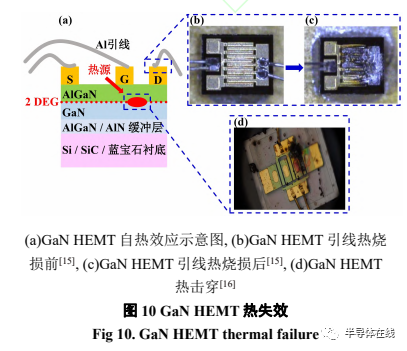

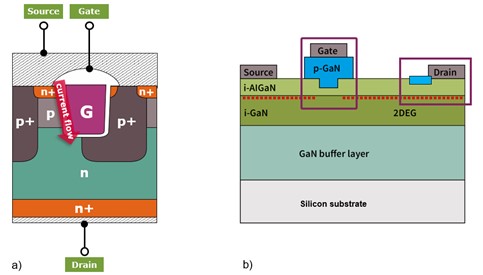

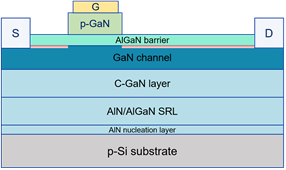

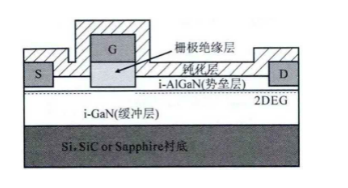

以往研究發(fā)現(xiàn),GaN HEMT 的自熱效應(yīng)非常顯著。如圖 10(a)所示,在 GaN 晶體管中,具有高電子遷移率的二維電子氣(2DEG)被限制在AlGaN 和 GaN 的產(chǎn)生的異質(zhì)結(jié)接觸面內(nèi),這使得其熱流密度非常大,尤其在柵極靠近漏極處的狹長區(qū)域內(nèi),會產(chǎn)生大量的焦耳熱。圖10(b)—(d)分別為自熱效應(yīng)造成引線的熱燒損以及 GaN HEMT 的熱擊穿現(xiàn)象,需要通過合理設(shè)計封裝結(jié)構(gòu),及時將熱量從熱源位置傳遞出去。因此,GaN 器件/模塊的封裝散熱設(shè)計至關(guān)重要。目前針對 GaN 功率器件/模塊的封裝散熱設(shè)計可以分為 3 大類:遠結(jié)被動冷卻封裝結(jié)構(gòu)、近結(jié)被動冷卻封裝結(jié)構(gòu)、近結(jié)主動冷卻封裝結(jié)構(gòu)。

3.1 遠結(jié)被動冷卻封裝結(jié)構(gòu)

被動冷卻是通過熱傳導(dǎo)的方式,靠熱量自身從高溫物體傳遞到低溫物體,完成散熱。在傳統(tǒng)的封裝結(jié)構(gòu)中,熱量傳遞路徑一般經(jīng)過芯片連接材料、基板、導(dǎo)熱膠到熱沉,所以又叫遠結(jié)被動冷卻。因此,降低傳熱路徑上各介質(zhì)的熱阻可以增大熱量的傳遞效率。目前在 GaN 功率器件/模塊中都是針對封裝基板進行改進設(shè)計,降低熱阻,提升其散熱性能。前文介紹到在 GaN 功率器件/模塊中,最常用的是印制電路板(PCB)、直接覆銅基板(DBC)、絕緣金屬基板(IMS)三種基板。下面分別將三種基板在 GaN 功率器件/模塊中應(yīng)用時的結(jié)構(gòu)設(shè)計進行介紹。

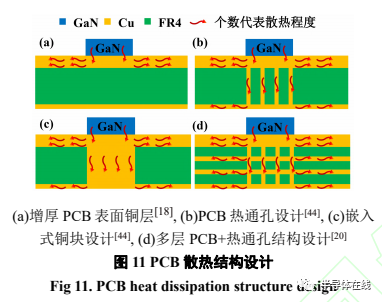

制作 PCB 基板的常用材料 FR4 的熱導(dǎo)率極低(0.2W/m?K),這是其在 GaN 功率器件/模塊中應(yīng)用的主要障礙。因此,許多研究人員考慮從結(jié)構(gòu)上進行設(shè)計,降低 PCB 基板的熱阻。例如,2017 年,法國巴黎第十一大學(xué)開展了改善GaN 芯片散熱性能的優(yōu)化研究。如圖 11(a)所示,增厚 PCB 基板頂部刻蝕電路銅層的厚度可以降低 PCB 基板的熱阻。由于 Cu 和 FR4 的熱導(dǎo)率差很大,隨著銅層厚度的增厚,熱量在垂直穿過 FR4 之前,在橫向上更加均勻的鋪展開,這種結(jié)構(gòu)的橫向熱擴散效應(yīng)使得熱阻下降。但是當(dāng)上銅層的厚度超過 300μm 時,熱阻降幅將不明顯,而且與 DBC 相比,熱阻差異仍較大。

如前述,通過增厚 PCB 基板頂部刻蝕電路銅層,可提升熱量在 PCB 基板表面的橫向傳遞效 率 。在 此 基 礎(chǔ) 之 上 , 在 PCB 基 板 與 GaN HEMT 直接接觸的地方制作導(dǎo)熱通孔,可以提升熱量的縱向傳遞效率。該設(shè)計思路目前主要有兩種形式,分別如圖 11(b)、圖 11(c)所示:PCB基板熱通孔設(shè)計和嵌入式銅塊設(shè)計。兩種設(shè)計的散熱性能相差不大,嵌入式銅塊設(shè)計熱阻略低一些。但是嵌入式銅塊設(shè)計的制作工藝偏復(fù)雜,銅塊與芯片、銅塊與熱沉之間的連接界面要保證平坦,孔隙和裂縫的存在都會阻礙熱量的傳遞。相比之下 PCB 基板熱通孔技術(shù)制造工藝簡單,目前應(yīng)用最為廣泛。例如,2011 年,比利時 魯 汶 大 學(xué) (Catholic University of Leuven, Belgium)提出了在 PCB 基板熱通孔中鍍金的改良方案,與以往僅使用 LTCC 基板封裝相比,GaN 功率放大器的最大輸出功率提高近 5 倍。2018 年,威斯康星大學(xué)麥迪遜分校的研究團隊通過仿真分析研究,發(fā)現(xiàn)當(dāng) PCB 基板上銅層厚度大于 0.07mm,銅面積大于 4032.25mm2,即使在不使用散熱器的條件下,也能保證使用特定BGA 或 LGA 封裝的 GaN 集成電機驅(qū)動部件在2W 的芯片發(fā)熱功耗工作時,其殼溫不超過150℃,保證模塊的可靠使用。2019 年,德國英飛凌公司又基于 PCB 基板易實現(xiàn)多層加工的特點,在熱通孔設(shè)計的基礎(chǔ)上,增加了 PCB 基板中的橫向散熱路徑,進一步提升了 PCB 基板的散熱性能,其設(shè)計結(jié)構(gòu)如圖 11(d)所示。

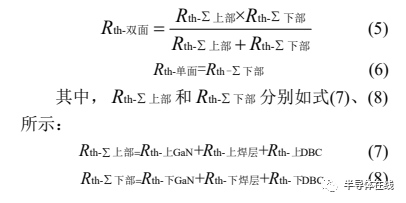

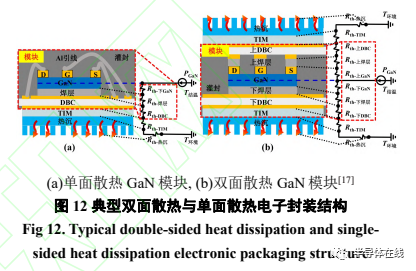

在 GaN 功率器件/模塊封裝技術(shù)中,DBC 基板因為具有較高的熱導(dǎo)率(AlN 陶瓷基板:200W/m?K)而應(yīng)用最多。在相同試驗條件下,GaN 功率模塊使用 DBC 基板比使用 PCB 基板可使 GaN 芯片的最大結(jié)溫下降 136℃。但是在多芯片的 GaN 功率模塊中,單面 DBC 結(jié)構(gòu)不能及時將多芯片產(chǎn)生的熱量傳遞出去,熱量的疊加使 得 E 型 GaN HEMT 的 最 大 結(jié) 溫 達 到155℃。長時間的高溫工作會加速芯片失效、芯片連接層以及引線的可靠性問題。因此,例如在 2020 年,西安交通大學(xué)提出了雙面 DBC 的散熱結(jié)構(gòu)設(shè)計(如圖 12(b)所示),該方案可實現(xiàn)上下兩部分熱阻并聯(lián),降低整體封裝結(jié)構(gòu)的熱阻。雙面散熱和單面散熱的結(jié)殼熱阻(junctionto-case)分別如式(5)、式(6)所示:

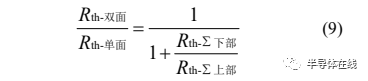

由式(5)、式(6)可知,雙面散熱模塊比單面散熱模塊芯片結(jié)溫下降的比率為式(9):

由式(9)可知, (Rth- Σ上部) / (Rth-Σ下部) 越小,結(jié)溫的下降幅度越大。而對于平面型 GaN 芯片,電極全部分布在芯片的上表面,散熱面積小,所以熱量大部分向下傳遞, Rth-Σ下部 小于Rth- Σ上部 。因此,可以通過調(diào)整熱模塊上下兩部分的散熱條件,來提升芯片結(jié)溫的下降幅度。

IMS基板在GaN功率器件/模塊中使用時,目前未見有獨特的結(jié)構(gòu)設(shè)計。IMS基板是通過底部金屬基板進行散熱,表面電路層和底部金屬基板之間的絕緣層是熱量傳遞的主要障礙。IMS基板熱阻略高于DBC基板,是其熱阻的1.5倍;但遠低于PCB基板的熱阻。值得注意的是,即使使用PCB嵌入式銅塊設(shè)計,其熱阻依然在IMS基板熱阻的2倍以上。

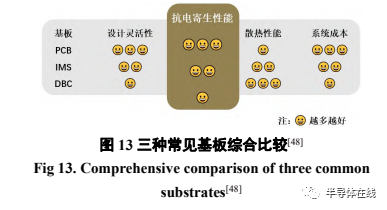

將上述 PCB、DBC、IMS 三種基板進行綜合比較,不難發(fā)現(xiàn),對于 PCB 來講,熱通孔設(shè)計、嵌入式銅塊設(shè)計與垂直環(huán)路磁相消設(shè)計很難做到同時兼顧。多層 DBC 的結(jié)構(gòu)雖然能同時保證散熱和低雜散電感的要求,但設(shè)計復(fù)雜且制作難度大。相比于 PCB 基板和 DBC 基板,IMS 基板顯示出其獨特的優(yōu)勢。它不需要復(fù)雜的布局和設(shè)計,就能同時實現(xiàn)較低的熱阻和較小的雜散電感。這也是目前 IMS 基板并沒有獨特結(jié)構(gòu)設(shè)計的原因。此外,IMS 基板還有較低的制作加工成本以及較高設(shè)計靈活性的優(yōu)勢。圖 13 從設(shè)計靈活性、抗電寄生性能、散熱性能、系統(tǒng)成本四個方面,將 GaN 功率器件/模塊中常用的三種基板進行了綜合比較。

3.2 近結(jié)被動冷卻封裝結(jié)構(gòu)

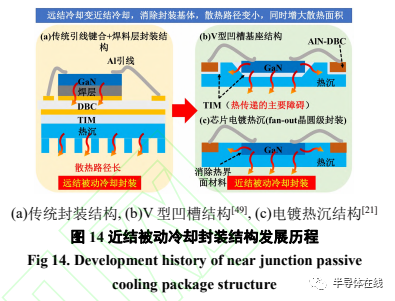

在前文介紹到的遠結(jié)被動冷卻封裝結(jié)構(gòu)中,熱量從芯片產(chǎn)生,經(jīng)過封裝基體傳遞到外界環(huán)境。然而對于整個封裝體結(jié)構(gòu),有 67%的熱阻來自于芯片以外的封裝基體(焊料、灌封材料、基板、導(dǎo)熱膠等)。因此,區(qū)別于遠結(jié)被動冷卻,許多研究人員考慮近結(jié)被動冷卻,即通過封裝的結(jié)構(gòu)設(shè)計,使得熱量的傳遞路徑不經(jīng)過封裝基體,一經(jīng)產(chǎn)生就被熱沉傳遞出去。近結(jié)被動冷卻主要是通過增加芯片的散熱面積達到降低熱阻的目的。例如,2012 年,中國臺灣交通大學(xué)(National Chiao Tung University, China)開展了直接在熱沉上連接芯片的研究[49]。如圖 14(b)所示,在熱沉結(jié)構(gòu)上制作 V 型凹槽,將 E 型 GaNHEMT 置入其中并使用導(dǎo)熱銀膠填充,通過增加芯片的橫向散熱路徑,增大芯片整體的散熱面積。然而通常 GaN 芯片的厚度較小(GaN System公司 GS-065-150-1-D 款 E 型 GaN HEMT 厚度264.5μm),增加的芯片側(cè)面散熱面積并不大,同時芯片與熱沉結(jié)構(gòu)之間的導(dǎo)熱界面材料依然是熱量傳遞過程中的阻礙。所以這種結(jié)構(gòu)的散熱效果并不顯著。

值得注意的是,近來,扇出式(fan-out)晶圓級封裝由于具有更低的熱阻,更高的功率密度而備受關(guān)注。因此,許多研究人員考慮將 fan-out晶圓級封裝的理念引入到 GaN 模塊封裝中。例如,2012 年,美國休斯研究室直接在 E 型 GaN HEMT 背面電鍍金屬形成熱沉結(jié)構(gòu)。如圖14(c)所示,這種結(jié)構(gòu)可以節(jié)省導(dǎo)熱界面材料的使用,進一步降低熱阻,最大可以使芯片結(jié)溫下降 100℃。2018 年,德國弗勞恩霍夫可靠性與微集成研究所使用扇出型封裝形式制作了650V GaN 半橋功率模塊。但目前尚未見到對高壓氮化鎵 fan-out 晶圓級封裝的報道。這可能是因為極小的引腳間距尚無法滿足高電壓下安全爬電距離的設(shè)計要求。此外,氮化鎵 fan-out 晶圓級封裝目前也僅用在低功率場合。雖然在 2020年,德國弗勞恩霍夫可靠性與微集成研究所提出了 GaN 射頻功率器件的 fan-out 晶圓級封裝設(shè)計,并成功研制出實驗室樣品,但其晶圓級封裝器件抗功率循環(huán)、抗溫度循環(huán)的可靠性有待進一步驗證。

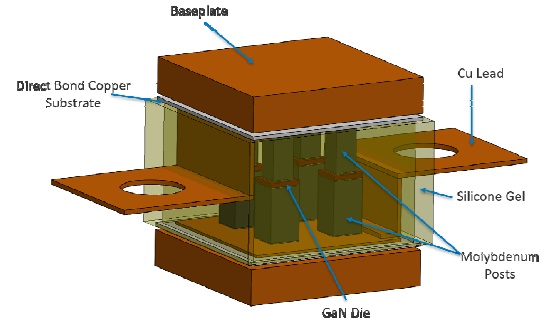

3.3 近結(jié)主動冷卻封裝結(jié)構(gòu)

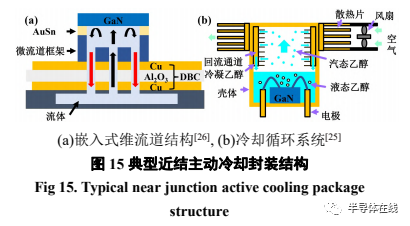

首先區(qū)分主動冷卻與被動冷卻:主動冷卻通常安裝散熱部件,借助外力增加熱傳遞的效率。接下來介紹的近結(jié)主動冷卻是在消除封裝基體的基礎(chǔ)之上(即近結(jié)冷卻),增加主動散熱的方式。例如,2011 年,日本松下電氣公司就已開展了在 GaN 功率器件中使用冷卻循環(huán)系統(tǒng)的散熱研究。2016 年,美國洛克希德·馬丁任務(wù)系統(tǒng)與訓(xùn)練分公司也開展了 GaN 功率模塊中制作嵌入式微流道結(jié)構(gòu)的研究。如圖 15(a)所示,嵌入式微流道結(jié)構(gòu)完全消除了金屬熱沉。通過冷卻液直接接觸金屬襯底將熱量帶走,可以使芯片結(jié)溫最大下降 55%。但是微流體對芯片背部的沖擊作用不可忽視,它會造成芯片的損傷。如圖15(b)所示,將 GaN 芯片封裝到一個冷卻循環(huán)系統(tǒng)框架中可以消除微流體對芯片的沖擊。冷卻循環(huán)系統(tǒng)分為三個部分:蒸發(fā)段、冷凝段、回流段。在蒸發(fā)段,空腔內(nèi)部的乙醇液體直接接觸芯片的背部,吸收芯片產(chǎn)生的熱量蒸發(fā)成汽態(tài)并揮發(fā)到殼體上部。在冷凝段,由于風(fēng)扇不斷向散熱片吹入空氣進行強制熱對流,汽態(tài)乙醇受冷重新凝結(jié)為小液滴。在回流段,冷凝后的乙醇小液滴受殼體內(nèi)部針狀結(jié)構(gòu)毛細吸引力作用,匯聚到回流通道,形成大的乙醇液滴并流回蒸發(fā)段,這樣形成一個循環(huán)。如此不斷重復(fù),完成冷卻循環(huán)系統(tǒng)的導(dǎo)熱過程。該結(jié)構(gòu)與傳統(tǒng)的封裝結(jié)構(gòu)相比,熱阻下降 32%。近結(jié)主動冷卻封裝結(jié)構(gòu)能極大降低封裝結(jié)構(gòu)的熱阻,但往往尺寸較大,且設(shè)計制造復(fù)雜。

3.4 小結(jié)與展望

遠結(jié)冷卻結(jié)構(gòu)與近結(jié)冷卻結(jié)構(gòu)的本質(zhì)區(qū)別是:熱量經(jīng)芯片產(chǎn)生傳遞到熱沉的過程中是否通過封裝基體。近結(jié)冷卻相比于遠結(jié)冷卻,消除了封裝基體,極大降低整體結(jié)構(gòu)的熱阻。主動冷卻相比于被動冷卻,使用液冷的方式提升了熱量的傳遞效率。遠結(jié)被動冷卻結(jié)構(gòu)主要著重于對基板的改進設(shè)計。PCB 基板遵循著從增強表面橫向散熱、增強縱向散熱到橫向散熱和縱向散熱混合使用的設(shè)計思路。DBC 基板則主要著重于開發(fā)雙面散熱結(jié)構(gòu)。近結(jié)被動冷卻結(jié)構(gòu)遵循增加芯片散熱面積的思路,從基板上制作 V 型凹槽到在芯片背部直接電鍍熱沉結(jié)構(gòu)的 fan-out 晶圓級封裝,都通過增加芯片的側(cè)向散熱路徑來增大芯片的散熱面積。制作 V 型凹槽這種方法由于芯片厚度小,且芯片與熱沉之間的導(dǎo)熱膠阻礙熱量傳遞,對散熱性能提升的效果并不顯著。近結(jié)主動冷卻結(jié)構(gòu)設(shè)計了嵌入式微流道和冷卻循環(huán)系統(tǒng)兩種結(jié)構(gòu),雖然極大降低了結(jié)溫,但是這兩種結(jié)構(gòu)尺寸大、制作復(fù)雜,抗機械沖擊可靠性低。

綜上所述,遠結(jié)被動冷卻仍然是 GaN 功率器件/模塊主要使用的封裝結(jié)構(gòu)。其中雙面 DBC散熱結(jié)構(gòu)因具有更低的熱阻,將會成為主流的封裝結(jié)構(gòu)。

4 封裝連接可靠性

GaN 功率器件/模塊的封裝連接可靠性風(fēng)險主要集中封裝連接層。包括連接層材料的開裂,引線鍵合脫落或斷裂等。失效產(chǎn)生的原因是連接層材料和引線鍵合界面的熱機械疲勞損傷。此外,考慮到 GaN 的耐高溫應(yīng)用特性,隨著工作時間的增加,連接層材料會產(chǎn)生熱蠕變疲勞損傷。而在實際的工作過程中,熱機械疲勞損傷和熱蠕變疲勞損傷會產(chǎn)生耦合作用。熱蠕變促進了連接層材料微裂紋的萌生和擴展,熱機械應(yīng)力又提高了熱蠕變的程度。這種耦合作用會加劇連接層材料失效的風(fēng)險。因此,本文接下來將主要介紹如何提高 GaN 功率器件/模塊封裝連接層的熱機械疲勞失效與熱蠕變疲勞失效抗性。目前未見對 GaN 功率器件/模塊中引線失效以及增強引線失效抗性的相關(guān)報道。

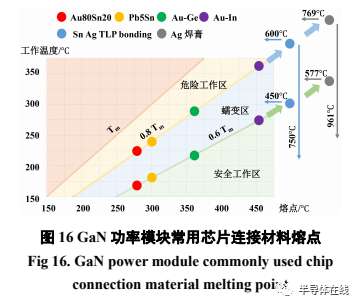

4.1 熱蠕變疲勞失效

對于大多數(shù)連接材料來講,在長時間的高溫工作過程中會有蠕變疲勞失效的風(fēng)險。工作溫度為0.6Tm是連接材料蠕變變形的臨界狀態(tài)(Tm:焊料熔點),當(dāng)溫度超過0.6Tm,蠕變變形機制開始起作用,并逐漸占據(jù)主導(dǎo)地位;當(dāng)工作溫度超過0.8Tm,連接材料會因為蠕變造成晶界滑移,產(chǎn)生塑性變形而快速開裂失效。目前,在低溫段工作的GaN功率器件/模塊中常用的高溫焊料是金基焊料和高鉛焊料。然而隨著研究的不斷進展,最新研制的GaN HEMT可以在325℃下穩(wěn)定工作,所以要求芯片連接材料的熔點至少在400℃以上。如圖16所示,在功率器件/模塊中常用的金基焊料都不能滿足更高的工作溫度要求。同時,合金焊料在長時間的高溫工作條件下,連接 界 面 處 脆 性 金 屬 間 化 合 物 生 長 嚴(yán) 重 。以Au80Sn20為例,在240℃條件下保存72h,脆性金屬間化合物Au-Ni-Sn生長大約1.6?m,造成連接層抗剪強度的下降,進一步增加了連接層熱蠕變疲勞失效的風(fēng)險。此外,由于ROHS指令對焊料無鉛化的要求,高鉛焊料也會被逐漸替代。因此,目前迫切需要開發(fā)熔點更高,同時在高溫下保證高可靠性的焊料,以充分保證GaN器件/模塊的工作可靠性。

在 GaN 功率器件/模塊中,目前流行的兩種芯片連接技術(shù)是瞬時液相 (Transient liquid phase, TLP) 連 接 和 低 溫 連 接 技 術(shù) (Low temperature joining technique, LTJT)。其中瞬時液相連接技術(shù)以錫銀的瞬時液相 (簡稱 Sn Ag TLP)連接應(yīng)用最多,低溫連接技術(shù)以燒結(jié)銀應(yīng)用最多。

TLP 連接技術(shù)通常是指在連接金屬表面鍍覆低熔點金屬作為中間層材料,在適當(dāng)壓力下加熱至熔點。低熔點中間層材料和高熔點金屬發(fā)生固-液互擴散現(xiàn)象,生成高熔點的連接層,實現(xiàn)低溫連接、耐高溫工作的應(yīng)用條件。當(dāng)使用Sn、Ag 作為中間層材料時,Sn 在熔點 232℃下熔化并擴散到 Ag 中與 Ag 生成高熔點的二元合金ζ相 Ag85Sn15(Tm?600℃),連接界面完整、無孔洞,而且不需要助焊劑。例如,2015 年,德國弗萊堡大學(xué)最先開展了 Sn Ag TLP 連接在GaN 芯片封裝中的應(yīng)用研究。然而該方法成本高、時間長,不利于商業(yè)化應(yīng)用。對于 Sn Ag TLP 連接在 GaN 功率器件/模塊中的應(yīng)用研究尚處于起步階段,目前未見對其高溫蠕變疲勞失效的研究報道。這可能與生成的金屬間化合物具有較明顯脆性,疲勞失效的風(fēng)險仍然顯著有關(guān)。

近年來,LTJT 技術(shù),尤其是低溫?zé)Y(jié)銀連接技術(shù)受到廣泛關(guān)注。燒結(jié)銀以其 961℃的高熔點,低焊接溫度的優(yōu)勢,成為替代 Au80Sn20 和高鉛焊料、應(yīng)用在 Cascode GaN HEMT、E 型GaN HEMT 功率器件/模塊中芯片連接的主要候選 材 料 。早 在 2013 年 , 天 津 大 學(xué) (Tianjin University, China)就開展了燒結(jié)銀在高溫下的蠕變疲勞行為研究。研究證實燒結(jié)銀具有較高的熱蠕變疲勞失效抗性,適合在 GaN 功率器件/模塊中使用。

4.2 熱機械疲勞失效

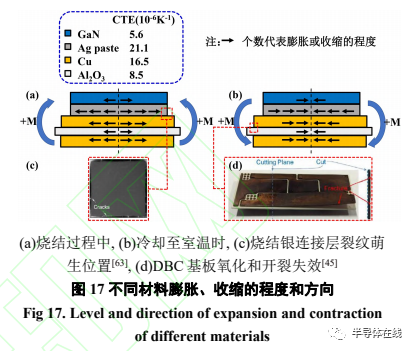

如圖 17(a)、(b)所示,由于不同材料的熱膨脹系數(shù)不同,在溫度的變化過程中,材料的收縮程度就會不同,在界面處會產(chǎn)生交變的熱機械應(yīng)力。熱機械應(yīng)力的表現(xiàn)形式是平行于連接界面的剪切力。剪切力又會使不同材料產(chǎn)生不同程度的塑性變形。隨著循環(huán)次數(shù)的增多,連接層界面材料塑性變形不斷累積,產(chǎn)生熱機械疲勞失效。在 GaN 功率器件/模塊中,由于 CTE 不匹配造成界面開裂失效的位置有兩處,芯片與基板連接層以及 DBC 基板的銅與陶瓷連接層。對于芯片與基板連接層如圖 17(c)所示,其應(yīng)力和塑性功密度的最大值位于芯片連接層靠近 DBC 的邊角處。因此,此處最易萌生裂紋,造成分層開裂現(xiàn)象。對于 DBC 基板,如圖 17(d)所示,其在高溫使用的過程中,高溫工作條件下易發(fā)生銅層脫落的現(xiàn)象。此外,從圖中可以看出 DBC基板的氧化現(xiàn)象十分嚴(yán)重。

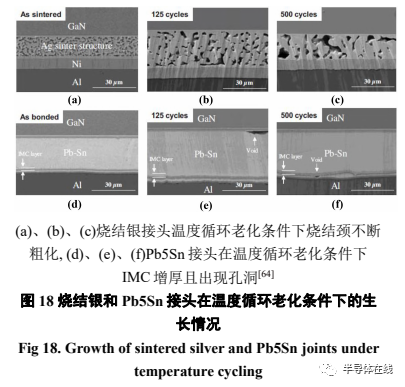

值得一提的是,前文提到的燒結(jié)銀和Sn AgTLP都具有非常高的熱機械疲勞抗性,可以有效的抑制芯片連接層發(fā)生分層斷裂。在溫度循環(huán)老化條件下,燒結(jié)銀的可靠性都要優(yōu)于Au80Sn20和Pb5Sn焊料,因為溫度循環(huán)次數(shù)的增加,燒結(jié)銀接頭的燒結(jié)頸不斷變粗,使得接頭的連接強度變大。如圖18(a)—(c)所示為燒結(jié)銀接頭在溫度循環(huán)作 老 化 條 件 下 燒 結(jié) 頸 不 斷 粗 化 的 現(xiàn) 象 。而Au80Sn20、Pb5Sn接頭在溫度循環(huán)的過程中,脆性金屬間化合物生長加厚,從而造成接頭的抗剪強度的下降。如圖18(d)—(f)所示為Pb5Sn接頭在溫度循環(huán)老化條件下界面金屬間化合物增厚同時出現(xiàn)孔洞的現(xiàn)象。2015年,德國弗萊堡大學(xué)將低溫?zé)Y(jié)銀連接和Sn Ag TLP連接在可靠性方面進行了比較,兩者在功率循環(huán)和溫度循環(huán)作用下都表現(xiàn)出優(yōu)異的可靠性,且優(yōu)于金基焊料和錫鉛焊料。

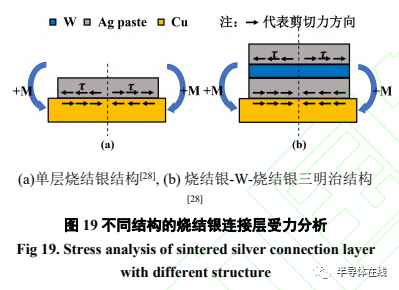

為了抑制芯片連接層的斷裂,2018年,日本大阪大學(xué)從芯片連接層的結(jié)構(gòu)上進行改進,提出了燒結(jié)銀-W-燒結(jié)銀的三明治式結(jié)構(gòu)[28]。圖19是芯片連接層從高溫冷卻至室溫時的應(yīng)力變化行為,利用W薄膜高彈性的特點,使其分擔(dān)芯片連接層和基板界面處的界面應(yīng)力,同時使得燒結(jié)銀和基板連接界面處的應(yīng)力方向重合,界面處材料的塑性應(yīng)變下降大約50%。

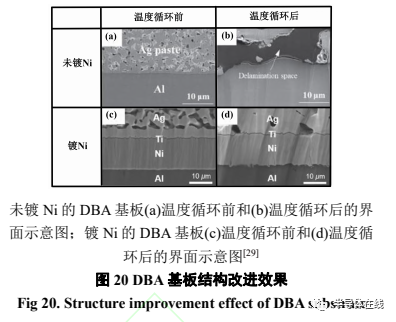

為了抑制 DBC 基板在使用過程中發(fā)生銅層脫落的現(xiàn)象,2018 年,日本大阪大學(xué)開展了GaN 模塊中 DBA 基板表面鍍 Ni 的應(yīng)用研究。如圖 20(a)、(b)所示,將 GaN 芯片連接到DBA 基板上后,發(fā)現(xiàn)在溫度循環(huán)老化條件下DBA 基板開裂。這是因為 Al 晶粒在高溫作用下會粗化長大,而且鋁的楊氏模量低,容易發(fā)生塑性變形。這使得燒結(jié)銀和 DBA 基板的連接界面在工作中會有裂紋萌生并擴展,從而造成界面開裂現(xiàn)象。為此,作者在 DBA 基板表面鍍厚Ni 層(7μm)。如圖 20(c)、(d)所示,Ni 在高溫作用下,晶粒長大的不明顯,可以抑制 Al 晶粒的粗化。在 GaN 功率器件/模塊中使用 DBA 基板表面鍍 Ni 代替 DBC 基板,避免了基板銅層脫落的風(fēng)險,同時提高了連接界面的可靠性。

4.3 小結(jié)與展望

為了解決熱蠕變疲勞失效的問題,研究人員已提出了采用低溫?zé)Y(jié)銀連接材料技術(shù)和 Sn AgTLP 連接材料技術(shù)。這兩種材料同時具有較高的熱蠕變疲勞以及熱機械疲勞失效抗性,應(yīng)是未來研究的熱點。為了解決熱機械疲勞失效的問題,研究人員還提出改變芯片連接層的結(jié)構(gòu)以及在基板表面鍍 Ni 兩種方法。“Ag-W-Ag”三明治式結(jié)構(gòu)雖然能大幅降低界面處連接材料的塑性應(yīng)變,但結(jié)構(gòu)復(fù)雜,實際操作困難。DBA 基板表面鍍Ni 這種方法簡單有效,明顯降低了基板表面附層脫落的風(fēng)險。

5 GaN 功率器件/模塊封裝技術(shù)的思考

盡管 GaN 功率器件/模塊的封裝技術(shù)是當(dāng)前研究熱點,在降低雜散電感、封裝散熱結(jié)構(gòu)設(shè)計和提升封裝連接可靠性等方面也已引起廣泛關(guān)注 。2018 年 , 美 國 阿 肯 色 大 學(xué) (Uniersity ofArkansas, USA)研究團隊[65]最先發(fā)表了先進 GaN器件封裝與集成研究綜述,從芯片級封裝、模塊級封裝與集成和封裝熱管理三個方面提出 GaN封裝技術(shù)面臨的挑戰(zhàn),并指出當(dāng)下需要重點研究的三大問題:(1)降低 GaN 器件功率環(huán)路和驅(qū)動環(huán)路的雜散電感;(2)優(yōu)化 GaN 集成模塊開關(guān)性能;(3)提出更有效的熱管理方案。目前,針對這三個問題都有許多效果顯著的解決方案,已經(jīng)在文中進行闡述。然而仍存在大量亟待解決的問題以及研究空白,處于剛起步階段。

1)雙面 DBC 散熱結(jié)構(gòu)、芯片嵌入式結(jié)構(gòu)和帶有 PCB 插入器的 GaN 功率器件/模塊存在可靠性瓶頸。這是因為這三種結(jié)構(gòu)都是目前較為先進的封裝結(jié)構(gòu),同時具有較低熱阻、低電感的優(yōu)良特性,但由于結(jié)構(gòu)復(fù)雜,會增大整個封裝體的內(nèi)應(yīng)力,降低其可靠性。使用 CTE 相匹配的封裝材料或使用合適的灌封材料做緩沖層也許是有效的解決方案。

2)亟待開展 Cascode GaN HEMT 的雙面散熱結(jié)構(gòu)的開發(fā)與封裝可靠性研究。其中 E 型GaN HEMT 表面復(fù)雜的電極形狀是其實現(xiàn)雙面散熱結(jié)構(gòu)的最大阻礙。采用芯片嵌入式封裝的方法實現(xiàn)雙面散熱或許是可行的方案。

3)亟待揭示 GaN 功率器件/模塊中連接層材料與引線在熱蠕變疲勞和熱機械疲勞耦合作用下的失效模式、失效機理以及顯微組織變化等。但是由于熱蠕變和熱機械應(yīng)力耦合的試驗條件難以實現(xiàn),目前對于這一部分的研究仍是空白。可以考慮先從仿真研究入手,提供物理模型和仿真數(shù)據(jù),為以后的試驗研究打下基礎(chǔ)。

4)亟需探索 GaN 功率器件/模塊中引線失效形式以及提升其可靠性的方法。尤其值得注意的是,GaN 功率器件/模塊的耐高溫應(yīng)用特性會增大引線產(chǎn)生熱蠕變損傷的風(fēng)險,聚焦其在高溫下的蠕變疲勞行為開展研究更有研究價值。具體研究可以沿著溫度梯度對引線與基板連接界面上晶粒塑性變形程度影響的路徑去探索。

不難發(fā)現(xiàn),問題(1)、(2)、(3)都是有關(guān) GaN基功率器件/模塊無引線封裝型式可靠性方面的問題,是這一領(lǐng)域亟待解決的最關(guān)鍵問題。因為目前研究人員在追求 GaN 功率器件/模塊的低雜散電感封裝、低熱阻封裝型式的時候,往往并不能同時兼顧其在可靠性方面的性能,導(dǎo)致這些研究成果并不能很好的商業(yè)化應(yīng)用。因此,解決新型 GaN 功率器件/模塊封裝型式的可靠性問題對于推進科研成果產(chǎn)業(yè)化具有重要意義。相比之下,問題(4)屬于次要關(guān)鍵問題,因為該問題是關(guān)于引線鍵合封裝型式的 GaN 功率器件/模塊中引線的可靠性問題,然而目前引線在 GaN 器件/模塊中使用頻率越來越少,將來勢必會被無引線封裝型式取代。

審核編輯:湯梓紅

電子發(fā)燒友App

電子發(fā)燒友App

評論