LED驅動電源目前正朝著高功率因數、高輸出電流精度、高效率、高可靠性和低成本、小尺寸方向發展,因此,帶PFC(功率因數校正)的原邊電流反饋 準諧振技術方案已漸漸成為市場主流。現有的照明用LED驅動電源目前標準仍有待統一,但PFC在全電壓范圍內做到0.95以上、輸出電流精度做到±3%以 內、效率做到90%以上、啟動時間在0.5s以內、輸出電壓紋波小于5%等,已經成為一些業內領先的芯片供應商設置的技術競爭門檻。

要達到 上述這些要求,市場必然要求有一款功能全面、性能優異的芯片,同時,這也對系統設計者提出了更高的要求。本文從芯片和系統兩個層面,詳細分析了影響上述性 能的原因和提高各項性能的手段,并給出了實驗波形和數據。無論對于LED驅動芯片設計者還是系統設計者而言,都具有一定的參考意義。

基本原理

LED驅動電源功率較小,器件的應力裕度較大,加之其對尺寸有嚴格要求,需采用盡可能小的原邊電感量,因此,它一般采用DCM峰值電流控制PFC的方式。其原、副邊的電流方程為:

式中:n=Np/ Ns為原副邊匝比;IP為原邊峰值電流。

由 公式(1)可知,要使輸入電流峰值IP跟隨輸入電壓Vm做正弦變化,只要讓ton在一個正弦半波時間內保持恒定就能做到。另一方面,如果采用乘法器方案, 強制讓IP跟隨Vm變化,則ton必然在一個正弦半波周期內保持恒定。前者稱之為固定導通時間PFC方案。其優點是可以節省Vins的采樣電阻,節省芯片 管腳,提高系統效率。但由于實現PFC是靠DCM和原邊起始電流為0這兩個先決條件保證的,所以在CCM或非準諧振模式工作的系統中應用受限。后者稱之為 乘法器PFC方案。其優點是不受工作模式及原邊電流起始值的影響,只需考慮最后的電流峰值是否跟蹤輸入電壓。這是一種更為直接的控制,能夠得到更高的PF 值。但這同時也增加了芯片設計者的設計難度,需要保證乘法器的寬廣線性度和THD等指標,并且也增加了芯片面積。PT4209為了得到更好的系統性能,采 用了乘法器PFC方案。

表2:PF值。

為 了節省副邊反饋網絡和光耦等元件,在小功率應用場合,一般電路采用PSR(原邊反饋)控制方式。該法適用于對輸出精度、輸入調整率、負載調整率要求不高, 負載不會突然變化的場合,并且該法在輸入突變時也加快了系統的保護。LED驅動電源正好滿足上面的應用條件。其副邊電流反饋公式為:

?

表1:輸入電壓調整率及負載調整率。

?

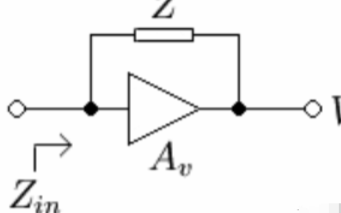

芯 片采樣Vcs和tdis/T兩個信號,再將兩個信號相乘和Vref相比較;兩者的差值經過一個跨導放大器(gm)和Ccomp電容濾波,再將濾波的結果和 Vin的采樣結果Vins一起送入到乘法器相乘;乘法器輸出即為Vcs的給定信號,芯片以此來控制開關管的關斷。其芯片內部的邏輯框圖如圖1所示。

圖1:PT4209內部的邏輯框圖。

在開關管關斷后,為了最大限度減小開關損耗,希望在Vds最小時打開開關管。這就要求芯片有谷底檢測的功能,即所謂的準諧振控制。其諧振周期由變壓器原邊電感Lp與MOS管輸出電容Cd (或稱Coss)共同決定,公式為:

系統參數及原理圖

PT4209 的功率應用范圍為5W~30W。以一款應用于PAR38燈具的16W驅動電源為例,系統的性能參數如下:輸入電壓85V~264V;輸出電壓 3.2V*16=51.2V(16個LED串聯);輸出電流320mA;變壓器骨架選擇PQ2016,原邊電感量選0.65mH,保證在264V高壓輸入 下,最高開關頻率小于150kHz。系統原理圖如圖2所示。

圖2:16W PAR38燈具電路原理圖。

PF值的影響因素及提高手段

系統PF值的高低,主要與輸入電流和輸入電壓的相角差和輸入電流的THD兩個因素有關。計算公式為:

其中:V1、I1為基波有效值;Vin、Iin為總的有效值。

其中:Ik為k次諧波的有效值。

故

首先,芯片控制的是輸入峰值電流的正弦化,而PF計算的是平均電流的正弦化,這里相差一個占空比D。公式為:

其中:ton、Lp、Vr在一個周期內恒定,所以,并不是一個正弦,而是一個削頂的準正弦波形。這勢必會影響一些PF值,這也就是峰值電流控制的芯片PF值始終不能達到1的根本原因。

接 下來,由上面的邏輯框圖可知,要保證乘法器的輸出是一個良好的正弦波形,這個和三個因素有關:第一是Vcomp電容要足夠大,才能濾去100Hz的工頻紋 波。但該電容也不能選擇過大,否則會使得上電后抽取過多Vcs電容的能量而導致UVLO出現。選擇過小,則會出現輸入電流波形向前偏的現象,且該現象因為 輸入電壓的升高而日趨嚴重。因為Vcomp上紋波大小不變,但穩態值變小,相應紋波所占比例越大。第二是整流橋后端電容Cin要足夠小,才能保證良好的正 弦波形。此外,電容過大的話,電容上的充放電電流會和原邊電流疊加,也會使得輸入電流向前偏。但Cin也不能太小,否則會使得輸入電壓的開關紋波變大。極 端情況下,僅靠Cin已不足以維持一個開關周期的開通,而前端又有電感使得電流不能突變,從而導致輸入電流波形紊亂。同時,過小的Cin也不利于對差模干 擾的抑制。第三,乘法器要求有寬廣的線性度。

上面解決的是cos?,而沒有考慮THD的影響。首先,乘法器要有良好的THD;再次,開關頻率要盡可能抬高來降低輸入電流紋波;最后,在電源進線端要選擇電感匹配,這樣才能做到高的PF值。

恒流精度的影響因素和提高手段

根 據公式(3),恒流精度受兩個因素影響:一是每個周期Vcs的峰值檢測。由于芯片內部比較器的延時等因素,真正檢測到最終的峰值難度很大(往往檢測值都要 小于真實的峰值)。這也是影響系統線調整率的主要因素。二是tdis/T的檢測,其關鍵又在于tdis的檢測。tdis的檢測一個是開始點的確定,一個是 結束點的確定。

PT4209中以DET腳超過1.25V為開始點的起始點。這個點和實際的真實開始點略有超前(相當于加進去一個 tdis的小量),正好補償因為Vcs的峰值檢測漏掉的一點峰值。此外,這個上升時間量和Vin+ Vr/sub>大小成正比,所以就算對線調整率有影響也非常有限。另一端,如何判斷tdis時間的結束,無論對于PSR恒壓還是恒流,都是至關重要 的一環。由于真正檢測到該點有一定難度,市面上一般的芯片都只是簡單地采取判斷DET腳過零來近似認為是tdis的結束。好一點的芯片會在內部減去一個預 先設定好的時間,但一旦系統選擇不一樣的參數,則補償的結果不是偏大就是偏小。有些還需要在MOS管DS兩端掛電容或在DET腳對地掛電容來進行補償。

PT4209采用了先進的自適應判斷方法。在輸出二極管關斷后,芯片內部記錄振蕩周期,并將其補回到下一個周期的tdis的計算中。這樣做不僅可以保證精確的采到tdis,系統不需要增加任何元件,也使得芯片對不同系統的適應性更強。

此外,對于PCB的走線,Rcs的地要和芯片地接在同一點;整流橋后端電容、變壓器原邊、MOS管和Rcs四個元件組成的回路要盡可能小;芯片DRV腳、Rdrv和MOS管G極組成的驅動回路也要盡可能短。這樣才能保證Vcs的峰值檢測盡可能準確。

系統效率和啟動時間的影響因素和提高手段

前文已經提到,PT4209采用準諧振開通的方式,在低壓甚至零壓時開通MOS管,極大降低了開關管的開通損耗。實際參數設計時,在保證MOS耐壓安全的前提下,可以盡量提高反射電壓Vr的值,進一步降低高壓輸入時的開關損耗。適當增加RCD snubber(電壓關斷型緩沖器)電路的Vclamp值,減小Rdrv值,也能加快開關速度,降低開關損耗。但該法會惡化系統EMI性能,需要折中考慮。

另 外,由于PT4209這類芯片拓撲結構的固有特點,原邊需要進行PFC。輸入電容較小,抑制輸入交流紋波的任務落在了輸出電容之上,加之對于輸出電壓紋波 有小于5%(一級標準)的要求,輸出電容會選擇的較大。這樣要使上電后不出現UVLO,Vcc電容也要適當加大,而Rst電阻因為效率問題一般要選1M以 上,更加減慢了上電時間。PT4209借鑒了開關電源中常用的加速啟動的方法,上電后強制拉高Vcomp值,啟動時原邊以OCP方式工作。然后,再通過閉 環控制將Vcomp值降到正常值。通過此方法,能夠使得系統在全電壓輸入范圍內,將啟動時間控制在0.5s以內。這樣做在一些特定的系統中,可能會造成 LED啟動過流的現象,但由于人眼的視覺暫留,一般很難被人眼所察覺。同時,系統也可以通過減小Ccomp、增大Vins采樣分壓變比 、增大Cout、降低Vr或將DET腳1.25V時對應的Vout抬高等多種手段,避免過沖的發生。

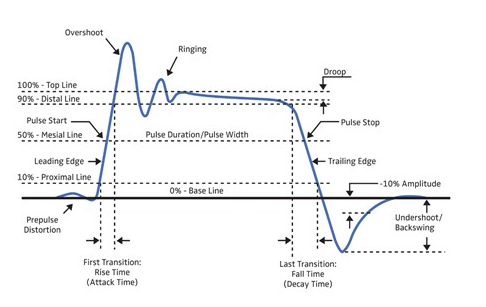

系統測試波形和實驗數據

系統測試波形和實驗數據如圖3所示。實測LED啟動時間小于0.5s,效率高于90%。另外,PT4209還具有PWM調光、模擬調光兩個調光功能,調光信 號從DIM腳輸入,能夠輕松做到1%以下的調光精度,整個調光過程線性度也非常好。如果用戶需要帶可控硅調光的功能,在PT4209的基礎上,華潤矽威公 司又同步推出了帶可控硅調光的芯片PT4208。該芯片所需外圍元件較少,真正做到了無閃爍TRIAC調光。上述兩款芯片的詳細系統設計過程和測試數據可 以參考PT4209、PT4208的芯片手冊和應用說明。

圖3:系統測試波形和實驗數據。

本文小結

本文詳細分析了帶PFC的原邊反饋準諧振芯片PT4209系統設計中的若干難 點,并對于如何提高系統PF值、輸出電流精度及系統效率,做了詳細的理論分析和試驗驗證。從試驗結果可以看出,采用PT4209芯片的LED驅動系統具有 高功率因數(>0.95)、高恒流精度(<±3%)、高效率(>90%)和快速啟動(<0.5s)等諸多優點。該芯片是一款十分 優秀的LED恒流驅動芯片。

電子發燒友App

電子發燒友App

評論