關鍵詞:嵌入式處理器 MPC8250 接入路由器

1 MPC8250簡介

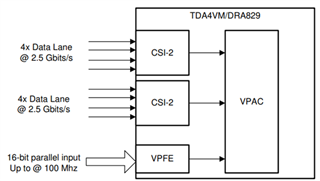

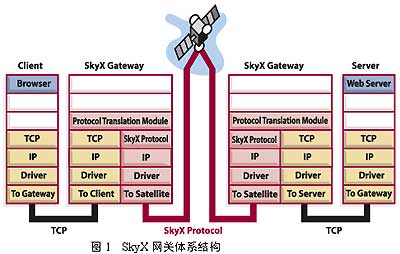

MPC8250是Motorla公司在嵌入式徽順MPC860基礎之上推出的MPC82XX系列微處理器中的一種。MPC82XX系列保留了MPC860的嵌入式PowerPC內(nèi)核和通信處理模塊CPM并存的體系結(jié)構(gòu),同時進一步提高了工作頻率、集成了更多的外圍器件、提供了豐富的總線接口。其中,MPC8250沒有集成在一數(shù)據(jù)通信設備中不常使用、而且較為昂貴的ATM處理模塊,進一步降低了成本。MPC8250的內(nèi)部結(jié)構(gòu)基于PowerQUICC結(jié)構(gòu),主要由PowerPC內(nèi)核、系統(tǒng)接口單元SIU、通信處理單元CPM構(gòu)成。它支持60x總線,其數(shù)據(jù)線為64位,地址線為32位;支持PCI/LOCAL總線,其數(shù)據(jù)線為32位,地址線為32位。內(nèi)核工作時鐘最高300MHz,CPU工作時鐘最高200MHz。內(nèi)部結(jié)構(gòu)如圖1所示。

①PowerPC內(nèi)核:完成中央處理器的功能,執(zhí)行高層程序偌,它與SIU和CPM通過獨立的指令Cache和數(shù)據(jù)Cache通信,通過MMU對存儲器進行管理。

②系統(tǒng)接口單元SIU:包括CPU的復位、中斷控制器、時鐘配置等功能。內(nèi)部包括60x總線控制器、PCI/LOCAL總線到60x總線的橋接器、存儲器控制器、時鐘控制器等。MPC8250的存儲控制器部分集成了SDRAM控制器,通過設置寄存器即可完成與SDRAM的接口配置,與MPC860配置UPM表的方式相比,極大地降低了開發(fā)的復雜度。

③通信處理單元CPU:CPM可與內(nèi)核并行工作,處理通信控制中的底層任務。內(nèi)部包括32位RISC通信控制器、DMA通道、用于內(nèi)部交換數(shù)據(jù)的32KB雙口RAM、中斷控制器、波特率發(fā)生器、計數(shù)器等。CPM部分還集成了4個時分復用TDM接口、3個媒體無關接口MII和非時分復用串行接口NMSI三種物理層接口,它們之間的選擇由串行接口SI模塊控制。CPM部分最主要的功能模塊是它所集成的大量可同時使用的通信控制單元,包括:

*1個多通道通信控制器MCC,可工作于HDLC模式,物理層接口為TDM方式,最多可以同時與4個TDM接口相連;

*3個快速通信控制器FCC,可工作于HDLC、10M/100Mbit/s以太網(wǎng)和透明模式,物理層接口為TDM或MII方式,當物理層工作于TDM方式時,最高可以支持T3/E3速率;

*4個串行通信控制器SCC,可工作于HDLC、UART、同步UART、BISYNC、10Mbit/s以太網(wǎng)、AppleTalk、透明模式,物理層接口為TDM或NMSI方式;

*2個串行管理控制器SMC,可工作于UART或透明方式,物理層接口為TDM或NMSI方式;

*1個I2C控制器;

*1個SPI控制器。

2 MPC8250與MPC860的對比

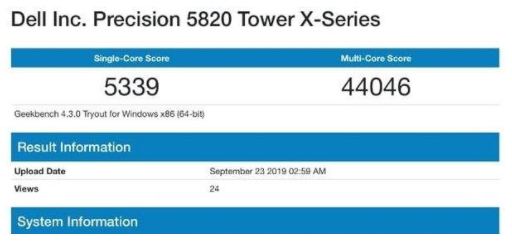

現(xiàn)有的很多寬帶接入產(chǎn)品多是以Motorola公司的PowerQUICC系列CPU MPC860為核心構(gòu)建的。與MPC8250相比,除了通信控制單元類型不夠豐富、存儲控制器的UPM方式開發(fā)難度高等缺點之外,另一個顯著的劣熱是工作時鐘頻率低。這不僅制約了系統(tǒng)的處理能力,也增加了軟件開發(fā)的難度。表1簡要對比了MPC8250與MPC860的特點。

表1 MPC8250與MPC860的對比

| MPC8250 | MPC860 | |

| 內(nèi)核工作時鐘 | 300MHz | 50MHz |

| CPM工作時鐘 | 200MHz | 50MHz |

| 總線數(shù)據(jù)寬度 | 64bit | 32bit |

| PCI總線支持 | 有 | 無 |

| 存儲器控制器個數(shù) | 12 | 8 |

| MCC | 1 | 無 |

| FCC | 3 | 無 |

| SCC | 4 | 4 |

| SMC | 2 | 2 |

3 MPC8250在寬帶接入中的應用

在目前的寬寬帶接入中,一個顯著的特點就是硬件接口和協(xié)議類型均呈現(xiàn)出多樣化、復雜化的特征,這就對寬帶接入產(chǎn)品提出了更高的要求。一方面,要在面積有限的電路板上支持更多類型的接口;另一方面,要處理更多、更復雜的通信協(xié)議。以寬帶執(zhí)著入中常見的接入路由器為例,一般需要提供以下功能:

①對內(nèi)提供2個100Mbit/s以太網(wǎng)接口;

②對外應提供各種類型的廣域網(wǎng)接口模塊;

③支持PPP、PPPoE、LAPB等鏈路層協(xié)議;

④支持IP、IPX等網(wǎng)絡層協(xié)議;

⑤支持RIP、OSPF、BGP等路由協(xié)議;

④支持組插、安全管理、VPN等機制。

可見,接入路由器以及類似的家庭網(wǎng)關、寬帶接入集線路等設備的特點是不僅硬件接口多;而且由于協(xié)議眾多,需要處理器具有相當?shù)奶幚砟芰Α?/p>

MPC8250本身即可通過內(nèi)部集成的FCC支持3個100Mbit/s以太網(wǎng)接口或E1/E3接口,內(nèi)部還集成了PCI總線控制器,因此可以減少使用外圍擴展芯片;而且被減少的外圍擴展芯片:PCI橋芯片和100Mbit/s以太網(wǎng)MAC芯片是硬件設計使用外擴芯片中引腳較多、接口較復雜的芯片。同時MPC8250還提供了4個SCC,可用于提供數(shù)據(jù)速率較低的通信接口,如10Mbit/s以太網(wǎng)接口、E1接口、ISDN PRI/BRI接口、X.25接口等。此外,MPC8250內(nèi)核的工作時鐘和CPM工作時鐘均達到了百MHz級別。可見,將MPC8250用于寬帶接入產(chǎn)品的設計可以充分利用MPC8250的優(yōu)點,提供更為強大的處理能力,并在提高硬件集成度、降低軟件開發(fā)難度的同時降低硬件成本。

4 基于MPC8250的接入路由器設計

根據(jù)上文對接入路由器的功能分析,接入器由器的硬件主要由中央處理器、廣域網(wǎng)接口模塊、局域網(wǎng)(以太網(wǎng))接口模塊、維護、調(diào)試接口模塊、內(nèi)存SDRAM、引導Flash等同部分構(gòu)成。其中:MPC8250可通過內(nèi)部集成的FCC支持2個100Mbit/s以太網(wǎng)接口,由于FCC支持標準的MII接口,因此可以直接與以太網(wǎng)的物理層收發(fā)器相連接;MPC8250內(nèi)部集成了PCI總線控制器,可以用于提供與加密模塊的接口;同時MPC8250仍然保留了4個SCC,可用于提供廣域網(wǎng)接口;由于內(nèi)部的SMC不提供Modem控制信號,因此為了支持遠程撥號維護,擴串口控制芯片;此外,SDRAM、Flash、Bootrom、NVRAM等器件均通過60x總線與MPC8250連接。基于MPC8250的接入路由器內(nèi)部硬件結(jié)構(gòu)如圖2所示。

除MPC8250外各模塊設計說明如下:

①總線驅(qū)動:由于MPC8250的總線驅(qū)動能力有限,而60x總線上器件較多,除SDRAM與MPC8250直接相連外,其它器件與MPC8250的物理距離均較遠,因此采用74LVC245提供數(shù)據(jù)總線的驅(qū)動,采用74LVTH244提供地址總線的驅(qū)動,采用74LVTH244為走線較長的總線控制信號(部分片選、R/W、OE等)提供總線驅(qū)動。

②廣域網(wǎng)接口卡:主要完成電平轉(zhuǎn)換功能,以PCMCIA插卡的形式提供。其中SCC1、SCC2對應插卡1,SCC3、SCC4對應插卡2,插卡可以是多協(xié)議串口卡、ISDN PRI接口卡、E1接口卡等。如果是多協(xié)議串口卡則一塊插卡提供兩路廣域網(wǎng)接口,即SCC1、SCC2通過插卡1分別對應一路廣域網(wǎng)接口。此時SCC1、SCC2的物理層接口均應工作在NMSI方式;如果是ISDN PRI或E1/T1接口卡則一塊插卡提供一路擴域網(wǎng)接口,此時SCC1、SCC2的物理層接口均應工作在TDM方式。

③網(wǎng)絡加密模塊:以PMC插卡形式提供,提供用于VPN的加密/解密功能。

④以太網(wǎng)物理層接口芯片:完成以太網(wǎng)線路側(cè)與以太網(wǎng)MAC收發(fā)器之間的電平轉(zhuǎn)換、保護等功能,遵循與MAC層之間的MII接口規(guī)范,與MPC8250的FCC通過MII接口直接相連。

⑤串口通信芯片:由于MPC8250內(nèi)部SMC接口的UART方式?jīng)]有Modem控制信號,無法支持遠程撥號連接,因此,需要擴展串口通信芯片,使用雙路UART收發(fā)器實現(xiàn)。常見的雙路UART收發(fā)器均支持硬件流控,內(nèi)部帶有FIFO的緩存,支持DMA方式。兩路UART中:一路用做本地維護串口同時在開發(fā)過程中用做調(diào)試串口;一路用做遠程維護串口。串口通信芯片與MPC8250以60x總線相連。

⑥SDRAM:用于存放用戶的數(shù)據(jù)和代碼,為程序的運行和保存臨時文件提供空間。采用商用的168引腳的64/128Mbyte內(nèi)存條,與MPC8259以60x總線相連。數(shù)據(jù)寬度為64位。MPC825提供了SDRAM控制器,與MPC860的UPM表編程相比,只需進行寄存器的設置,降低了開發(fā)的難度。

⑦Flash:用于存儲操作系統(tǒng)內(nèi)核、文件系統(tǒng)映像和用戶程序文件。與MPC8250以60x總線相連,設計為類似SDRAM內(nèi)存條的Flash插卡形式,可支持8/16/32MB不同大小的Flash插卡。數(shù)據(jù)寬度為32位。

⑧Bootrom:存儲操作系統(tǒng)內(nèi)的引導程序與MPC8250以60x總線相連。Bootrom實際上也是一塊Flash芯片,大小為512KB,數(shù)據(jù)寬度為8位。

⑨NVRAM:保存系統(tǒng)和用戶的配置文件,與MPC8250以60x總線相連,大小為64/128KB。

⑩EPLD:給出必須的邏輯控制信號、時序調(diào)整信號、譯碼片選信號等,要用Altera、Xilinx等公司的產(chǎn)品。

5 MPC8250與Flash的接口設計

在接入路由器的設計中,要求兼容8/16/32MB不同大小的Flash插卡,即在驅(qū)動程序中應能檢測出不同大小的Flash插卡,而Flash插槽的數(shù)據(jù)總線寬度為32位。因此使用4片16位的Flash,以存儲器擴展的方式完成MPC8250與Flash的接口設計,如圖3所示。

Chip1、Chip3、Chip2、Chip4為4片F(xiàn)lash芯片。其中Chip1與Chip3、Chip2與Chip4分別對應數(shù)據(jù)線的低16位和高16位,Chip1與Chip2、Chip3與Chip4分別構(gòu)成2個存儲器Bank,對應MPC8250的2個片選CS3和CS4。由于構(gòu)成的是32位Flash插卡,最大32MB,因此使用MPC8250的地址線A[8~29]與Flash插槽的A[21~0]相連,假設Flash的地址空間為0xF0000000~0xf1ffffff,那么當分別使用8/16/32MB大小的Flash插卡時,以INTEL的28F系列Flash為例,每個存儲器Bank的地址空間分配如表2所列。

表2 Flash地址空間的分配

| Flash插卡大小 | 芯片使用 | 芯片型號 | Bank1地址空間 | Bank2地址空間 |

| 8MB | 4×2MB | 28F160 | 0xf0000000~0xf03fffff | 0xf1000000~0xf13fffff |

| 16MB | 4×4MB | 28F320 | 0xf0000000~0xf07fffff | 0xf1000000~0xf17fffff |

| 32MB | 4×8MB | 28F640 | 0xf0000000~0xf0ffffff | 0xf1000000~0x0xf1ffffff |

在驅(qū)動程序的初始化過程中,可分別在2個存儲器Bank的起始地址0xf0000000和0xf1000000處讀取芯片的制造商標識和芯片標識,以此確定所使用的Flash芯片,從而確定Flash插卡的大小,然后即可按上表確定的地址空間使用Flash,這樣就實現(xiàn)了對Flash插卡大小的自動檢測。而且如果在某一個存儲器Bank的高/低16位讀出了不合法的制造商標識或芯片標識,即可認為此芯片異常,在開機自檢時報告。

結(jié)語

從以上的設計不難看出,MPC8250用于寬帶接入產(chǎn)品的設計具有顯著的優(yōu)點:

芯片數(shù)量少,芯片間接口少,前期設計和后續(xù)開發(fā)的復雜度低;

芯片數(shù)量減少降低了硬件成本;

MPC8250的工作時鐘最高達到300MHz,處理機能力顯著提高。

電子發(fā)燒友App

電子發(fā)燒友App

評論