【原書名】 High-Speed Digital System Design: A Handbook of Interconnect Theory and Design Practices [原書信息]

【原出版社】 John Wiley & Sons,Inc.

【作者】 (美)Stephen H.Hall,Garrett W.Hall, James A.McCall

【譯者】 伍微等

【叢書名】 電子與電氣工程叢書

【出版社】 機械工業出版社

【書號】 7-111-16822-4

【開本】 16開 【頁碼】 252

【出版日期】 2005-8-1 【版次】 1-1

市場價: ¥33.00

《高速數字系統設計:互連理論和設計實踐手冊》

數字系統設計員必須面對當今微處理器運行速度不斷增加所帶來的挑戰,因此,理解高速互連現象是不可或缺的。本書基于硬件平臺,將從基本的傳輸線理論到數字時序分析,再到高速測量技術等概念,逐一為讀者進行高速數字系統設計說明并將通俗易懂的原理解釋與大量實用問題解決方案結合起來,為當前的數字系統設計技術提供實踐指導。本書由3位Intel高級工程師編寫,詳細解釋常被忽略的有關數字總線上高頻效應的主題,介紹多種成熟技術和應用實例。

本書特點

●從數字角度詳細介紹基本傳輸線理論。

●理論層面的理解有助于讀者擺脫當前實踐應用的局限,進而能夠解決本書中未涉及的問題。

●書中理論適用于任何高速數字系統。

●書中涵蓋的所有方法都已經應用于實際數字產品,且這些產品的大批量生產和銷售已經獲得成功。

http://www.china-pub.com/computers/common/info.asp?id=26449

中國PCB論壇網斑竹winworm評價:

首先肯定一下,高速數字系統設計中的時序設計章節是所有高速數字設計書籍中講得最清楚的,盡管Howard在書中也講到了時序,但沒有這本書中講得好。

但是,我覺得時序設計可以簡化,沒有必要搞這么復雜,很多時候,盡管已經理解了,時序公式還是記不住,尤其是哪個量應該加,哪個量應該減,而且時序系統不止文中所說的2種類型,還有其它的一些變型,關鍵是要把握好時序設計的基本點,抓住建立時間和保持時間,剩下的事情都好辦。

時序設計應該有一個好的設計工具,而不是靠一個簡單的時序計算表。

本書目錄:

第1章互連設計的重要性1

1?1基礎1

1?2過去和未來3

第2章理想傳輸線基本原理5

2?1PCB或MCM上的傳輸線結構5

2?2波的傳播6

2?3傳輸線參數6

2?3?1特征阻抗7

2?3?2傳播速度、時間和距離9

2?3?3SPICE仿真中的等效電路模型10

2?4發送初始波和傳輸線反射12

2?4?1初始電波12

2?4?2多次反射14

2?4?3上升時間對反射的影響20

2?4?4電抗性負載的反射21

2?4?5消除反射的匹配方案22

2?5補充示例25

2?5?1問題25

2?5?2目標25

2?5?3計算PCB的橫截面幾何結構25

2?5?4計算傳輸延遲26

2?5?5確定接收端波形27

2?5?6創建等效電路27

第3章串擾29

3?1互感和互容29

3?2電感矩陣和電容矩陣29

3?3場仿真器30

3?4串擾感應噪聲31

3?5用等效電路模型仿真串擾35

3?6串擾感應延遲時間和信號完整性變化36

3?6?1開關模式對傳輸線性能的影響36

3?6?2使用單線等效模型模擬多導線系統中的走線40

3?7串擾引起的阻抗變化41

3?8奇、偶模傳輸線對的匹配43

3?8?1Pi型匹配網絡44

3?8?2T型匹配網絡45

3?9串擾最小化設計45

3?10補充示例46

3?10?1問題46

3?10?2目標47

3?10?3計算串擾引起的阻抗變化和傳播速度變化的最大值47

3?10?4判斷串擾是否會導致誤觸發48

第4章非理想互連問題51

4?1傳輸線損耗51

4?1?1導線直流損耗51

4?1?2介質直流損耗52

4?1?3趨膚效應52

4?1?4與頻率相關的介電損耗60

4?2介電常數的變化62

4?3走線彎曲63

4?4符號間干擾65

4?590°轉角效應67

4?6拓撲效應68

第5章連接器、封裝和過孔71

5?1過孔71

5?2連接器72

5?2?1串聯電感73

5?2?2并聯電容73

5?2?3連接器串擾73

5?2?4電感耦合引起的連接器引腳場效應74

5?2?5EMI76

5?2?6連接器設計指南76

5?3芯片封裝78

5?3?1常見的封裝類型78

5?3?2創建封裝模型81

5?3?3封裝的影響84

5?3?4最佳引腳布局88

第6章非理想回路、同步開關噪聲和功率傳輸91

6?1非理想電流回路91

6?1?1最小電感通路91

6?1?2信號通過地槽92

6?1?3切換參考面的信號94

6?1?4以電源或地為參考面的信號95

6?1?5其他非理想回路98

6?1?6差分信號98

6?2本地功率傳輸網絡99

6?2?1高速I/O設計中求解本地去耦需求100

6?2?2系統級功率傳輸102

6?2?3選擇去耦電容104

6?2?4功率傳輸系統的頻率響應105

6?3SSO/SSN105

第7章緩沖器建模109

7?1模型分類109

7?2基本的CMOS輸出緩沖器110

7?2?1基本操作110

7?2?2為CMOS緩沖器建立線性模型114

7?2?3為CMOS緩沖器建立行為模型119

7?3在飽和區中工作的輸出緩沖器121

7?4小結122

第8章數字時序分析123

8?1公用時鐘時序123

8?2源同步時序127

8?2?1源同步時序方程128

8?2?2根據眼圖推導源同步時序方程131

8?2?3其他源同步方案131

8?3其他總線信號傳輸技術132

8?3?1時鐘伴隨133

8?3?2時鐘嵌入133

第9章設計方法學135

9?1時序135

9?1?1最差情況時序表136

9?1?2統計時序表138

9?2時序度量、信號質量度量和測試負載140

9?2?1參考電壓的不確定度140

9?2?2對參考負載進行仿真140

9?2?3延遲時間143

9?2?4延遲時間偏差144

9?2?5信號完整性145

9?3設計優化147

9?3?1圖紙分析147

9?3?2制板分析148

9?4靈敏度分析149

9?4?1初步的趨勢分析和顯著性分析150

9?4?2有序參數掃描154

9?4?3解空間求解的第1階段155

9?4?4解空間求解的第2階段157

9?4?5解空間求解的第3階段159

9?5設計指南159

9?6參數提取160

9?7在設計系統時應遵循的通用經驗方法160

第10章輻射規范和系統噪聲最小化163

10?1FCC輻射規范163

10?2輻射的物理原理164

10?2?1差模輻射164

10?2?2共模輻射168

10?2?3波阻抗171

10?3去耦與扼流172

10?3?1系統級高頻去耦173

10?3?2扼流電纜、本地電源平面和本地地平面176

10?3?3低頻去耦與地平面隔離182

10?4補充的PCB設計準則、封裝須知與引腳布局183

10?4?1高速器件和高速走線的布局183

10?4?2串擾183

10?4?3引腳布局和封裝選擇184

10?5機箱設計184

10?5?1電磁屏蔽基本知識184

10?5?2孔徑186

10?5?3諧振189

10?6時鐘頻譜擴展190

第11章高速測量技術193

11?1數字示波器193

11?1?1帶寬193

11?1?2采樣194

11?1?3其他效應196

11?1?4統計197

11?2時域反射計197

11?2?1TDR理論198

11?2?2測量要素199

11?3TDR的精度201

11?3?1入射寄生效應202

11?3?2探針類型203

11?3?3反射204

11?3?4接口傳輸損耗204

11?3?5電纜損耗204

11?3?6幅度漂移誤差205

11?4阻抗測量205

11?4?1阻抗的精確測量205

11?4?2TDR阻抗分析中的測量區域206

11?5奇模阻抗和偶模阻抗207

11?6串擾噪聲208

11?7傳播速度208

11?7?1長度差分法209

11?7?2Y截距法209

11?7?3TDT法209

11?8矢量網絡分析儀210

11?8?1S參數簡介211

11?8?2儀器211

11?8?3單端口測量(Zo、L、C)212

11?8?4雙端口測量(Td、衰減、串擾)214

11?8?5校準217

11?8?6單端口測量校準218

11?8?7雙端口測量校準218

11?8?8校準驗證219

附錄A阻抗公式的其他特性221

附錄BGTL電流模式分析223

附錄C數字信號的頻域分量229

附錄D有用的S參數變換231

附錄E分貝的定義235

附錄FFCC輻射限制237

參考書目239

索引241

- 高速數字(8300)

- 實踐手冊(5850)

相關推薦

高速數字系統設計——互連理論和設計實踐手冊

0

0RA6快速設計指南 [完結] 一般布線實踐 (下)高速信號設計注意事項

655

655探索開源創新理論|2023開放原子全球開源峰會開源創新理論與實踐分論壇成功召開

472

472探索開源創新理論|2023 開放原子全球開源峰會開源創新理論與實踐分論壇成功召開

300

300

展望開源產業與數字經濟未來|2023 開放原子全球開源峰會開源創新理論與實踐分論壇即將啟幕

189

189

展望開源產業與數字經濟未來|2023開放原子全球開源峰會開源創新理論與實踐分論壇即將啟幕

204

204

如何區分高速信號和低速信號

4587

4587高速PCB布線實踐指南介紹

11

112020年大連理工大學《單片機原理及應用》期末試卷

31

31高速數字電路設計中的信號反射抑制綜述

15

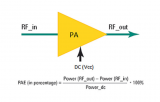

15解讀放大器負載對PAE的影響-從理論到實踐

2377

2377

高速數字系統設計互連理論和設計實踐手冊PDF電子書免費下載

49

49高速電路設計實踐的電子教材免費下載

85

85高速PCB設計中高速信號與高速PCB設計須知

9850

9850

高速電路設計實踐PDF電子教材免費下載

185

185高數據速率數字互連解決方案面向高速背板應用

2891

2891變頻器的故障分析和解決 實踐檢驗、理論知識及維修水平

3709

3709

高速電路設計實踐PDF電子書免費下載

373

373探討高速信號完整性理論和PCB仿真設計

1215

1215

學好電子技術關鍵是理論知識和實踐動手能力

6525

6525高速電路信號完整性分析與設計—高速信號完整性的基本理論

1536

1536現代通信的理論與實踐_吉家騮

95

95高速數字設計_英文版

130

130高速數字系統的互連完整性和散熱問題

843

843

高速數字設計_沈立譯

52

52應用于光互連的高速誤碼儀的設計

28

28數字邏輯電路教學實踐探討

60

60高速互連 (第9版本)

20

20基于RapidIO和存儲映射的高速互連網絡

20

20高速接口互連

19

19高速互連自測試技術的原理與實現

15

15思想政治理論課開展研究性教學的實踐探索

7

7高速數字設計

286

286高速PCB互連設計中的測試技術

535

535

電子發燒友App

電子發燒友App

評論