新型的頻率數顯電路SC3610D集分頻器、頻率計數、顯示驅動于一身,只需很少的外圍元件即可工作,其顯示頻率高達100MHz以上。現在被廣泛用于袖珍頻率計和調頻收音機頻率顯示等領域。

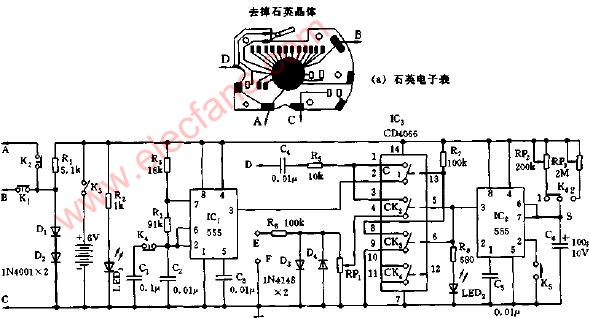

SC3610D采用平板雙列軟封裝,其第{1}引腳無顯示標記,故請參考圖2外形尺寸及引腳順序1。該芯片典型工作電壓為3V,應用電路見圖1。第{1}至{16}腳為液晶顯示信號輸出端;{17}、{18}為37.368Hz標準時基信號源;第{19}、{25}、{31}、{32}、{34}為接地端;{21}、{22}為定時鬧鈴調節控制端;{23}、{24}為時鐘調節,同時按下S1和點擊S2、S3可調整顯示時間;{26}、{29}為頻率計電源供應端;{27}、{30}、{33}懸空;{28}腳為定時鬧鈴音頻輸出端,外接低放使喇叭發聲;{35}腳是高頻信號檢測輸入端,內有分頻器、計數閘門、頻率計數等電路,一般是將高頻信號緩沖放大之后再輸入到該引腳以防信號過載;{36}腳系時鐘數顯電路供電端,當S4斷開時IC工作于時鐘顯示狀態,閉合S4為頻率數顯狀態,同時時鐘被迫停顯。該IC可接收音機本振作頻率顯示。

由于此IC采用軟封裝,所以在焊接時速度要盡量快,以免敷銅引線脫落致使電路損壞。

- 組圖單片(6125)

- 610D(5695)

相關推薦

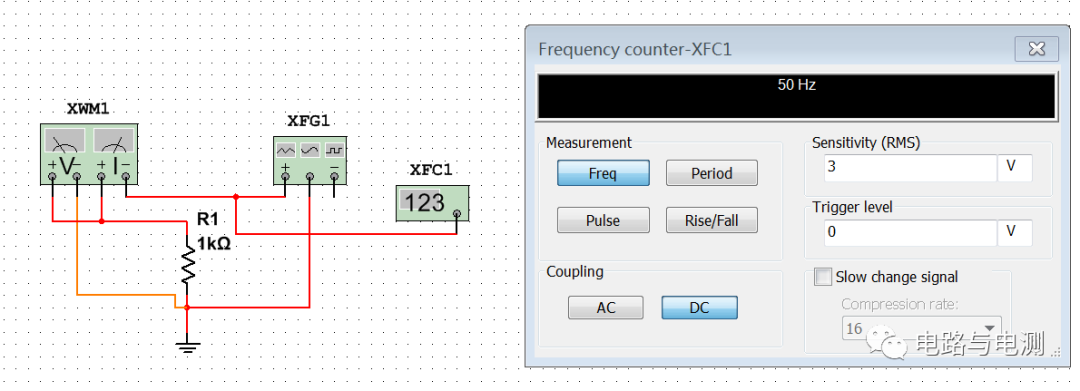

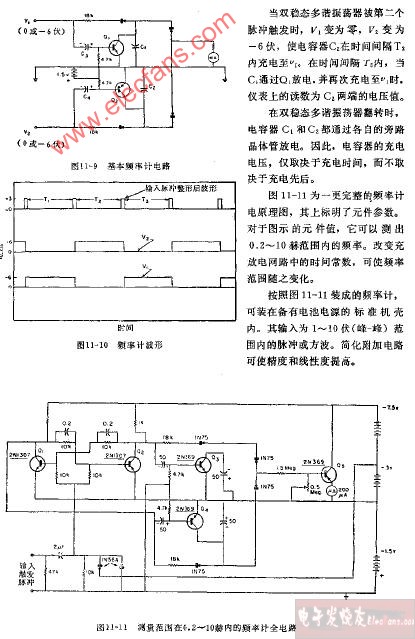

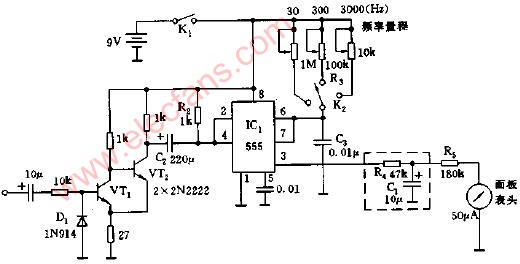

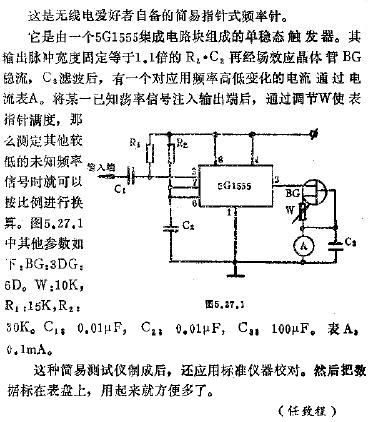

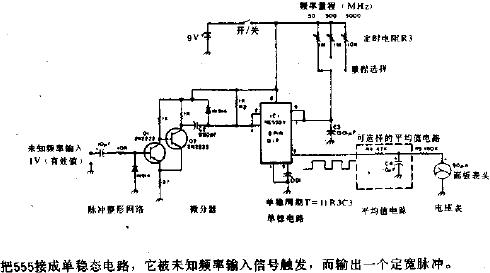

分享一個簡單的模擬頻率計電路

848

848

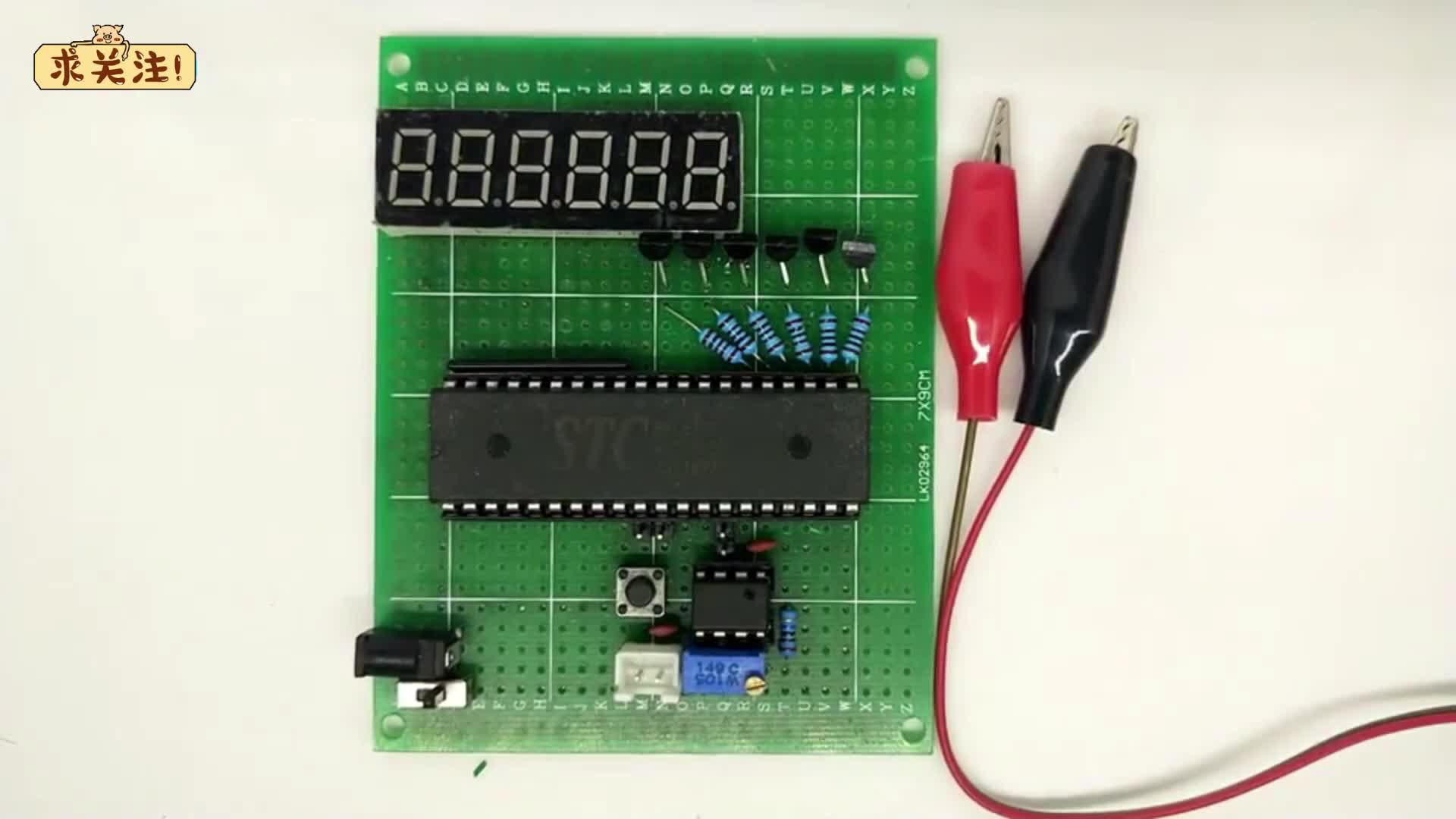

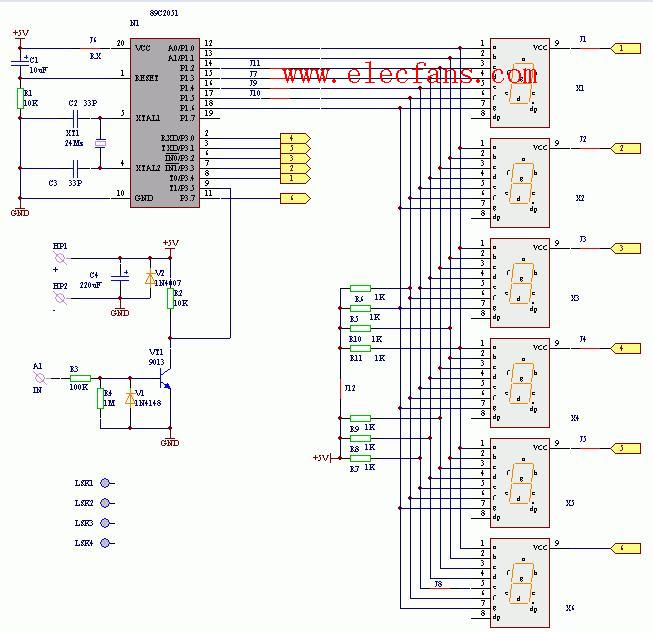

基于51單片機的頻率計仿真方案原理圖

11

11基于單片機的頻率計設計 單片機 仿真 頻率計

57

57基于單片機的數字頻率計設計

31

31基于51單片機的數字頻率計的設計講解

85

85一個智能頻率計的設計與制作的proteus仿真電路圖和程序與工程文件

20

20正點原子開拓者FPGA:頻率計實驗

2925

2925

使用51單片機設計的數字頻率計源碼和原理圖資料免費下載

54

54頻率計工作原理

1240

1240

基于verilog語言的數字頻率計設計

74

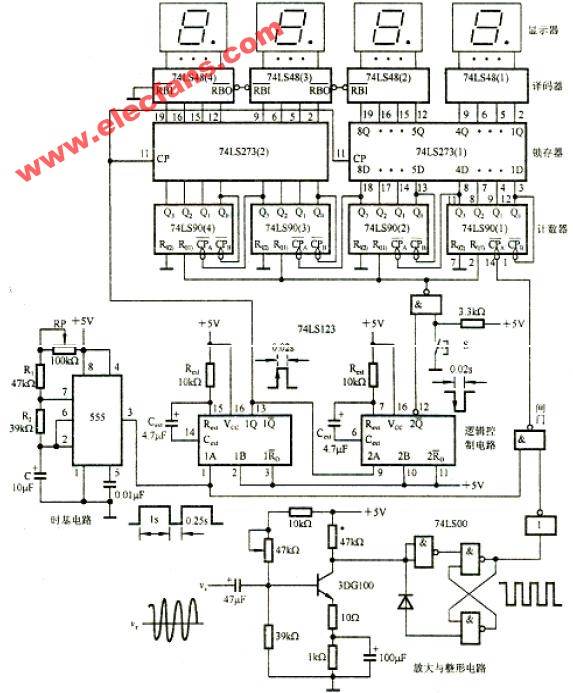

74數字頻率計的制作

142

142基于AT89C51的頻率計硬件電路圖

4175

4175

基于單片機的頻率計的C語言源代碼

16868

16868

基于單片機的數字頻率計電路圖

4914

4914

超高頻數字頻率計的設計

100

100基于單片機的數字頻率計的方案

6181

6181

數字頻率計測頻率的基本原理

505

505基于單片機的頻率計設計

612

612基于單片機和CPLD的數字頻率計的設計

992

992 電子發燒友App

電子發燒友App

評論