a) 什么是Setup 和Holdup時間?

建立時間(setup time)是指在觸發器的時鐘信號上升沿到來以前,數據穩定不變的時間,如果建立時間不夠,數據將不能在這個時鐘上升沿被打入觸發器;保持時間(hold time)是指在觸發器的時鐘信號上升沿到來以后,數據穩定不變的時間, 如果保持時間不夠,數據同樣不能被打入觸發器。

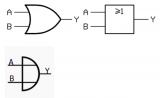

b) 什么是競爭與冒險現象?怎樣判斷?如何消除?

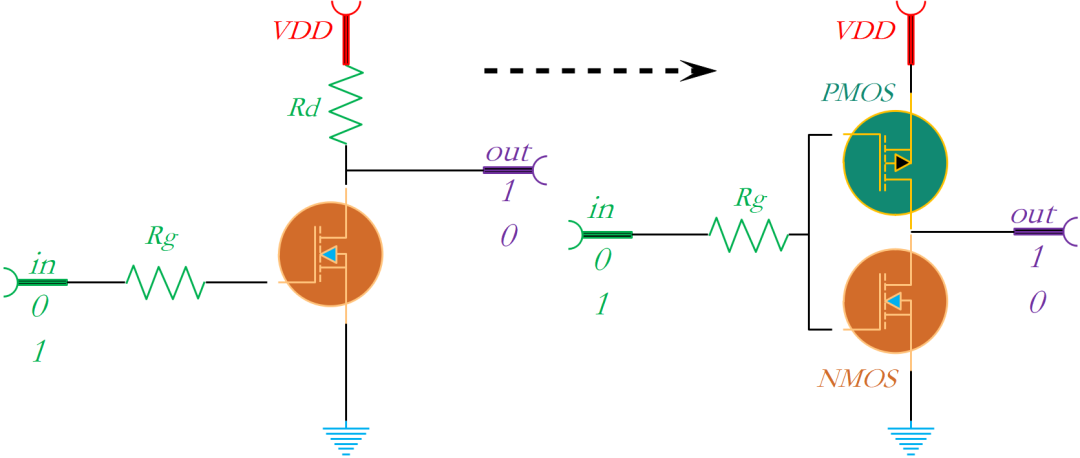

信號在FPGA器件內部通過連線和邏輯單元時,都有一定的延時。延時的大小與連線的長短和邏輯單元的數目有關,同時還受器件的制造工藝、工作電壓、溫度等條件的影響。信號的高低電平轉換也需要一定的過渡時間。由于存在這兩方面因素,多路信號的電平值發生變化時,在信號變化的瞬間,組合邏輯的輸出有先后順序,并不是同時變化,往往會出現一些不正確的尖峰信號,這些尖峰信號稱為"毛刺"。如果一個組合邏輯電路中有"毛刺"出現,就說明該電路存在"冒險"。用D觸發器,格雷碼計數器,同步電路等優秀的設計方案可以消除。

c) 請畫出用D觸發器實現2倍分頻的邏輯電路?

就是把D觸發器的輸出端加非門接到D端。

d) 什么是"線與"邏輯,要實現它,在硬件特性上有什么具體要求?

將幾個OC門結構與非門輸出并聯,當每個OC門輸出為高電平時,總輸出才為高,這種連接方式稱為線與。

e) 什么是同步邏輯和異步邏輯?

整個設計中只有一個全局時鐘成為同步邏輯。

多時鐘系統邏輯設計成為異步邏輯。

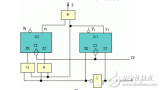

f) 請畫出微機接口電路中,典型的輸入設備與微機接口邏輯示意圖(數據接口、控制接口、所存器/緩沖器)。

是不是結構圖?

g) 你知道那些常用邏輯電平?TTL與COMS電平可以直接互連嗎?

TTL,cmos,不能直連

LVDS:LVDS(Low Voltage Differential Signal)即低電壓差分信號,LVDS接口又稱RS644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。

ECL:(EmitterCoupled Logic)即射極耦合邏輯,是帶有射隨輸出結構的典型輸入輸出接口電路

CML: CML電平是所有高速數據接口中最簡單的一種。其輸入和輸出是匹配好的,減少了外圍器件,適合于更高頻段工作。

什么是同步邏輯和異步邏輯?

相關推薦

用邏輯筆測量信號的邏輯狀態屬于?

用邏輯筆測量信號的邏輯狀態屬于?? 信號的邏輯狀態是指該信號所表達的信息在邏輯上的真假性質,即1或0的狀態。在數字電路設計中,邏輯狀態是非常重要的概念,因為只有正確地確定信號的邏輯狀態,才能正確地

2023-09-19 17:16:11 110

110

110

110FPGA學習-異步復位,同步釋放

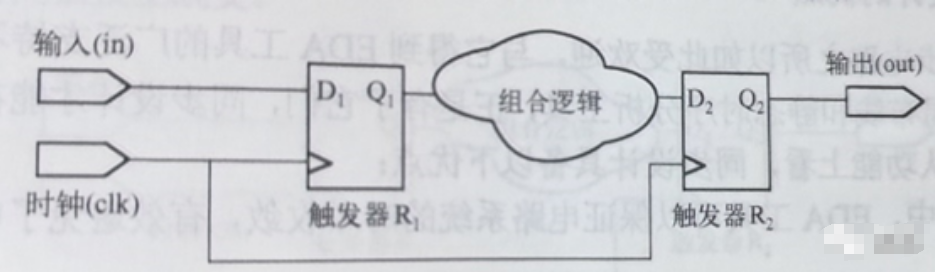

點擊上方 藍字 關注我們 系統的復位對于系統穩定工作至關重要,最佳的復位方式為:異步復位,同步釋放。以下是轉載博客,原文標題及鏈接如下: 復位最佳方式:異步復位,同步釋放 異步復位; 異步

2023-09-09 14:15:01 124

124

124

124

異步邏輯器件之反相器、緩沖器(驅動器)和收發器

引言:在異步邏輯器件中,信號不與時鐘信號同步,或者說該信號壓根就沒有對位的時鐘信號。本節簡述基本的異步邏輯--->1位拓撲和多位拓撲的緩沖器、反相器、驅動器和收發器。

2023-09-04 15:59:03 356

356

356

356

soc中的組合邏輯和時序邏輯應用說明

芯片設計是現代電子設備的重要組成部分,其中組合邏輯和時序邏輯是芯片設計中非常重要的概念。組合邏輯和時序邏輯的設計對于構建復雜的電路系統至關重要。

2023-08-30 09:32:15 511

511

511

511同步電路與異步電路有何區別

同步電路與異步電路有何區別 同步電路和異步電路是數字電路中兩種類型的電路,兩種電路在功能、結構、時序要求等方面都存在差異。同步電路和異步電路分別適用于不同類型的應用場景,因此在設計數字電路時要根據

2023-08-27 16:57:02 1852

1852

1852

1852Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

針對異步復位、同步釋放,一直沒搞明白在使用同步化以后的復位信號時,到底是使用同步復位還是異步復位?

2023-06-21 09:59:15 277

277

277

277

數字邏輯電路下載

;nbsp; 集成同步計數器 5.3 異步計數器 5.3.1 異步計數器分析 5.3.2

2008-05-15 21:57:28

時序邏輯電路設計之同步計數器

時序電路的考察主要涉及分析與設計兩個部分,上文介紹了時序邏輯電路的一些分析方法,重點介紹了同步時序電路分析的步驟與注意事項。 本文就時序邏輯電路設計的相關問題進行討論,重點介紹時序邏輯電路的核心部分——計數器。

2023-05-22 17:01:29 680

680

680

680

為什么在Verilog HDL設計中一定要用同步而不能用異步時序邏輯?

同步時序邏輯是指表示狀態的寄存器組的值只可能在唯一確定的觸發條件發生時刻改變。只能由時鐘的正跳沿或負跳沿觸發的狀態機就是一例。always @(posedge clock) 就是一個同步時序邏輯

2023-03-29 17:40:28 346

346

346

346FPGA入門之功能描述-時序邏輯

時序邏輯的代碼一般有兩種: 同步復位的時序邏輯和異步復位的時序邏輯。在同步復位的時序邏輯中復位不是立即有效,而在時鐘上升沿時復位才有效。 其代碼結構如下:

2023-03-21 10:47:07 238

238

238

238FPGA中何時用組合邏輯或時序邏輯

數字邏輯電路分為組合邏輯電路和時序邏輯電路。時序邏輯電路是由組合邏輯電路和時序邏輯器件構成(觸發器),即數字邏輯電路是由組合邏輯和時序邏輯器件構成。

2023-03-21 09:49:49 258

258

258

258可編程邏輯器件有哪些?什么是同步邏輯和異步邏輯?

在組合邏輯電路中,由于門電路的輸入信號經過的通路不盡相同,所產生的延時也就會不同,從而導致到達該門的時間不一致,我們把這種現象叫做競爭。由于競爭而在電路輸出端可能產生尖峰脈沖或毛刺的現象叫冒險。

2022-12-09 09:23:31 524

524

524

524FPGA之組合邏輯與時序邏輯、同步邏輯與異步邏輯的概念

數字電路根據邏輯功能的不同特點,可以分成兩大類:一類叫做組合邏輯電路,簡稱組合電路或組合邏輯;另一類叫做時序邏輯電路,簡稱時序電路或時序邏輯。

2022-12-01 09:04:04 336

336

336

336Verilog時序邏輯中同步計數器的功能和應用

沒有任何寄存器邏輯,RTL設計是不完整的。RTL是寄存器傳輸級或邏輯,用于描述依賴于當前輸入和過去輸出的數字邏輯。

2022-03-15 11:06:03 2368

2368

2368

2368【FPGA】異步復位,同步釋放的理解

異步復位,同步釋放的理解目錄目錄 同步復位和異步復位 異步復位 同步復位 那么同步復位和異步復位到底孰優孰劣呢? 異步復位、同步釋放 問題1 問題2 問題3 問題4 問題5 參考資料同步

2022-01-17 12:53:57 4

4

4

4數字IC設計工程師筆試面試經典100題-有答案

轉自知乎答主ictown_數字IC設計工程師筆試面試經典100題-有答案-陳恩1:什么是同步邏輯和異步邏輯?(漢王)同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。同步

2021-11-06 10:36:00 19

19

19

19數字IC設計工程師筆試面試經典100題

本文來自芯社區,謝謝。1:什么是同步邏輯和異步邏輯? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 同步時序邏輯電路的特點:各觸發器的時鐘端全部連接在一起,并接在系統

2021-11-06 10:21:02 4

4

4

4淺析數字邏輯電路之邏輯門或邏輯

上篇文章我們講解了與邏輯, 緩沖器和非門只差一個圈嗎? 而與之對應的就是或邏輯,在數字電路中與、或、非為三大基礎邏輯門電路,其后續的與非、或非、同或、異或,都是建立在基礎邏輯門電路的基礎上邊。 那么

2021-10-29 11:09:43 7163

7163

7163

7163

簡述CDC當中最典型錯誤案例

一、主要概念 同步邏輯和異步邏輯:時鐘域為由單個時鐘或具有固定相位關系的時鐘驅動的設計部分。也就是說,在一個模塊中一個時鐘和他的翻轉或者分頻時鐘認為是相同的時鐘域,其所驅動的邏輯是同步邏輯。在一個

2021-04-12 16:47:53 8045

8045

8045

8045

什么是同步邏輯和異步邏輯?同步電路和異步電路的區別是什么?

同步電路是由時序電路(寄存器和各種觸發器)和組合邏輯電路構成的電路,其所有操作都是在嚴格的時鐘控制下完成的。這些時序電路共享同一個時鐘CLK,而所有的狀態變化都是在時鐘的上升沿(或下降沿)完成的。

2021-01-04 10:53:37 13650

13650

13650

13650數字電路設計之同步時序邏輯電路

了解嗎? (1)純組合邏輯電路的缺點在哪? (3)純組合邏輯電路完成不了什么功能? (2)為什么需要時鐘和寄存器呢? 帶著這三個疑問我們來認識一下時序邏輯電路。 二. 同步時序邏輯電路的作用 1. 時序邏輯電路對于組合邏輯的毛刺具有容忍度,

2020-12-25 14:39:28 3607

3607

3607

3607

異步和同步電路的區別 同步時序設計規則

產生毛刺,且易受環境的影響,不利于器件的移植; 同步電路 1. 電路的核心邏輯是由各種各樣的觸發器實現的,所以比較容易使用寄存器的異步復位/置位端,以使整個電路有一個確定的初始狀態; 2. 整個電路是由時鐘沿驅動的; 3. 以觸發器為主體的同步時序電

2020-12-05 11:53:41 9613

9613

9613

9613FPGA設計中涉及的10個知識點

1、什么是同步邏輯和異步邏輯? 同步時序邏輯電路的特點:電路中所有的觸發器都是與同一個時鐘或者該時鐘的衍生時鐘驅動,而且當時鐘脈沖到來時,電路的狀態才能改變。改變后的狀態將一直保持到下 一個時鐘脈沖

2020-11-19 15:13:15 1214

1214

1214

1214

IC設計中同步復位與異步復位的區別

1、什么是同步邏輯和異步邏輯,同步電路和異步電路的區別是什么? 同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。 電路設計可分類為同步電路和異步電路設計。同步電路利用

2020-11-09 14:58:34 8729

8729

8729

8729FPGA的經典面試題和解答方法合集

1:什么是同步邏輯和異步邏輯?(漢王)

同步邏輯是時鐘之間有固定的因果關系。異步邏輯是各時鐘之間沒有固定的因果關系。答案應該與上面問題一致〔補充〕:同步時序邏輯電路的特點:各觸發器的時鐘端全部連接

2020-09-04 17:18:30 5

5

5

5如何設計轉換映射指導成功的異步狀態機

雖然ASIC公司和“良好的工程實踐”強調同步設計技術,但時鐘速度的增加使用速度高達50至200 MHz,這迫使設計人員實施異步邏輯電路。不幸的是,雖然大多數數字設計工程師都熟悉組合和同步時序邏輯

2019-08-08 11:11:42 2447

2447

2447

2447

Xilinx FPGA的同步復位和異步復位

對于xilinx 7系列的FPGA而言,flip-flop支持高有效的異步復/置位和同步復位/置位。對普通邏輯設計,同步復位和異步復位沒有區別,當然由于器件內部信號均為高有效,因此推薦使用高有效的控制信號,最好使用高有效的同步復位。輸入復位信號的低有效在頂層放置反相器可以被吸收到IOB中。

2018-07-13 09:31:00 5911

5911

5911

5911如何區分同步復位和異步復位?

同步復位,何時采用異步復位;2. 復位電路是用來干嘛的;3. 激勵和響應的分析(單拍潛伏期)是否適用與復位邏輯。 1. 電路中,何時采用同步或異步,取決與設計者,取決于當前設計電路的需要。一般而言:高速邏輯應該采用同步復位,

2018-06-11 15:15:11 6087

6087

6087

6087時序邏輯電路分析有幾個步驟(同步時序邏輯電路的分析方法)

分析時序邏輯電路也就是找出該時序邏輯電路的邏輯功能,即找出時序邏輯電路的狀態和輸出變量在輸入變量和時鐘信號作用下的變化規律。上面講過的時序邏輯電路的驅動方程、狀態方程和輸出方程就全面地描述了時序邏輯電路的邏輯功能。

2018-01-30 18:55:32 120321

120321

120321

120321

什么是同步邏輯和異步邏輯,同步電路和異步電路的區別

異步電路:主要是組合邏輯電路,用于產生地址譯碼器、FIFO或RAM的讀寫控制信號脈沖,但它同時也用在時序電路中,此時它沒有統一的時鐘,狀態變化的時刻是不穩定的,通常輸入信號只在電路處于穩定狀態時才

2017-11-30 09:35:40 30261

30261

30261

30261

UART邏輯實現高速異步串行通信

介紹一種利用cPLD實現高速異步串行通信的方法,主要適用于必須使用高速異步串行通信,而對誤碼率要求又不是很高的應用環境,如基于Rs485協議的共線語音通信系統。對實現方法進行詳細的說明,并指出該方法

2017-11-10 14:21:43 4

4

4

4邏輯門是什么?基礎數字邏輯門詳解

邏輯門是邏輯電路的基本組成部分,可以由晶體管來構成,邏輯門大致可以分為基本門、萬用門和延伸門等三種,其中基本門又可以分為與門、或門和非門三種。邏輯門可以使信號的高低電平轉化為響應的邏輯信號,從而實現邏輯運算

2017-05-22 14:16:38 53353

53353

53353

53353

邏輯運算,什么是邏輯運算

邏輯運算,什么是邏輯運算 計算機中除了進行加、減、乘、除等基本算術運算外,還可對兩個或一個邏輯數進行邏輯運算。所謂邏輯數,是指不帶符號的二進制

2010-04-13 10:48:38 29945

29945

29945

29945邏輯加密卡,邏輯加密卡是什么意思

邏輯加密卡,邏輯加密卡是什么意思

邏輯加密存儲卡(Smart Card With Security Logic)主要是由EEPROM存儲單元陣列和密碼控制邏輯單元所構成。

2010-04-02 13:35:45 4633

4633

4633

4633華為同步電路設計規范

華為同步電路設計規范

為了增加可編程邏輯器件電路工作的穩定性,一定要加強可編程邏輯器件設計的規范要求,要盡量采用同步電路設計。對于設計中的異步

2010-02-11 10:04:19 125

125

125

125FPGA工程師面試試題集錦

FPGA工程師面試試題集錦1、同步電路和異步電路的區別是什么?(仕蘭微電子)2、什么是同步邏輯和異步邏輯?(漢王筆試)同步邏輯是時鐘之間有固定的因果關系。異步

2009-09-28 16:36:22 73

73

73

73異步時序邏輯電路

異步時序邏輯電路:本章主要從同步時序邏輯電路與異步時序邏輯電路狀態改變方式不同的特殊性出發, 系統的介紹異步時序邏輯電路的電路結構、工作原理、分析方法和設計方法。

2009-09-01 09:12:34 59

59

59

59邏輯代數與邏輯函數

邏輯代數與邏輯函數:本章主要討論分析和設計數字邏輯功能的數學。首先介紹邏輯代數中的基本運算、基本公式, 常用定理和重要規則; 然后講述邏輯函數的形式與轉換; 最后介

2009-09-01 09:11:40 47

47

47

47同步時序邏輯電路

同步時序邏輯電路:本章系統的講授同步時序邏輯電路的工作原理、分析方法和設計方法。從同步時序邏輯電路模型與描述方法開始,介紹同步時序邏輯電路的分析步驟和方法。然后

2009-09-01 09:06:27 71

71

71

71組合邏輯電路的分析與設計-邏輯代數

組合邏輯電路的分析與設計-邏輯代數

在任何時刻,輸出狀態只決定于同一時刻各輸入狀態的組合,而與先前狀態無關的邏輯電路稱為組合邏輯電路。

2009-04-07 10:07:57 2503

2503

2503

2503

邏輯函數與邏輯問題的描述

邏輯函數與邏輯問題的描述

在討論了與、或、非三種基本邏輯運算后,下面將從工程實際出發,提出邏輯命題,然后用真值表加以描述,從真值表可以寫出邏輯函數。一

2009-04-06 23:56:35 1192

1192

1192

1192

二值數字邏輯和邏輯電平

二值數字邏輯和邏輯電平

二進制數正好是利用二值數字邏輯中的0和1來表示的。二值數字邏輯是Binary Digital Logic的譯稱。 與模擬信

2009-04-06 23:37:10 3163

3163

3163

3163

第二十七講 同步時序邏輯電路的設計

第二十七講 同步時序邏輯電路的設計

7.5 同步時序邏輯電路的設計用SSI觸發器16進制以內7.5.1 同步時序邏輯電路的設計方法

2009-03-30 16:31:56 3156

3156

3156

3156

時序邏輯電路

實驗十六 時序邏輯電路? 實驗(1) 計數器?一、實驗目的?⒈ 熟悉計數器的設計方法及工作原理。?⒉ 了解同步計數器與異步計數器的區別。?⒊ 應用

2008-09-24 22:17:08 3155

3155

3155

3155

電子發燒友App

電子發燒友App

評論