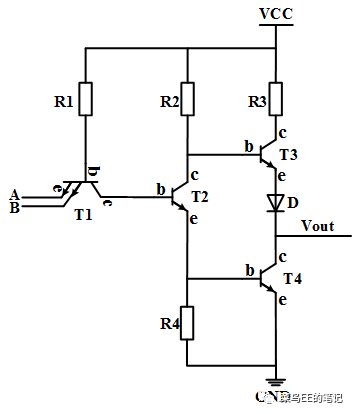

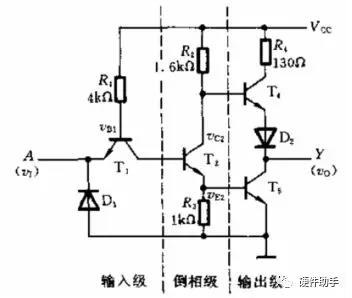

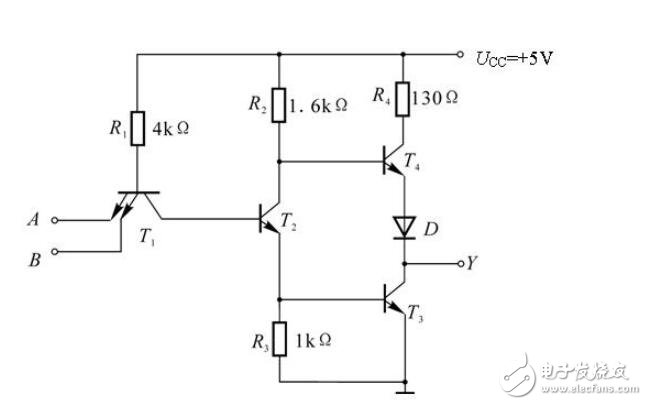

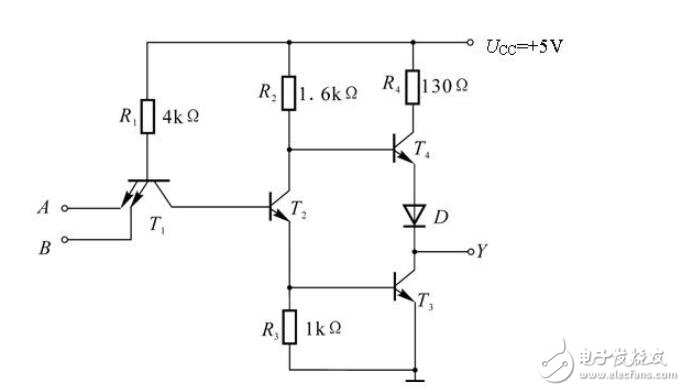

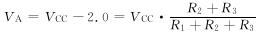

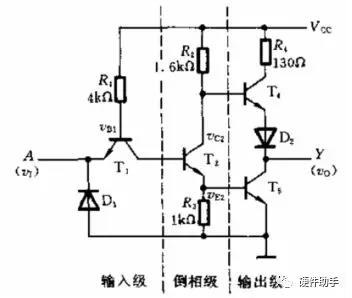

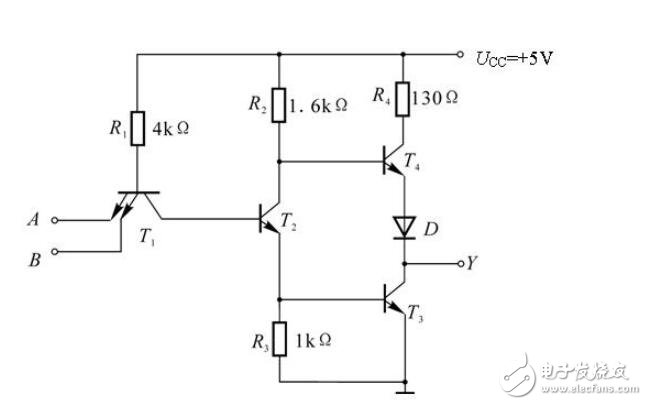

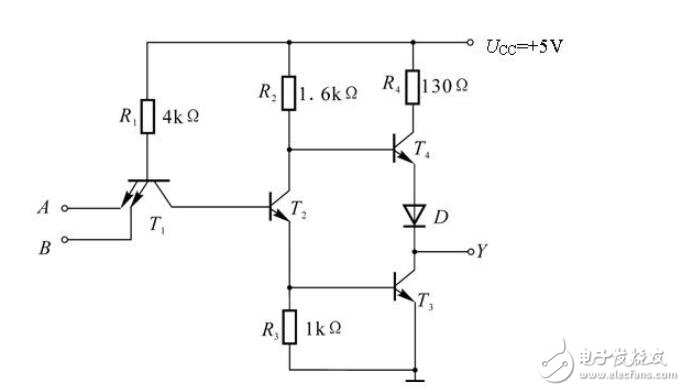

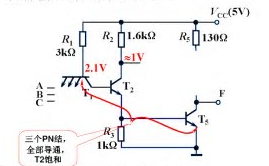

要實現輸出電平在0/1之間變換,需要三極管的數量最少只需要一個,而TTL電路使用了4個三極管,用較多的器件去實現相同的功能,必定要有性能上的提升,否則這種電路設計就是一種浪費。對于TTL電路而言,使用成倍的器件需要換來的性能包括以下幾點:

2023-09-21 17:03:47 199

199

ttl與非門懸空相當于輸入什么電平? 什么是 TTL 與非門? TTL 與非門(TTL NAND Gate)是一種基礎電子元件,屬于數字邏輯電路的一種。它是由兩個輸入端和一個輸出端組成的,當兩個輸入

2023-09-17 15:42:18 401

401 推挽輸出是低電平還是高電平? 推挽輸出器是一種常見的輸出方式。它由負和正三項組成,其中,負電平被連接到PNP晶體管,而正電平被連接到NPN晶體管。當給定輸入信號時,晶體管被開啟或關閉,電流流過負極

2023-08-31 10:26:31 589

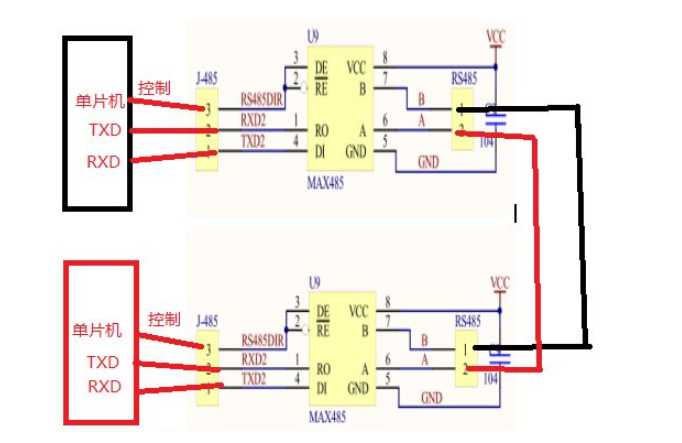

589 單端邏輯電平的匹配是我們平時在硬件設計中最經常碰到的,我們在《TTL&CMOS電平》章節中已經對TTL和COMS電平的匹配設計做了一些分析,一般3.3V LVTTL和LVCMOS是可以直接相互驅動的。但是其它不同邏輯電平之間呢?舉個栗子,3.3V邏輯電平和1.8V邏輯電平之間呢?

2023-06-25 14:52:24 929

929

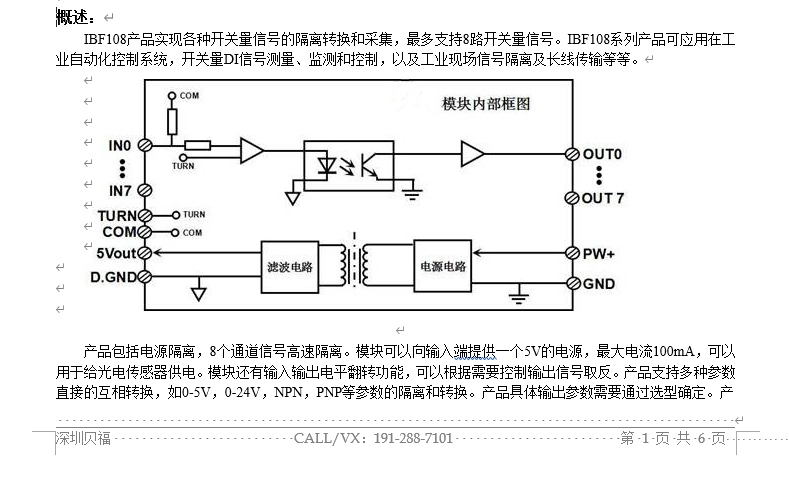

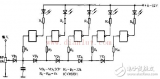

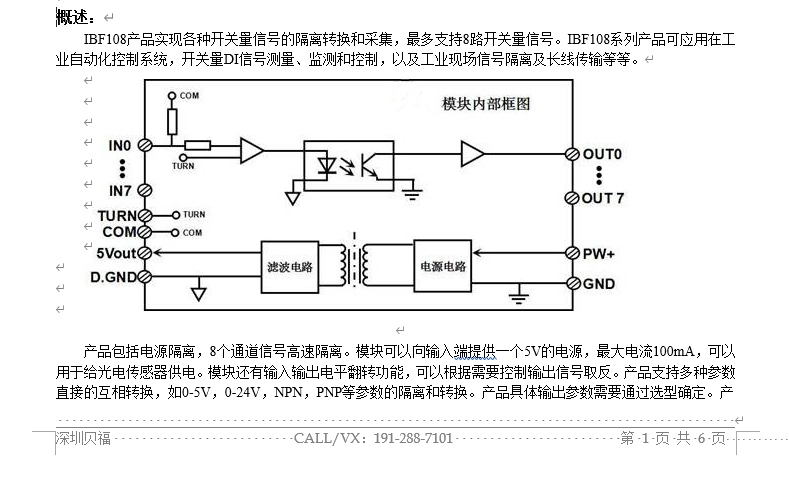

品特點: ● ?8路NPN信號轉PNP信號高速轉換 ● ?8路0-5V電平轉0-24V電平 ●? 8路TTL電平轉0-24V電平 ● ?8路NPN信號轉TTL電平 ● ?8路0-24V電平轉0-5V

2023-05-09 17:55:31 172

172

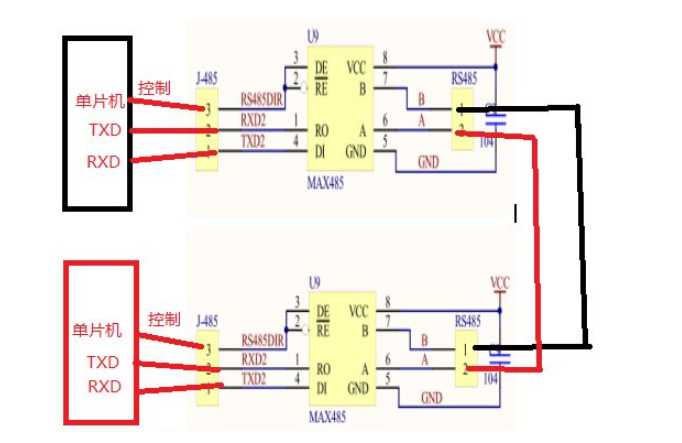

,RS-422/485是差分輸入輸出,RS-232是單端輸入輸出。2.3:TTL和CMOS的邏輯電平關系圖2-1:TTL和CMOS的邏輯電平圖上圖為5V TTL邏輯電平、5V CMOS邏輯電平、LVTTL邏輯電平

2008-06-24 09:38:52

電平,就是指電路中兩點或幾點在相同阻抗下電量的相對比值。這里的電量自然指“電功率”、“電壓”、“電流”,并將倍數化為對數,用“分貝”表示,記作“dB”。常用邏輯電平有TTL、CMOS、RS232、RS485等。

2023-04-12 14:58:39 4201

4201

什么是TTL電平、CMOS電平、RS232電平?它們有什么區別呢?一般說來,CMOS電平比TTL電平有著更高的噪聲容限。

2023-02-07 14:58:26 2846

2846 為了精簡電路 電器中會用到邏輯電平代替復雜的接線 他們都是如何設計的呢? CMOS器件與TTL器件? ? CMOS電平與TTL電平 ? 如何利用MOS管實現雙向電平轉換 ? 什么是LVDS電平

2022-12-14 11:36:07 305

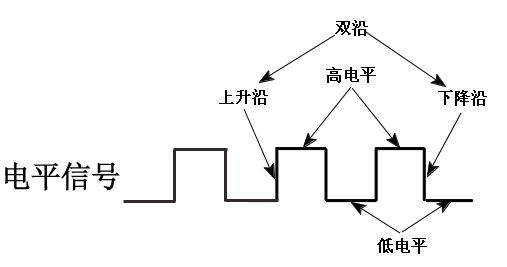

305 TTL 是 Time To Live 的縮寫, 是生存時間值的意思, TTL 電平信號規定, +5V 等價于邏輯“1”, 0V 等價于邏輯“0”(采用二進制來表示數據時)。 輸入高電平>

2022-11-22 10:14:09 774

774

電路設計中,經常遇到各種不相同的邏輯電平。常見的邏輯電平如下: TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,還有一些速度比較高的 LVDS

2022-10-27 10:39:48 6297

6297 TTL器件輸出低電平要小于0.8V,高電平要大于2.4V。輸入,低于1.2V就認為是0,高于2.0就認為是1。于是TTL電平的輸入低電平的噪聲容限就只有(0.8-0)/2=0.4V,高電平的噪聲容限為(5-2.4)/2=1.3V。

2022-08-22 10:10:50 7957

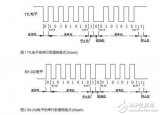

7957 由于TTL是流控器件,電流起作用,電路的響應速度較快,狀態建立時間在在5-10ns,而CMOS電路是壓控器件,狀態建立時間25-50ns。

2022-08-16 09:33:46 957

957 什么是ttl電平

TTL電平信號被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯"1",0V等價于邏輯"0",這被稱做TTL(晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制

2022-02-11 15:12:28 14

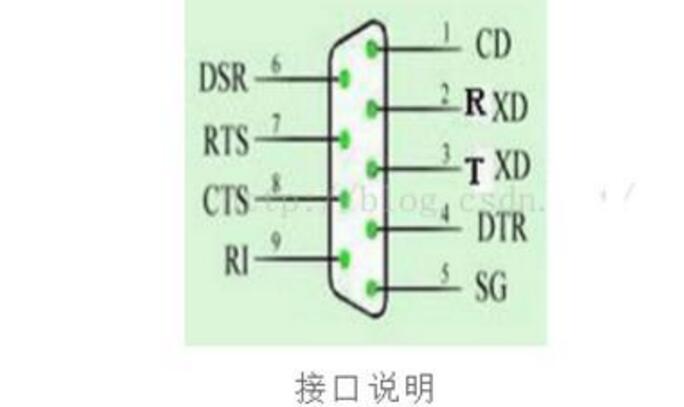

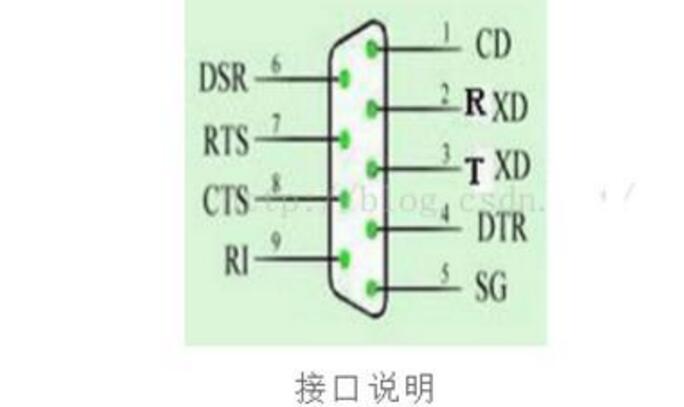

14 IT6302 電源后面板的 DB9 接口輸出為 TTL 電平,您需要通過附件電平轉換后才可連接到 PC機的串口上。該DB9接口的接口定義為:1-VCC(5V 由IT6302輸出)2-RX(TTL電平

2022-01-06 12:47:38 7

7 1.開漏輸出和推挽輸出的區別開漏輸出只能輸出低電平,需要上拉電阻才能輸出高電平;推挽輸出既能輸出低電平又能輸出高電平。(點擊查看:上拉電阻和下拉電阻的詳細解釋)2.懸空輸入、模擬輸入、上拉輸入、下拉

2021-12-01 10:06:07 47

47 電子電路是單片機硬件部分的基礎知識,電子電路分為模擬電路和數字電路。單片機是使用數字電路,但ADC功能涉及模擬電路。1、模擬電路與數字電路2、歐姆定律3、電源正極和負極4、TTL電平和CMOS電平

2021-12-01 10:06:07 11

11 什么是TTL電平,什么是CMOS電平,他們的區別

2021-11-30 20:51:06 37

37 的平臺,給老司機交流的平臺。所有文章來源于項目實戰,屬于原創。一、電平規范1、名稱解釋Uoh -> 輸出高電平,Uol -> 輸出低電平;Uih -> 輸入高電平,Uil -&g...

2021-11-30 20:21:12 6

6 TTL,CMOS都屬于數字電路。TTL電流控制器件輸出高電平>2.4V輸出低電平<0.4VCMOS電壓控制器件輸出高電平>2.4V輸出低電平<0.4V

2021-11-26 18:51:08 10

10 電子發燒友網為你提供什么是TTL電平、CMOS電平?都有哪些區別?資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:41:19 21

21 電子發燒友網為你提供常用電平標準(TTL、CMOS......)總結資料下載的電子資料下載,更有其他相關的電路圖、源代碼、課件教程、中文資料、英文資料、參考設計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-08 08:47:24 11

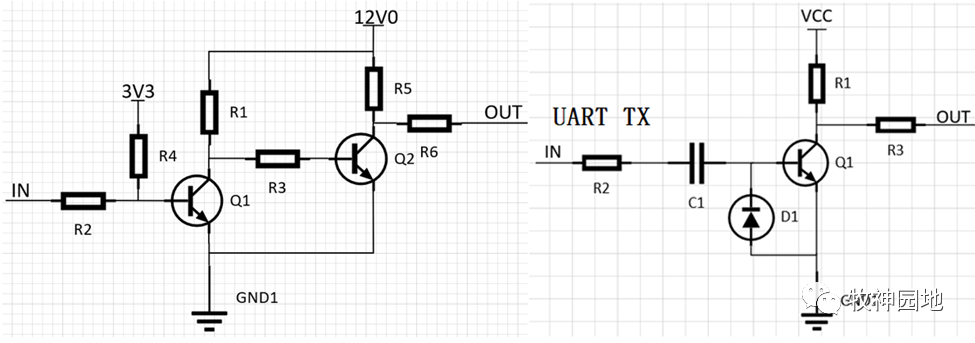

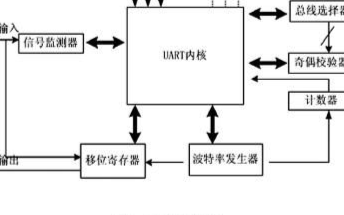

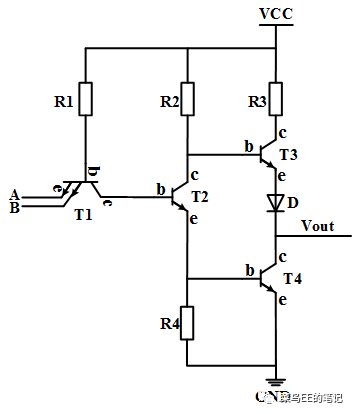

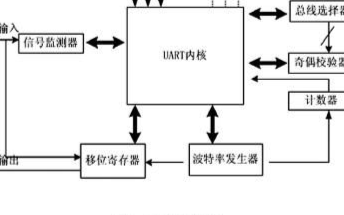

11 實現RS-232電平和TTL/CMOS電平轉換可以用接口芯片來實現,實現數據的串行到并行轉換用的是UART,它們是實現串行通信必不可少的兩個部分。

2021-03-26 14:19:59 3363

3363

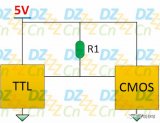

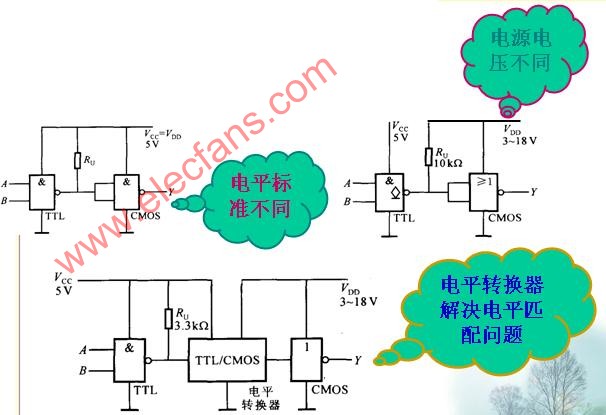

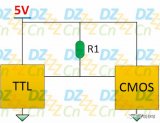

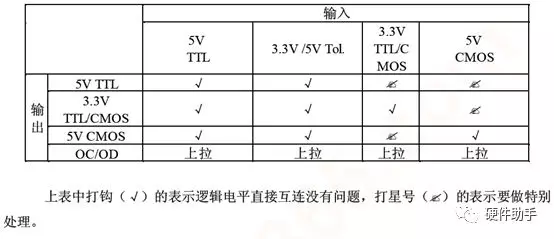

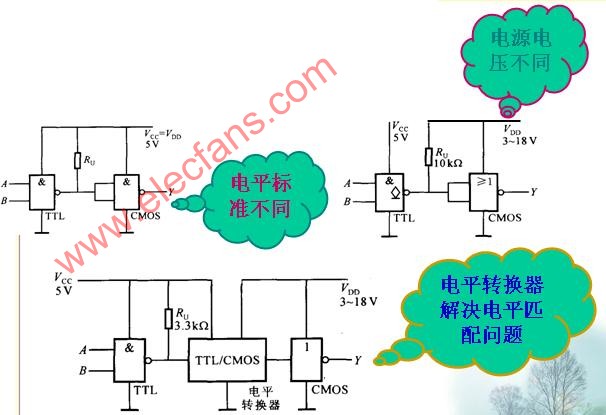

可以看到,TTL邏輯輸出的低電平最大值VOLMAX(0.4V)小于CMOS邏輯輸入低電平最大值VILMAX(0.3×VCC=1.5V),因此,TTL低電平驅動CMOS邏輯是完全沒有問題的,但是TTL

2021-01-20 17:14:12 4716

4716

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關器件規范、電平規范。

2021-01-06 17:40:22 20

20 本篇主要介紹常用的單端邏輯電平,包括TTL、CMOS、SSTL、HSTL、POD12等。 1、TTL電平 ? ? ? 下面以一個三輸入的TTL與非門介紹TTL電平的原理。 ? ? ? 三輸入TTL

2020-12-24 13:05:29 30414

30414

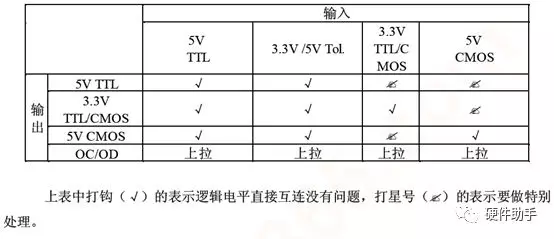

本篇主要介紹TTL/CMOS電平的互連、OC/OD的互連,其余單端邏輯電平的互連可參考相關器件規范、電平規范。 1、TTL/CMOS互連 常用的TTL和CMOS電平主要是5V TTL、5V CMOS

2020-12-23 14:15:12 5125

5125

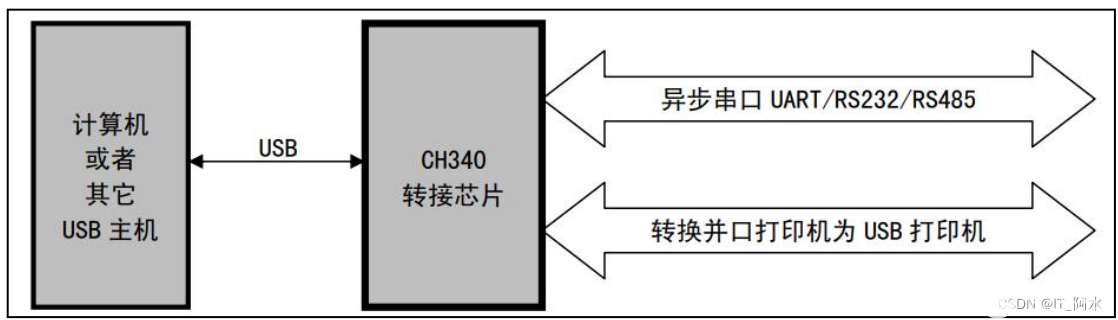

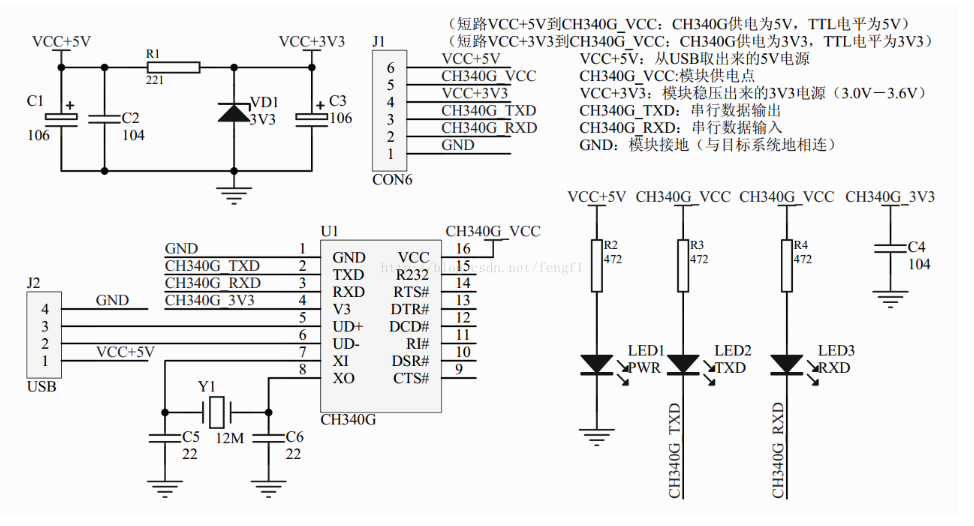

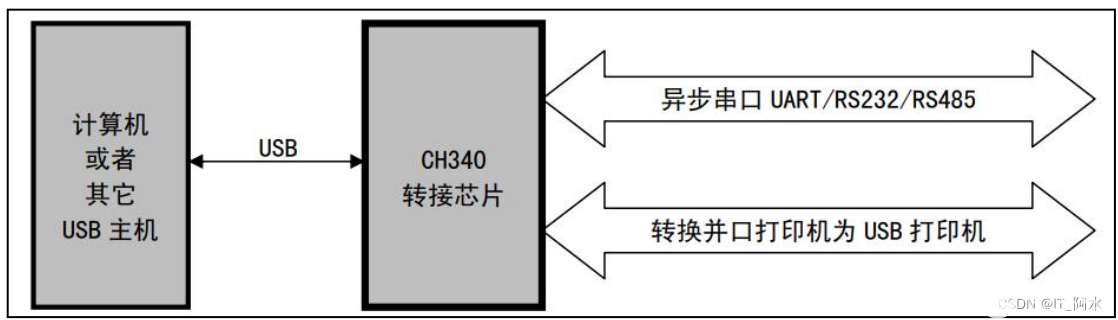

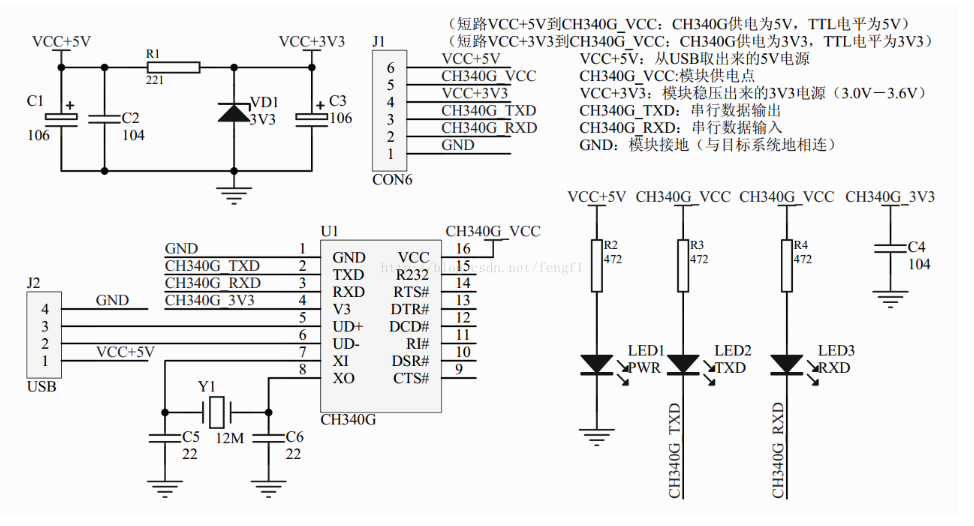

CH340是南京沁恒公司生產的USB轉串口芯片,能夠將TTL電平轉換為USB的輸出。

2020-10-20 13:44:00 13221

13221

在門電路輸入端串聯10K電阻后再輸入低電平,輸入端出呈現的是高電平而不是低電平。因為由TTL門電路的輸入端負載特性可知,只有在輸入端接的串聯電阻小于910歐時,它輸入來的低電平信號才能被門電路識別出來,串聯電阻再大的話輸入端就一直呈現高電平。這個一定要注意。COMS門電路就不用考慮這些了。

2020-08-05 10:41:30 16526

16526

本文檔的主要內容詳細介紹的是TTL和CMOS電平的區別詳細資料說明。

2020-06-05 17:10:31 25

25 請記住,以“I”開頭的引腳“是要進行電平轉換的輸入信號。以字母“ O”開頭的引腳是經過電平轉換并準備好讀取和/或使用的輸出信號。

2019-11-08 10:51:38 11775

11775

1.CMOS電平:

‘1’邏輯電平電壓接近于電源電壓,‘0’邏輯電平接近于0V。噪聲容限很大

2.TTL電平:

輸出高電平》2.4V,輸出低電平《0.4V。在室溫下,一般輸出高電平是3.5V

2019-09-14 10:52:00 5164

5164

CMOS電平:CMOS電路輸出高電平為3V~12V,低電平輸出接近0V 計算機的MAX232電平:高電平為-5V到-12V,低電平為+5V到+12V,為負電壓電平

2019-09-09 17:26:00 2

2 晶體管組成了TTL集成電路,TTL大多采用5V電路。用二進制來進行表示的話, 5V正好等于邏輯上的“1”, 0V等于邏輯上的“0”,因此, TTL電平在電路中得以被大星應用。而在此領域中,同樣被大量應用的還有CMOS電平。除了邏輯電平范圍的不同,TTL電平和CMOS電平之間還有哪些不同呢?

2019-08-19 14:20:23 27886

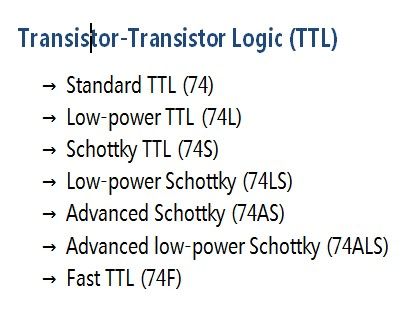

27886 本文檔的主要內容詳細介紹的是TTL電平與COMS電平的常識性概念詳細資料說明。TTL 集成電路的主要型式為晶體管-晶體管邏輯門( transistor-transistor logic gate ), TTL 大部分都采用5V 電源。

2019-07-11 16:45:58 9

9 TTL和COMS電平比較:

( 一)TTL 高電平3.6~5V,低電平0V~2.4V

CMOS電平Vcc 可達到12VTTL電路不使用的輸入端懸空為高電平另外, CMOS集成電路電源電壓可以在

2019-06-18 17:41:59 16

16 TTL電平信號被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯“1”,0V等價于邏輯“0”,這被稱做TTL(晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2019-06-06 17:50:00 5

5 TTL電平信號規定,+5V等價于邏輯“1”,0V等價于邏輯“0”(采用二進制來表示數據時)。這樣的數據通信及電平規定方式,被稱做TTL(晶體管-晶體管邏輯電平)信號系統。這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2019-01-22 16:36:59 62958

62958

TTL電平信號的傳輸距離在資料上一般寫15米,降低波特率可以更遠些,但是普通 TTL 芯片不適合米級距離的信號傳輸,需要用接口器件傳輸信號。同時,信號質量與傳輸速率有關。

2019-01-22 16:34:04 19095

19095

(AHCT與TTL電平兼容)

FCT——FACT擴展系列,與TTL電平兼容

FACT——Fairchild Advanced CMOS Technology,其

?

1,TTL電平:

???輸出高電平>2.4V,輸出低電平=2.0V,輸入低電平

2018-09-20 18:26:45 7830

7830 TTL、CMOS電平和OC門知識大全

2018-07-15 10:33:00 7222

7222 單片機的串口輸出電路采用的邏輯電平是TTL電平。這種電平信號由TTL器件產生的。在這里我們可以使用集成芯片MAX232,這是一款專門用來進行信號電平的轉換的芯片,使用起來簡單方便,這里把電路貼出。

2018-04-18 15:19:57 35086

35086

TTL 電平信號被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯“1”,0V等價于邏輯“0”,這被稱做TTL(Transistor- Transistor Logic 晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2018-03-23 16:45:00 37403

37403 1、CMOS是場效應管構成(單極性電路),TTL為雙極晶體管構成(雙極性電路)

2、COMS的邏輯電平范圍比較大(5~15V),TTL只能在5V下工作

3、CMOS

2017-12-19 12:38:14 105411

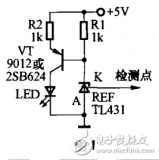

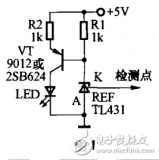

105411 本文用TL431制作TTL邏輯電平檢測電路,檢測電路工作原理:V+=5V,當檢測電壓低于2.5V(TTL低電平),Vka=5V,vT截止,LED不亮;當檢測電壓高于2.5V(TTL高電平),Vka=2V,vT導通,LED亮。

2017-12-13 10:05:30 6859

6859

實際輸出的效果是相反的,但是具體的原因是什么呢? 232跟TTL的電平標準是相反的 mcuisp軟件是用232的電平標準編寫的,當我們開發板里面使用的串口ISP軟件不是232而是CH340/PL2303等TTL電平時,那么設置就要相反才行。

2017-12-05 15:08:33 3

3 TTL電平信號之所以被廣泛使用,原因是因為:通常我們采用二進制來表示數據。而且規定,+5V等價于邏輯“1”,0V等價于邏輯“0”。這樣的數據通信及電平規定方式,被稱做TTL(晶體管-晶體管邏輯電平)信號系統。這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2017-11-15 15:26:10 49228

49228

TTL電平最常用于有關電專業,如:電路、數字電路、微機原理與接口技術、單片機等課程中都有所涉及。在數字電路中只有兩種電平(高和低)高電平+5V、低電平0V.同樣運用比較廣泛的還有CMOS電平、232

2017-11-15 14:34:49 6

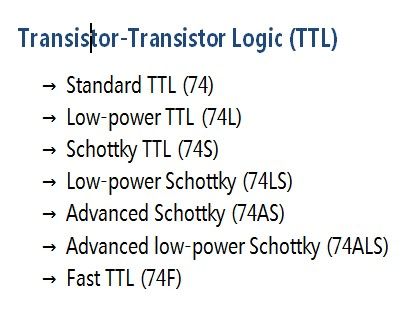

6 一.TTL TTL集成電路的主要型式為晶體管-晶體管邏輯門(transistor-transistor logic gate),TTL大部分都采用5V電源。 1.輸出高電平Uoh和輸出低電平

2017-11-08 12:59:13 0

0 介紹常用的幾種邏輯電平,然后給出其與光模塊的接口電路。 TTL 電路的電平就叫 TTL 電平,CMOS 電路的電平就叫 CMOS 電平。 TTL 集成電路的全名是晶體管-晶體管邏輯集成電路(Transistor-Transistor Logic),標準 TTL 輸入高電平最小 2V,輸出高電平

2017-11-06 16:50:08 100

100 一.TTL TTL 集成電路的主要型式為晶體管-晶體管邏輯門(transistor-transistor logic gate),TTL 大部分都采用 5V 電源。 1.輸出高電平 Uoh 和輸出

2017-11-04 10:32:33 20

20 TTL電平信號之所以被廣泛使用,原因是因為:通常我們采用二進制來表示數據。而且規定,+5V等價于邏輯“1”,0V等價于邏輯“0”。這樣的數據通信及電平規定方式,被稱做TTL(晶體管-晶體管邏輯電平)信號系統。這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2017-11-01 09:52:22 94775

94775

TTL CMOS RS232 RS485 RS422各種電平內容

2017-10-31 14:32:33 53

53 在 同樣5V電源電壓情況下,COMS電路可以直接驅動TTL,因為CMOS的輸出高電平大于2.0V,輸出低電平小于0.8V。

2017-09-20 10:04:53 30917

30917

數字信號才是0和1 。凡是輸入與 5V TTL 電平兼容的 5V CMOS 器件都可以用作 3.3V→5V 電平轉換,這是由于 3.3V CMOS 的電平剛好和5V TTL電平兼容(巧合),而 CMOS 的輸出電平總是接近電源電平的。

2017-08-26 16:52:00 8159

8159

ECL電平、LVDS電平、TTL電平三者的簡單比較,在應用方面酌情選取

2016-08-29 16:05:01 69

69 在電路設計時,最容易忽視也最容易造成錯誤的問題,詳細介紹TTL電平和CMO電平之間怎么轉換

2016-01-13 10:23:26 7

7 CMOS 電路是電壓控制器件,輸入電阻極大,對于干擾信號十分敏感,因此不用的輸入端不應開路,接到地或者電源上。 CMOS 電路的優點是噪聲容限較寬,靜態功耗很小。TTL 電平輸出高電

2011-08-08 16:02:01 179

179 本文分析了以電阻為負載的傳統三也TTL反相器的缺點,借鑒二值TTL推挽輸出極結構,設計了三值TTL電路的推挽輸出級.用SPICE I對設計電路的計算機模擬明,具有推挽輸出結椅的三值T

2010-04-30 10:16:42 25

25 TTL和CMOS電平基礎知識

TTL電平: 輸出高電平 > 2.4V 輸出低電平 <

2009-11-28 11:28:33 1211

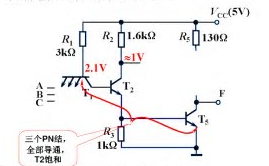

1211 TTL電路驅動CMOS電路

工作電源電壓不同;高、低電平標準不同。

2009-09-24 11:07:14 6193

6193

邏輯電平詳細介紹邏輯電平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。 常用邏輯系列器件 TTL:Transistor-Transistor Logic CMOS:Compl

2009-04-12 12:03:16 10541

10541

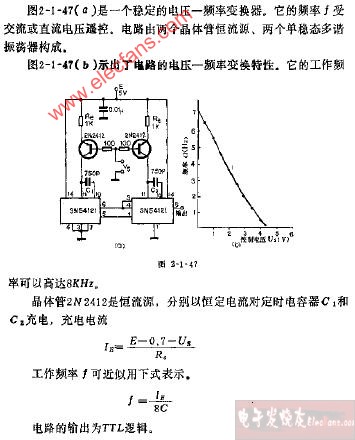

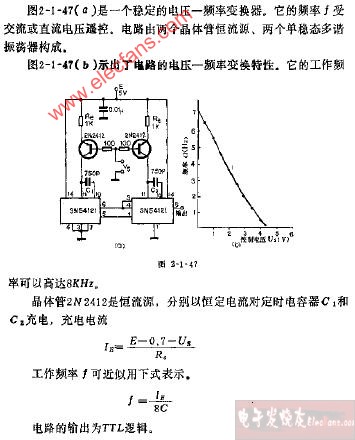

具有TTL邏輯電平輸出的壓控振蕩器

2009-03-23 10:00:59 562

562

電平標準:現在常用的電平標準有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,還有一些速

2008-07-21 10:25:08 2624

2624 TTL電平信號被利用的最多是因為通常數據表示采用二進制規定,+5V等價于邏輯“1”,0V等價于邏輯“0”,這被稱做TTL(晶體管-晶體管邏輯電平)信號系統,這是計算機處理器控制的設備內部各部分之間通信的標準技術。

2007-12-05 09:41:49 9677

9677 TTL電平與CMOS電平的區別

1,TTL電平:

輸出高電平>2.4V,輸出低電平<0.4V。在室溫下,一般輸出高電平是3.5V,輸出低電

2007-10-10 12:26:19 7799

7799 幾種常用邏輯電平電路的特點及應用

幾種常用邏輯電平電路的特點及應用

標簽/分類:

在通用的電子器件設備中,TTL和CMOS電路的應用非常廣泛。但

2007-08-21 15:34:59 1096

1096

電子發燒友App

電子發燒友App

評論