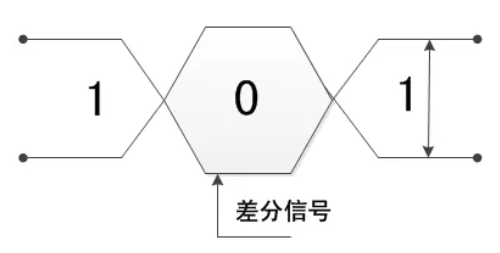

LVDS差分信號抗噪特性

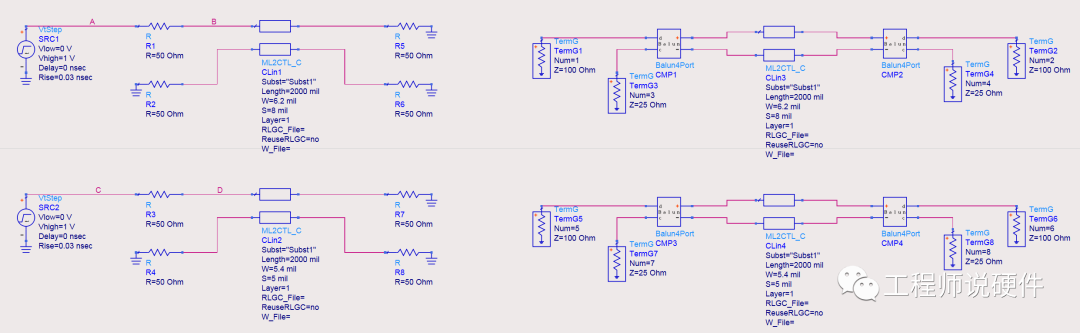

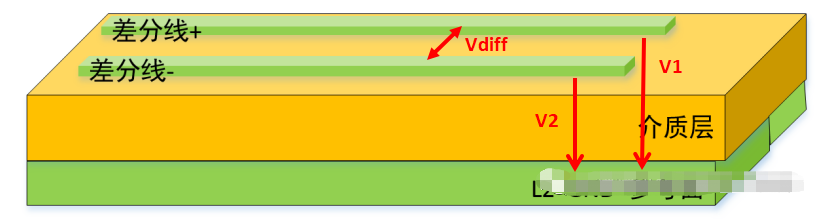

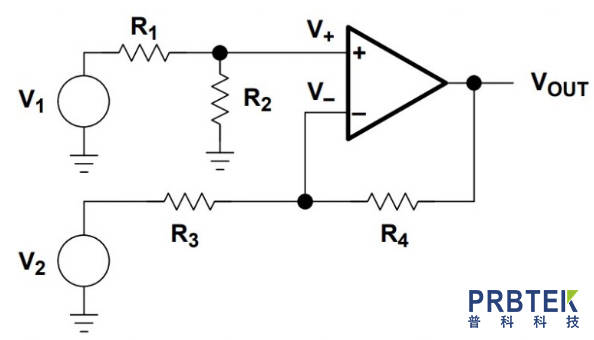

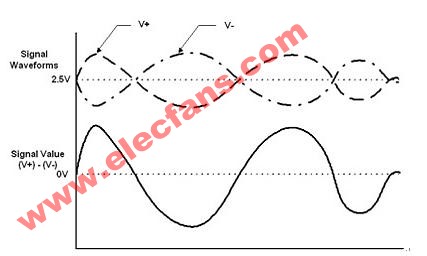

從差分信號傳輸線路上可以看出,若是理想狀況,線路沒有干擾時,

在發送側,可以形象理解為:IN= IN+ - IN-

在接收側,可以理解為:IN+ - IN-= OUT

所以:OUT=IN

在實際線路傳輸中,線路存在干擾,并且同時出現在差分線對上,

在發送側,仍然是:IN=IN+ - IN-

線路傳輸干擾同時存在于差分對上,假設干擾為q,則接收則:(IN++ q) - (IN- + q) = IN+ - IN- =OUT

所以:OUT=IN

噪聲被抑止掉。

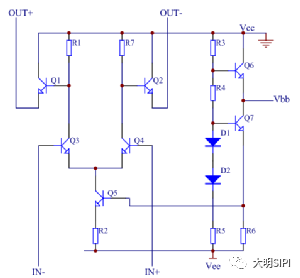

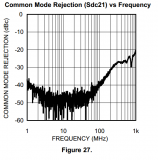

上述可以形象理解差分方式抑止噪聲的能力。在實際芯片中,是在噪聲容限內,采用“比較”及“量化”來處理的。

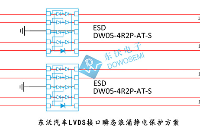

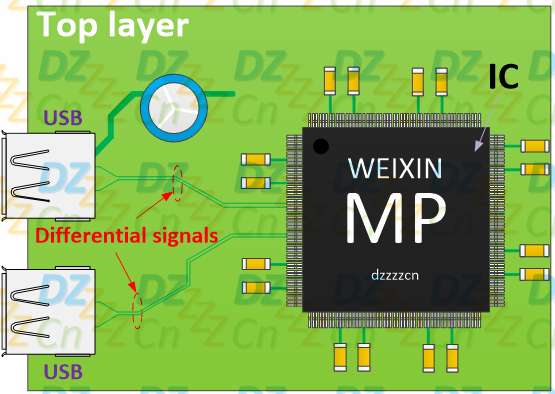

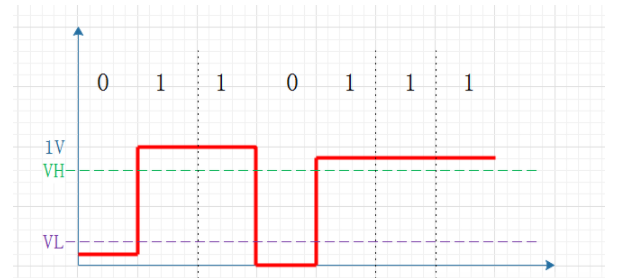

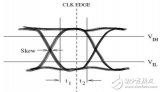

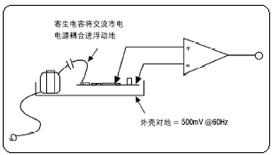

LVDS接收器可以承受至少±1V的驅動器與接收器之間的地的電壓變化。由于LVDS驅動器典型的偏置電壓為+1.2V,地的電壓變化、驅動器偏置電壓以及輕度耦合到的噪聲之和,在接收器的輸入端相對于接收器的地是共模電壓。這個共模范圍是:+0.2V~+2.2V。建議接收器的輸入電壓范圍為:0V~+2.4V。

抑止共模噪聲是DS(差分信號)的共同特性,如RS485,RS422電平,采用差分平衡傳輸,由于其電平幅度大,更不容易受干擾,適合工業現場不太惡劣環境下通訊。

電子發燒友App

電子發燒友App

評論