串行進位加法器

- 加法器(29467)

相關推薦

初級數字IC設計-加法器

加法器(Adder)** 是非常重要的,它不僅是其它復雜算術運算的基礎,也是** CPU **中** ALU **的核心部件(全加器)。

2023-10-09 11:14:14 431

431

431

431

半加法器的工作原理及電路解析

半加法器是一種執行二進制數相加的數字電路。它是最簡單的數字加法器,您只需使用兩個邏輯門即可構建一個;一個異或門和一個 AND 門。

2023-06-29 14:35:25 1320

1320

1320

1320

全加法器的工作原理和電路解析

加法器可以是半加法器或全加法器。不同之處在于半加法器僅用于將兩個 1 位二進制數相加,因此其總和只能從 0 到 2。為了提高這種性能,開發了FullAdder。它能夠添加三個 1 位二進制數,實現從 0 到 3 的總和范圍,可以用兩個輸出位 (“11”) 表示。

2023-06-29 14:27:35 1542

1542

1542

1542

加法器的原理及采用加法器的原因

有關加法器的知識,加法器是用來做什么的,故名思義,加法器是為了實現加法的,它是一種產生數的和的裝置,那么加法器的工作原理是什么,為什么要采用加法器,下面具體來看下。

2023-06-09 18:04:17 2245

2245

2245

2245怎樣測量加法器的速度?器件延遲的時間長度!

設計了一種加法器,晶體管數少,計算速度快。希望能更精確的測量到,快多少?實物已經制作,但不會使用示波器。是不是應該通過VHDL時序,進行驗證加法器的速度?

2022-10-30 17:53:29 980

980

980

980

計算機組成原理、數字邏輯之加法器詳解

問題咨詢及項目源碼下載請加群:群名:IT項目交流群群號:245022761一、加法器的意義加法器是計算機中的基礎硬件,了解加法器不僅能夠揭開計算機的本質,也能對計算機的數制運算產生深刻的理解。二、半

2021-11-11 12:06:03 20

20

20

20加法器工作原理_加法器邏輯電路圖

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用

2021-02-18 14:40:31 29303

29303

29303

29303

FPGA的一些學習資料詳細說明

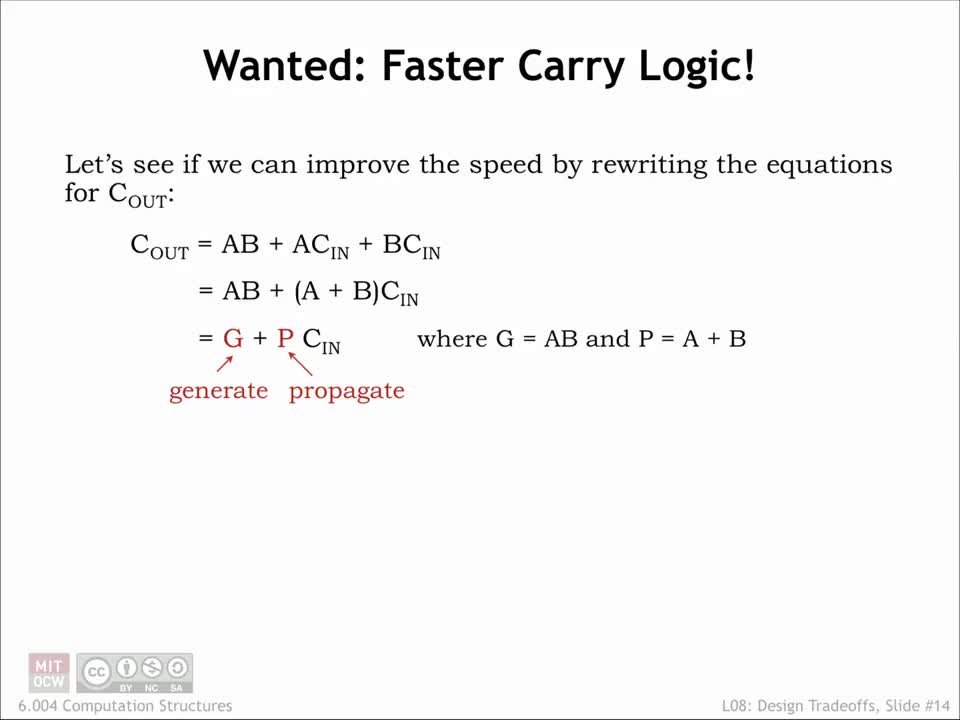

昨天后仿真四位加法器的時候,想比較一下,超前進位加法器和串行加法器的時候,特意比較了一下那個的延時少一些,居然發現超前進位加法器延時比串行加法器多,不知道為什么,于是做么一下是不是優化的問題。

2020-10-14 16:00:00 13

13

13

13DM74LS83A四位快速進位二進制加法器的數據手冊免費下載

這些全加器執行兩個4位二進制數的加法。為每一位提供和(∑)輸出,并從第四位獲得所得進位(C4)。這些加法器的特點是在所有四個位上都具有完全的內部前瞻性。這為系統設計者提供了部分經濟性前瞻性能,并減少

2020-05-26 08:00:00 1

1

1

1加法器原理

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用

2019-06-19 14:20:39 23685

23685

23685

23685

加法器功能

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。

2019-06-19 14:19:17 6914

6914

6914

691412位加法器的實驗原理和設計及腳本及結果資料說明

加法器是數字系統中的基本邏輯器件。例如:為了節省資源,減法器和硬件乘法器都可由加法器來構成。但寬位加法器的設計是很耗費資源的,因此在實際的設計和相關系統的開發中需要注意資源的利用率和進位速度等兩方面的問題。

2019-04-15 08:00:00 4

4

4

4怎么設計一個32位超前進位加法器?

最近在做基于MIPS指令集的單周期CPU設計,其中的ALU模塊需要用到加法器,但我們知道普通的加法器是串行執行的,也就是高位的運算要依賴低位的進位,所以當輸入數據的位數較多時,會造成很大的延遲

2018-07-09 10:42:00 18610

18610

18610

18610

加法器內部電路原理

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

2018-01-29 11:28:26 79946

79946

79946

79946

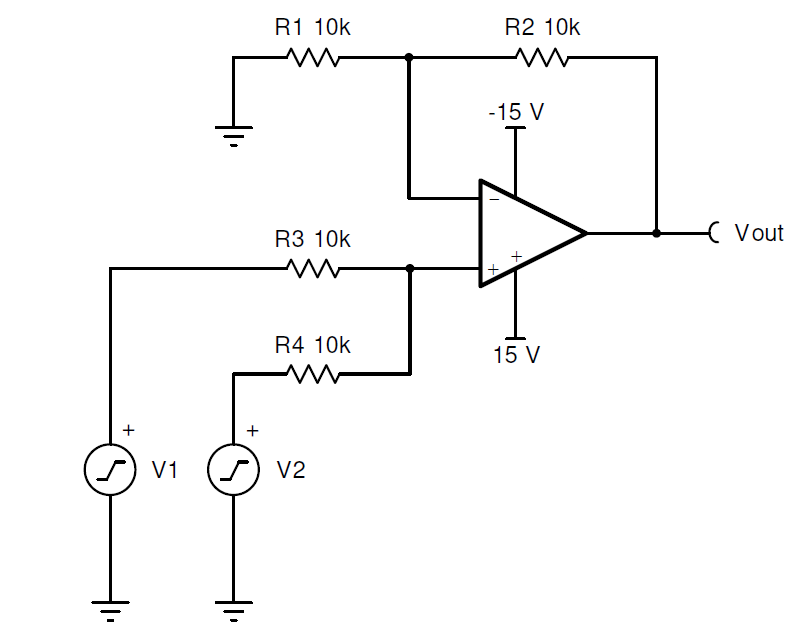

反相加法器電路與原理

加法器是為了實現加法的。即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

2018-01-29 10:49:50 30686

30686

30686

30686

加法器電路設計方案匯總(八款模擬電路設計原理詳解)

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。在電子學中,加法器是一種數位電路,其可進行數字的加法計算。

2018-01-17 10:42:03 134108

134108

134108

134108

八位加法器仿真波形圖設計解析

8位全加器可由2個4位的全加器串聯組成,因此,先由一個半加器構成一個全加器,再由4個1位全加器構成一個4位全加器并封裝成元器件。加法器間的進位可以串行方式實現,即將低位加法器的進位輸出cout與相臨的高位加法器的最低進位輸入信號cin相接最高位的輸出即為兩數之和。

2017-11-24 10:01:45 27671

27671

27671

27671

音頻運放加法器電路_njm4558 音頻運放電路

在電子學中,加法器是一種數位電路,其可進行數字的加法計算。加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

2017-08-16 12:06:45 16643

16643

16643

16643

加法器與減法器_反相加法器與同相加法器

加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。減法電路是基本集成運放電路的一種,減法電路可以由反相加法電路構成,也可以由差分電路構成。基本集成運放電路有加、減、積分和微分等四種運算。一般是由集成運放外加反饋網絡所構成的運算電路來實現。

2017-08-16 11:09:48 157219

157219

157219

157219

同相加法器電路圖_反相加法器電路圖_運放加法器電路圖解析

在電子學中,加法器是一種數位電路,其可進行數字的加法計算。加法器是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。常用作計算機算術邏輯部件,執行邏輯操作、移位與指令調用。

2017-08-16 10:21:31 143816

143816

143816

143816

加法器是什么?加法器的原理,類型,設計詳解

加法器是為了實現加法的。即是產生數的和的裝置。加數和被加數為輸入,和數與進位為輸出的裝置為半加器。若加數、被加數與低位的進位數為輸入,而和數與進位為輸出則為全加器。

2017-06-06 08:45:01 22064

22064

22064

22064

MC14008B:4比特加法器

構造完整的MC14008B 4比特加法器與MOS p溝道和n溝道增強型設備在一個單一的整體結構。 這個設備由四個完整的蛇與快速內部先行的輸出。 它是有用的在二進制加法和其他算法的應用程序。 快速并行進位輸出位允許高速與其他毒蛇在系統操作使用時。

2017-04-06 08:56:16 11

11

11

11同相加法器電路原理與同相加法器計算

同相加法器輸入阻抗高,輸出阻抗低 反相加法器輸入阻抗低,輸出阻抗高.加法器是一種數位電路,其可進行數字的加法計算。當選用同相加法器時,如A輸入信號時,因為是同相加法器,輸入阻抗高,這樣信號不太容易流入加法器,反而更容易流入B端。

2016-09-13 17:23:33 54133

54133

54133

54133

基于選擇進位32位加法器的硬件電路實現

為了縮短加法電路運行時間,提高FPGA運行效率,利用選擇進位算法和差額分組算法用硬件電路實現32位加法器,差額分組中的加法單元是利用一種改進的超前進位算法實現,選擇進位算

2013-09-18 14:32:05 33

33

33

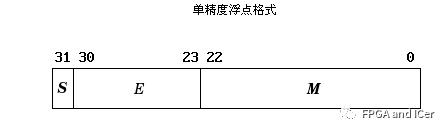

33FPU加法器的設計與實現

浮點運算器的核心運算部件是浮點加法器,它是實現浮點指令各種運算的基礎,其設計優化對于提高浮點運算的速度和精度相當關鍵。文章從浮點加法器算法和電路實現的角度給出設計

2012-07-06 15:05:42 47

47

47

47一款32位嵌入式CPU的定點加法器設計

根據一款32位嵌入式CPU的400MHz主頻的要求,結合該CPU五級流水線結構,并借鑒各種算法成熟的加法器,提出了一種電路設計簡單、速度快、功耗低、版圖面積小的32位改進定點加法器

2010-07-19 16:10:03 17

17

17

17加法器和乘法器簡介及設計

大多數數字功能可分為:數據通道、儲存器、控制單元、I/O。加法器和乘法器屬于數據通道部分。 一般對數據通道有如下要求:首先是規整性以優化版圖,其次是局域性(時間

2010-05-25 17:43:34 6279

6279

6279

6279多位快速加法器的設計

摘要:加法運算在計算機中是最基本的,也是最重要的運算。傳統的快速加法器是使用超前進位加法器,但其存在著電路不規整,需要長線驅動等缺點。文章提出了采用二叉樹法設

2010-05-19 09:57:06 62

62

62

62計算機常用的組合邏輯電路:加法器

計算機常用的組合邏輯電路:加法器

一、加法器

1.半加器: 不考慮進位輸入時,兩個數碼X n和Y n相加稱為半加。設半加和為H n ,則H n 的

2010-04-15 13:48:11 5885

5885

5885

5885十進制加法器,十進制加法器工作原理是什么?

十進制加法器,十進制加法器工作原理是什么?

十進制加法器可由BCD碼(二-十進制碼)來設計,它可以在二進制加法器的基礎上加上適當的“校正”邏輯來實現,該校正邏

2010-04-13 10:58:41 12142

12142

12142

12142加法器原理(16位先行進位)

加法器原理(16位先行進位)

這個加法器寫的是一波三折啊,昨天晚上花了兩三個小時好不容易寫完編譯通過了,之后modelsim莫

2010-03-08 16:52:27 10796

10796

10796

10796加法器:Summing Amplifier

加法器:Summing Amplifier

The summing amplifier, a special case of the inverting amplifier, is shown in Figure 4. The circuit gives an

2009-05-16 12:38:34 2486

2486

2486

2486

性能改進的1 6 位超前進位加法器

加法運算是最重要最基本的運算, 所有的其他基本算術運算, 減、 乘、 除、 模乘運算最終都能歸結為加法運算。 在不同的場合使用的加法器對其要求也不同, 有的要求

2009-04-08 15:15:12 41

41

41

41超前進位集成4(四)位加法器74LS283

超前進位集成4位加法器74LS283

由于串行進位加法器的速度受到進位信號的限制,人們又設計了一種多位數超前進位

2009-04-07 10:36:35 26072

26072

26072

26072

第二十講 加法器和數值比較器

第二十講 加法器和數值比較器

6.6.1 加法器一、半加器1.含義 輸入信號:加數Ai,被加數Bi 輸出信號:本位和Si,向高位

2009-03-30 16:24:54 4993

4993

4993

4993

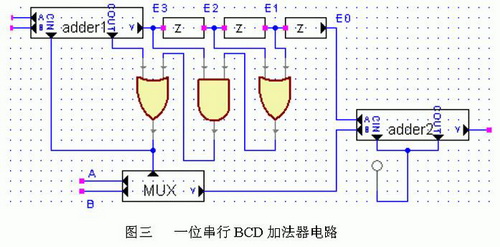

一位串行BCD加法器電路

圖三所示為一位串行BCD加法器。它是以犧牲速度以達到減少硬件邏輯門的目的,這種電路在對頻率要求不高的系統中非常之適用。其中ADDER1、ADDER2均為一位全加器。ADDER1 做主運算器,

2009-03-28 16:36:21 3233

3233

3233

3233

電子發燒友App

電子發燒友App

評論