車載電源線路用共模濾波器

2023-08-22 14:25:35 399

399

只要玩過VPS的小伙伴,對于CN2一詞肯定不會陌生。 但是對于新手來說,CN2是什么?CN2線路有哪些特點(diǎn)?與其它線路又有什么不同? 本期,我將簡要介紹CN2線路和普通線路之間的區(qū)別,以及CN2線

2023-07-24 16:41:08 314

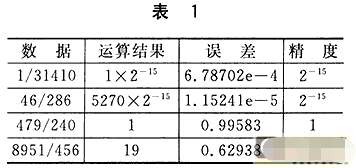

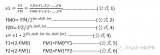

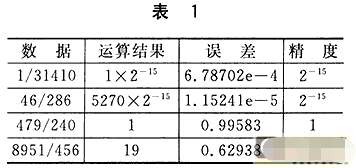

314 FPGA實(shí)現(xiàn)除法的方法有幾種,比如直接用/來進(jìn)行除法運(yùn)算,調(diào)用IP核進(jìn)行除法運(yùn)算,但這兩種方式都有個共同的問題——都是黑盒子,在進(jìn)行時序違例處理時,往往不好操作,比如想打打拍改善下時序都不知從何下手。

2023-07-04 10:03:39 236

236

本文是本系列的第四篇,本文主要介紹FPGA常用運(yùn)算模塊-除法器,xilinx提供了相關(guān)的IP以便于用戶進(jìn)行開發(fā)使用。

2023-05-22 16:20:45 924

924

;。電壓和電流的變化通過導(dǎo)線傳輸時有兩種形態(tài), 一種是兩根導(dǎo)線分別做為往返線路傳輸, 我們稱之為"差模";另一種是兩根導(dǎo)線做去路,地線做返回傳輸, 我們稱之為"共模"。

2023-05-10 14:19:17 466

466

python數(shù)字除法包括真除法(/)和floor除法(//),并且跟python版本相關(guān)。

2023-03-10 10:03:18 608

608 是有符號或者是無符號的,但分子分母必需是同類型的數(shù)據(jù)。請將32位的被除數(shù)放到MR(R4,R3)中,16位的除數(shù)放到R2中并清掉AQ標(biāo)志,然后就可以簡單的實(shí)現(xiàn)除法。復(fù)多次的執(zhí)行DIVQ,實(shí)際上是利用AQ

2009-09-21 09:26:57

NI Multisim 10經(jīng)典教程分享--除法與開平方運(yùn)算電路

2023-02-08 09:18:28 689

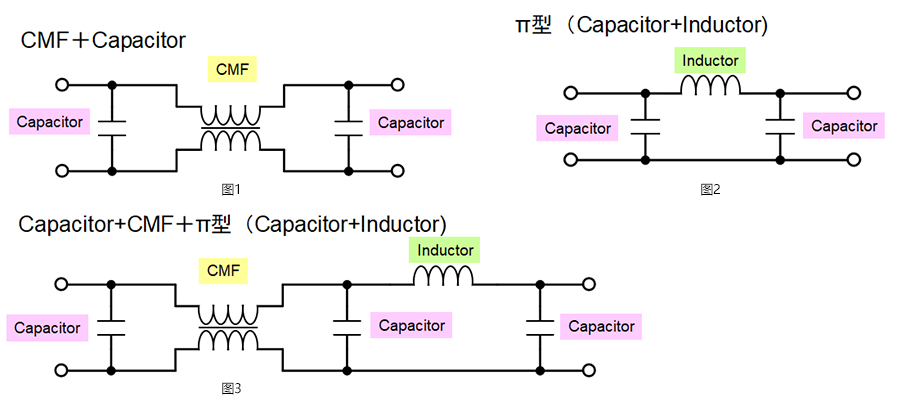

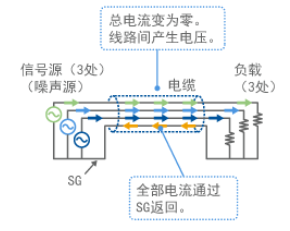

689 抑制共模噪聲的方法多種多樣,除了從源頭去減少共模噪聲外,通常我們抑制最常用的方法就是使用共模電感來濾除共模噪聲,也就是將共模噪聲阻擋在目標(biāo)電路外面。即在線路中串聯(lián)共模扼流器件。

2022-12-15 10:01:42 875

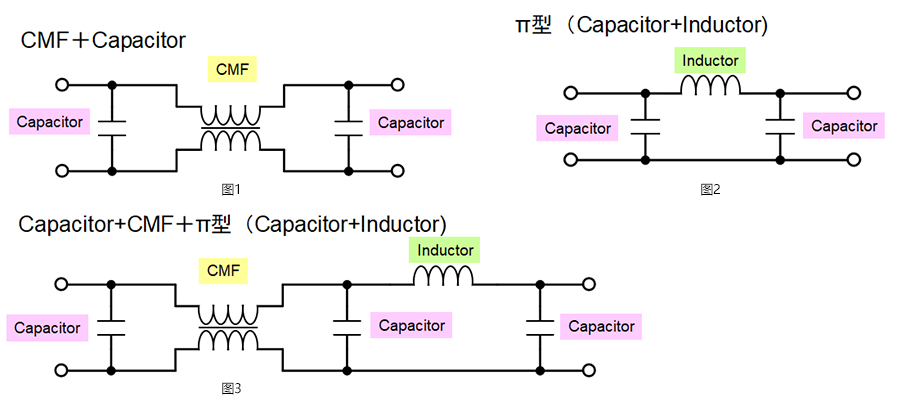

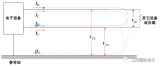

875 安全性和舒適性不斷增強(qiáng)的汽車搭載了很多電子設(shè)備。電子電路有信號線路和電源線路,需要分別采取防噪聲對策。TDK的共模濾波器的特點(diǎn)是可以根據(jù)用途分別提出多種產(chǎn)品陣容,準(zhǔn)備了追求小型薄型化的產(chǎn)品群、為了在車載用途中能應(yīng)對嚴(yán)格的環(huán)境條件,采用獨(dú)有端子結(jié)構(gòu)的產(chǎn)品群。本章將介紹電源線路用共模濾波器。

2022-11-04 09:21:45 997

997 抑制共模噪聲的方法多種多樣,除了從源頭去減少共模噪聲外,通常我們抑制最常用的方法就是使用共模電感來濾除共模噪聲,也就是將共模噪聲阻擋在目標(biāo)電路外面。即在線路中串聯(lián)共模扼流器件。

2022-09-09 14:18:32 1460

1460 ;。電壓和電流的變化通過導(dǎo)線傳輸時有兩種形態(tài), 一種是兩根導(dǎo)線分別做為往返線路傳輸, 我們稱之為"差模";另一種是兩根導(dǎo)線做去路,地線做返回傳輸, 我們稱之為"共模"。

2022-07-12 11:28:15 992

992 收音機(jī)噪聲免除法資料分享

2022-07-08 16:49:14 31

31 FPGA中的硬件邏輯與軟件程序的區(qū)別,相信大家在做除法運(yùn)算時會有深入體會。若其中一個操作數(shù)為常數(shù),可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運(yùn)算會占用較多的資源,電路結(jié)構(gòu)復(fù)雜,且通常無法在一個時鐘周期內(nèi)完成。因此FPGA實(shí)現(xiàn)除法運(yùn)算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 5168

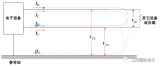

5168 線路中的噪聲電流以相同的方向流動,線路承受著相同的電壓,這種稱之為共模傳導(dǎo)。共模傳導(dǎo)經(jīng)由地線所保持負(fù)載的浮動靜電容量泄露的電流所導(dǎo)致,然后經(jīng)過地線回到噪聲源(也可能是負(fù)載和噪聲源之間的直接連接所導(dǎo)致而不經(jīng)過地線)。

2022-03-30 11:11:45 1385

1385

如何分辨海外服務(wù)器線路?購買海外服務(wù)器不像大陸服務(wù)器,不用糾結(jié)線路的選擇,海外服務(wù)器線路眾多,選擇不同線路對于海外服務(wù)器的性能也有影響,比較關(guān)鍵的是很多用戶都不太明白怎么分辨海外服務(wù)器的CN2

2022-03-17 16:04:11 1952

1952 匯編實(shí)現(xiàn)多字節(jié)乘除法乘法單片機(jī)的乘法本質(zhì)是二進(jìn)制的乘法,而乘法本身是通過加法實(shí)現(xiàn)的。多字節(jié)的乘法其實(shí)就是移位做加法。例如7x11,用二進(jìn)制豎式表示如下圖:可以看到,其實(shí)就是判斷乘數(shù)的每一位是1還是0

2021-11-15 17:21:03 18

18 4.3 實(shí)例九 除法器設(shè)計(jì)4.3.1. 本章導(dǎo)讀要求掌握除法器原理,并根據(jù)原理設(shè)計(jì)除法器模塊以及設(shè)計(jì)對應(yīng)的測試模塊,最后在 Robei可視化仿真軟件經(jīng)行功能實(shí)現(xiàn)和仿真驗(yàn)證。設(shè)計(jì)原理這個除法器的設(shè)計(jì)為

2021-11-07 10:51:04 17

17 針對魚眼鏡頭的高精度標(biāo)定需求,提岀一種基于除法畸變模型的線性標(biāo)定方法。通過除法模型將題轉(zhuǎn)換為線性方程組求解問題相機(jī)畸變中心后對畸變方程矩陣進(jìn)行解耦,分別求解相機(jī)內(nèi)外參數(shù)和畸變系數(shù)實(shí)現(xiàn)魚眼鏡頭的快速魯棒標(biāo)定。實(shí)驗(yàn)結(jié)果線性標(biāo)定方法相方法在保證標(biāo)定準(zhǔn)性和可靠性計(jì)算效率提高了約10倍。

2021-05-19 11:39:05 5

5 SSM2141:高共模抑制差動線路接收機(jī)數(shù)據(jù)表

2021-04-17 19:45:06 8

8 各種集成化單片數(shù)字信號處理器(DSP)以其功能強(qiáng)、集成度高、應(yīng)用靈活、性價(jià)比高等優(yōu)點(diǎn),在信號處理和系統(tǒng)控制中的主導(dǎo)性地位日益明顯。許多信號處理和控制需要運(yùn)用除法運(yùn)算。一般的數(shù)字信號處理器中沒有現(xiàn)成

2020-08-11 15:54:07 1345

1345

高、資源敏感而計(jì)算時延要求并不高,這時我們需要一種保證計(jì)算正確且資源開銷最低的FPGA實(shí)現(xiàn)方法,本文給出了實(shí)現(xiàn)乘除法、開方運(yùn)算的FPGA串行實(shí)現(xiàn)算法,并與LPM宏函數(shù)進(jìn)行了性價(jià)比比較。結(jié)果表明,本文給出的各算法計(jì)算準(zhǔn)確,資源量遠(yuǎn)小于調(diào)用LPM宏函數(shù)。

2020-07-29 17:48:57 1053

1053

除法運(yùn)算。很多人覺得不就是除法嘛,直接打上/即可,但是,F(xiàn)PGA是不能正確綜合這個除法器的,綜合的結(jié)果只是一個固定數(shù)值,而不像其他微處理器。可以這么說,用FPGA實(shí)現(xiàn)除法運(yùn)算是比較麻煩的。

2020-06-17 10:17:27 6157

6157

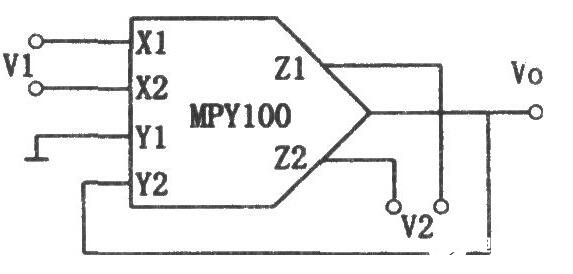

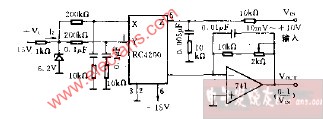

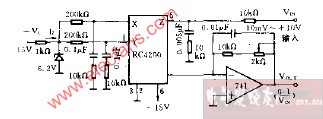

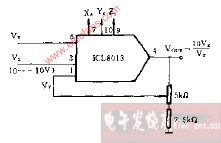

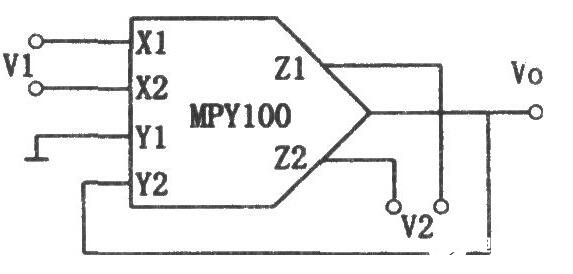

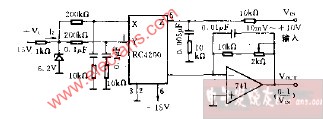

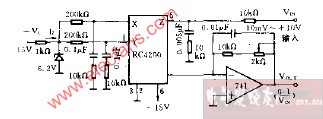

輸入信號為V1、V2,輸出Vo為Vo=10V2/V1。這種除法器是將乘法器接在運(yùn)算放大器的反院回路組成的。V1的輸入范圍為-0.2V到10V,V2的輸入范圍為-10V到10V。

2019-12-31 14:12:44 15859

15859

電壓電流的變化通過導(dǎo)線傳輸時有二種形態(tài),我們將此稱做“共模”和“差模”。設(shè)備的電源線、電話等的通信線、與其它設(shè)備或外圍設(shè)備相互交換的通訊線路,至少有兩根導(dǎo)線,這兩根導(dǎo)線作為往返線路輸送電力或信號。

2018-10-29 16:17:21 11302

11302

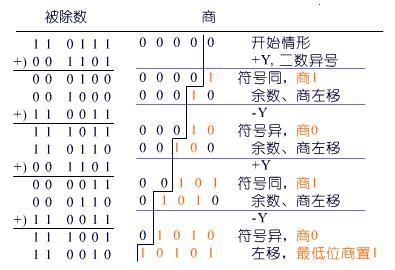

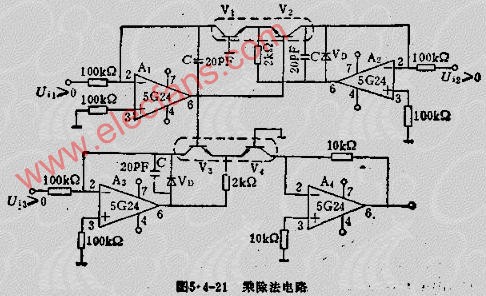

單片機(jī)中的除法也是二進(jìn)制的除法,和現(xiàn)實(shí)中數(shù)學(xué)的除法類似,是從被除數(shù)的高位開始,按位對除數(shù)進(jìn)行相處取余的運(yùn)算,得出的余數(shù)再和之后的被除數(shù)一起再進(jìn)行新的相除取余的運(yùn)算,直到除不盡為止,因?yàn)閱纹瑱C(jī)中的除法是二進(jìn)制的,每個步驟除出來的商最大只有1,所以我們實(shí)際編程時可以把每一步的除法看作減法運(yùn)算。

2018-05-31 08:51:02 5408

5408

通常無法在一個時鐘周期內(nèi)完成。因此FPGA實(shí)現(xiàn)除法運(yùn)算并不是一個“/”號可以解決的。 好在此類基本運(yùn)算均有免費(fèi)的IP核使用,本人使用的VIVADO 2016.4開發(fā)環(huán)境提供的divider gen IP核均采用AXI總線接口,已經(jīng)不再支持native接口。

2018-05-18 01:15:00 3961

3961 為確保安全苛求系統(tǒng)中程序執(zhí)行的正確性,研究人員將差錯控制理論用于對計(jì)算機(jī)指令進(jìn)行編碼,但由于編碼大多涉及模運(yùn)算,導(dǎo)致復(fù)雜度大量增加,應(yīng)用于實(shí)時系統(tǒng)有困難。針對復(fù)雜度問題對delta碼的乘除法運(yùn)算

2017-12-04 16:44:29 0

0 乘法器,求模運(yùn)算部分利用Barrett約減運(yùn)算,用硬件描述語言進(jìn)行FPGA設(shè)計(jì)與實(shí)現(xiàn),避免了除法運(yùn)算。對于192位的操作數(shù),完成Barrett模乘需要約186個時鐘周期,計(jì)算速率可以達(dá)到269.17 Mb/s。

2017-11-08 15:18:19 32

32 的磁場H1、H2,此時工作電流主要受線圈歐姆電阻以及可以忽略不計(jì)的工作頻率下小漏感的阻尼,所以差模信號可以無衰減地通過,如上圖所示;而當(dāng)流過共模電流時,磁環(huán)中的磁通相互疊加,從而具有相當(dāng)大的電感量

2017-10-30 09:00:11 12377

12377

14.2 除法運(yùn)算 因?yàn)锳RM體系結(jié)構(gòu)本身并不包含除法運(yùn)算硬件,所以在ARM上實(shí)現(xiàn)除法是十分耗時的。ARM指令集中沒有直接提供除法匯編指令,當(dāng)代碼中出現(xiàn)除法運(yùn)算時,ARM編譯器會調(diào)用C庫函數(shù)(有符合

2017-10-17 17:22:29 5

5 計(jì)算機(jī)如何來計(jì)算除法的?

第一步:分析除法

第二步,計(jì)算機(jī)中對第一步的模擬(真值)

2015-12-31 10:43:18 15

15 模擬除法器是一種能實(shí)現(xiàn)兩個模擬量相除的電子器件。目前不僅應(yīng)用于模擬運(yùn)算方面,而且已擴(kuò)展到無線通訊、電視廣播、人工神經(jīng)網(wǎng)路、機(jī)器人控制技術(shù)等領(lǐng)域。此外,模擬除法器在模糊控制和測量儀表中也是非常重要的器件。

2014-09-19 15:14:31 2946

2946 輾轉(zhuǎn)相除法是整數(shù)和多項(xiàng)式理論中求最大公因數(shù)和最大公因式的一類重要方法,對于較大的兩個整數(shù)和次數(shù)較高的兩個多項(xiàng)式而言,利用輾轉(zhuǎn)相除法手動計(jì)算它們的最大公因數(shù)和最大公

2013-06-06 10:54:26 16

16 除法器是電子技術(shù)領(lǐng)域的基礎(chǔ)模塊,在電子電路設(shè)計(jì)中得到廣泛應(yīng)用。目前,實(shí)現(xiàn)除法器的方法有硬件實(shí)現(xiàn)和軟件實(shí)現(xiàn)兩種方法。硬件實(shí)現(xiàn)的方法主要是以硬件的消耗為代價(jià),從而有實(shí)

2012-05-24 09:41:04 1757

1757

FPGA實(shí)現(xiàn)鐵軌檢測算法設(shè)計(jì)_本文將闡述如何用乘法運(yùn)算代替除法運(yùn)算,以及如何使除法的次數(shù)最少化。

2011-10-05 16:37:19 10528

10528

介紹一種在 8096 /96 系列單片機(jī)上實(shí)現(xiàn)的單精度 浮點(diǎn)數(shù) 快速除法。該算法采用了預(yù)估一修正的數(shù)值計(jì)算方法,并充分利用了16 位CPU 中的乘除法指令,計(jì)算速度快、精度高,有很強(qiáng)的實(shí)用

2011-06-03 16:47:06 93

93 對TMS320C3X中浮點(diǎn)數(shù)除法的實(shí)現(xiàn)方法進(jìn)行了詳細(xì)討論,并給出匯編子程序。浮點(diǎn)數(shù)除法首先利用牛頓迭代法求出除數(shù)的倒數(shù),然后再與被除數(shù)相乘,從而得出結(jié)果。該設(shè)計(jì)思想已經(jīng)應(yīng)

2010-08-05 16:34:51 17

17 高精度的乘除法和開方等數(shù)學(xué)運(yùn)算在FPGA實(shí)現(xiàn)中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計(jì)算時延要求較低的應(yīng)用中,以處理時間換取資源的串行運(yùn)算方法具有廣泛的應(yīng)

2010-07-28 18:05:14 37

37 在FPGA中實(shí)現(xiàn)高精度快速除法

2010-07-17 16:33:18 25

25 用于比率計(jì)算的除法運(yùn)算電路

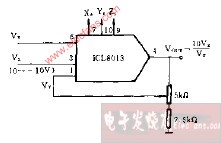

電路的功能

本電路是用X除輸入信號Z

2010-05-08 15:29:01 1562

1562

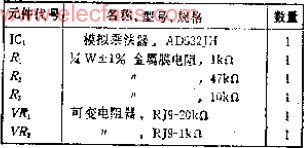

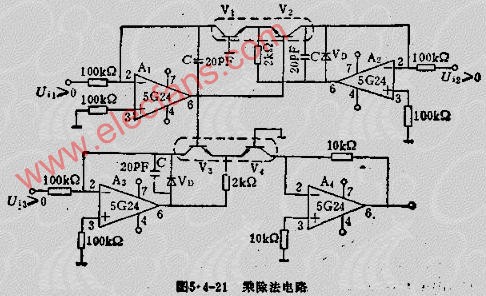

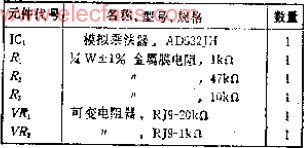

乘除法電路

圖5.4-21是乘除法運(yùn)算實(shí)用電路之一。

1、A

2010-04-26 16:11:49 16002

16002

除法器對數(shù)運(yùn)算電路的應(yīng)用

由對數(shù)電路實(shí)現(xiàn)除法運(yùn)算的數(shù)學(xué)原理是:

2010-04-24 16:07:27 2366

2366

原碼除法運(yùn)算原理是什么? 兩個原碼表示的數(shù)相除時,商的符號由兩數(shù)的符號按位相加求得,商的數(shù)值部分由兩數(shù)的數(shù)值部分相除求得。 設(shè)有n位定

2010-04-13 11:15:45 11412

11412 并行除法器 ,并行除法器結(jié)構(gòu)原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運(yùn)算部件,采用大規(guī)模集成

2010-04-13 10:46:30 14405

14405 模2n加整體逼近模2 加產(chǎn)生的噪聲函數(shù)的概率分布研究:該文證明了模2n 加變換以6 種不同的方式整體逼近模2 加時產(chǎn)生的噪聲函數(shù)取值概率的數(shù)值分布相同,給出了6 種噪聲函數(shù)的概率

2009-10-29 13:10:26 20

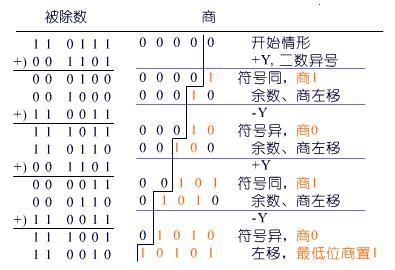

20 定點(diǎn)補(bǔ)碼一位除法的實(shí)現(xiàn)方案 與補(bǔ)碼乘法類似,也可以用補(bǔ)碼直接完成除法運(yùn)算,即用 [X]補(bǔ)/[Y] 補(bǔ) 直接求得[X/Y]補(bǔ) 。補(bǔ)碼除法的規(guī)則比原碼除

2009-10-13 22:58:39 2865

2865

除法運(yùn)算電路圖

2009-07-20 12:10:07 691

691

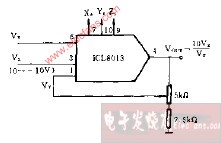

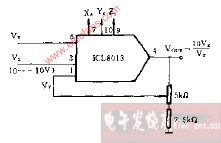

采用ICL8013的除法運(yùn)算電路圖

2009-07-20 12:02:08 610

610

除法運(yùn)算電路圖

2009-07-17 11:26:48 3856

3856

采用ICL8013的除法運(yùn)算電路圖

2009-07-17 11:23:30 804

804

摘要: 介紹了在PPGA芯片上實(shí)現(xiàn)數(shù)字頻率計(jì)的原理。對各種硬件除法進(jìn)行了比較,提出了高速串行BCD碼除法的硬件算法,并將其應(yīng)用在頻率計(jì)設(shè)計(jì)中。

2009-06-20 14:48:14 1147

1147

收錄機(jī)“咯”聲消除法

2009-04-23 11:37:47 748

748

在許多定點(diǎn)DSP芯片中,一般不提供單周期的除法指令;而在實(shí)際應(yīng)用中,又常常要用到除法運(yùn)算,因此如何利用簡單的指令來實(shí)現(xiàn)除法是一個非常重要的問題。本文對定點(diǎn)除法算法

2009-04-16 14:03:07 48

48 在橢圓曲線密碼體制中,有限域GF(2m)中模逆運(yùn)算是最重要的運(yùn)算之一。在分析一種通用有限域GF(2m)模逆算法的基礎(chǔ)上,提出改進(jìn)算法。改進(jìn)算法減少了原算法快速實(shí)現(xiàn)時的缺點(diǎn),能

2009-04-16 10:02:40 30

30 MCS51三字節(jié)無符號除法程序(ASM)

;三字節(jié)無符號除法程序(R2R3R4/R7)=(R2)R3R4 余數(shù)R7;入口 :R2,R3,R4,R7;占用資源:ACC,B,F0;堆

2009-01-16 11:54:07 1043

1043 51單片機(jī)的高精度除法程序及使用

開發(fā)人員在開發(fā)51單片機(jī)應(yīng)用系統(tǒng)過程中,往往遇到多字節(jié)除法及倒數(shù)問題。但目前一些資料中所介紹的有關(guān)程序,復(fù)

2008-09-09 10:12:28 1983

1983

電子發(fā)燒友App

電子發(fā)燒友App

評論