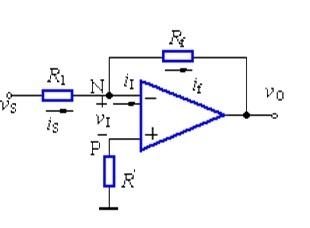

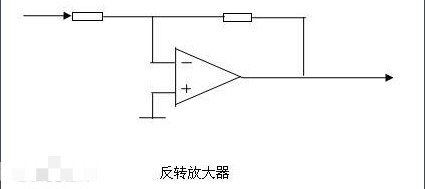

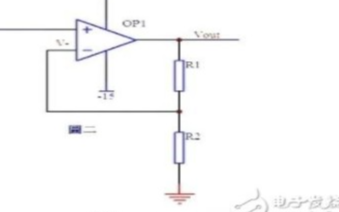

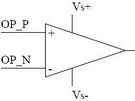

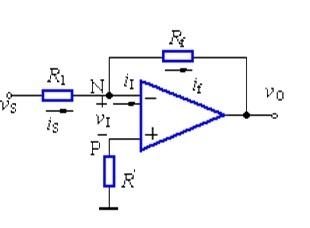

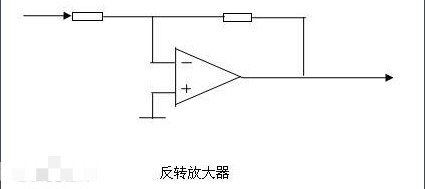

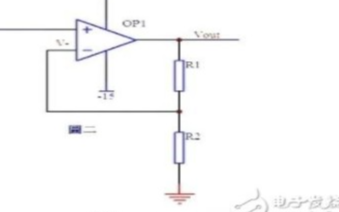

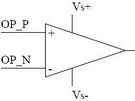

的直流放大器,若在運算放大器的輸入端與輸出端之間加上適當的反饋網絡,便可以實現不同的電路功能。例如,加入線性負反饋網絡,可以實現信號的放大功能以及加、減、微分、積分等模擬運算功能;加入非線性負反饋網絡

2008-09-22 13:09:28

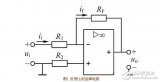

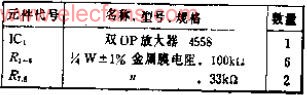

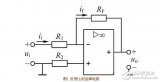

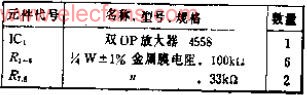

?內容包括虛短和虛斷理解,反相、同相比例運算放大電路,電壓跟隨器,相關運算電路(加、減、乘、除、積分、微分、對數與指數等),差分放大電路,I/V、V/I轉換電路,電壓抬升電路,F/V轉換電路,有源濾波器,移相電路,電壓源等。

2023-09-08 11:38:17 2296

2296

電子發燒友網站提供《帶有初始化信號的0-9加/減計數器.zip》資料免費下載

2023-06-16 14:39:59 0

0 加、減 使用補碼時,加減法可以統一,因而對加減不加區分,對有無符號也不加以區分。

2023-06-06 17:07:59 393

393

本文是本系列的第三篇,本文主要介紹FPGA常用運算模塊-乘加器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:17:12 522

522

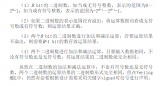

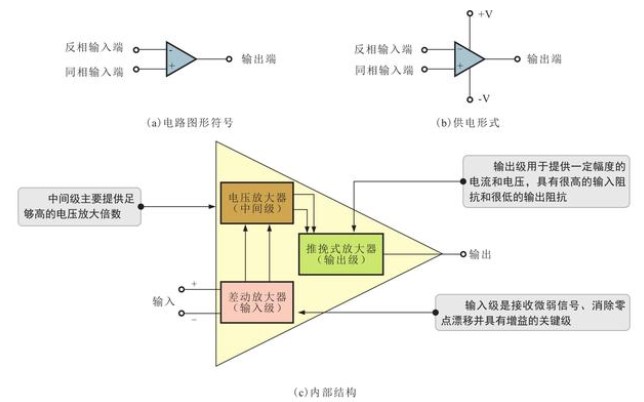

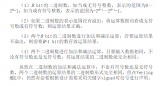

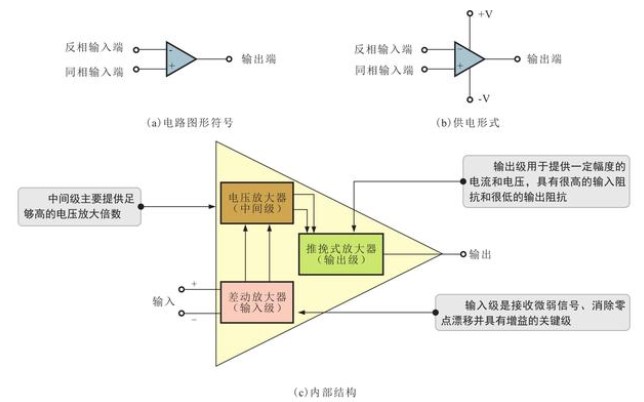

OP放大器 (Operational Amplifier)即運算放大器 (簡稱運放”) 是具有很高放大倍數的電路單元。在實際電路中通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2023-02-22 09:25:36 4967

4967

運算放大器(簡稱“運放”)是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。由于早期應用于模擬計算機中用以實現數學運算,因而得名“運算放大器”。

2023-02-21 17:54:58 1296

1296

運算放大器(簡稱“運放”)是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2023-01-10 10:16:55 1006

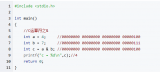

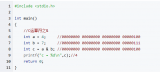

1006 基本算術運算符:+(加)、-(減)、*(乘)、/(右除)、(左除)、^(乘方)。

2022-11-14 16:01:53 384

384

運算放大電路是具有很高放大倍數的電路單元,可以進行加、減等運算,用途十分廣泛。運算放大電路的電路圖形符號、供電形式及內部結構如圖7-25所示。

2022-08-16 15:39:19 2028

2028

4位補碼可表示的整數的數值范圍是十進制-8~7.

1000 → -8;

1001 → -7;

1010 → -6;

1011 → -5;

2022-06-06 09:37:29 0

0 a為10,變量b為20: 運算符 描述 實例 + 加 - 兩個對象相加 a + b 輸出結果 30 - 減 - 得到 負數或是一個數減

2022-02-21 16:44:21 1507

1507 、十進制調整指令DA A六、加一減一指令INC XXXDEC XXX前言1.算術指令包括加、減、乘、除基本四則運算2.在邏輯運算單元(ALU)中能進行加、減、乘、除、加1,減1,BCD數轉十進制調整等...

2021-11-23 16:21:11 7

7 奇偶校驗來說A中“1”的個數為奇則P=1,偶P=0;以A為目的操作數的算術運算和邏輯運算指令ADD:加ADDC:進位加SUBB:借位減ANL:與ORL:或XRL:異或源操作數只有兩種:Rn、dir、@Ri、#data(立即數)以上的指令都是以A為目的操作數,例如:ADD A,@Ri以d

2021-11-23 16:21:11 2

2 ,在浮點類型轉換為整數類型時精度丟失,后面取整取余的時候再調整回來就好了。+0.5是為了四舍五入,計算機小數是直接舍棄的。關于溫度負值的處理"取反后加一"和"減一后取反"結果是相同的。取反后加一:原碼=補碼的補碼減一后取反:補碼的逆運算//基于51單片

2021-11-21 12:06:08 8

8 Keil C51基礎之運算符詳解一. 算術運算符 包括加(+)、減(-)、乘(*)、除(/)、取模 (%)、自加(++)、自減(--)。 示例: 5 % 3; 結果: 2 char a = 5

2021-11-21 11:21:03 13

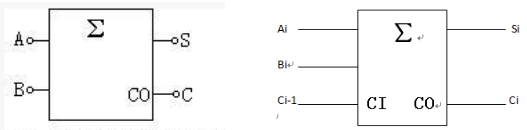

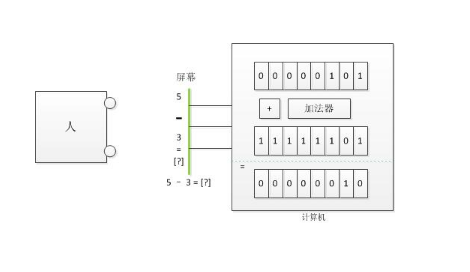

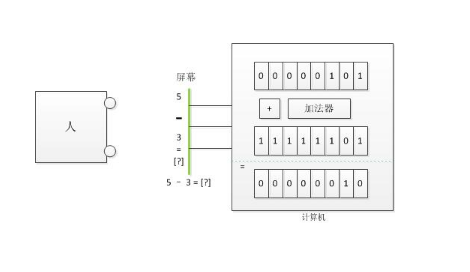

13 人類在制造出晶體管后,利用晶體管制造出了與非門,然后又利用與非門制造出了加法器。加法器解決了加法運算問題。只有加法器是不夠的,還需要解決減法的計算問題,但是與加法器相比,設計減法器硬件更為復雜

2021-09-12 16:06:43 5873

5873 本篇文章講解了計算機的原碼, 反碼和補碼。 并且進行了深入探求了為何要使用反碼和補碼, 以及更進一步的論證了為何可以用反碼, 補碼的加法計算原碼的減法。 論證部分如有不對的地方請各位牛人幫忙指正

2020-09-15 15:23:49 994

994 。

補碼:正數的補碼還是其本身;負數的補碼是在其原碼的基礎上,符號位保持不變,其余位取反,最后+1。即反碼加1。

2020-02-12 15:28:29 7795

7795 A)算術和邏輯運算,可對半字節(一個字節是8位,半個字節就是4位)和單字節數據進行操作。

B)加、減、乘、除、加1、減1、比較等算術運算。

C)與、或、異或、求補、循環等邏輯運算。

D)位處理功能(即布爾處理器)。

2019-09-14 17:20:00 3952

3952 運算放大器(簡稱“運放”)是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2019-04-01 17:01:25 12393

12393 算術運算指令(Arithmetic)8086/8088提供加、減、乘、除算術操作;

特點:大部分都影響標志位,不同指令影響不同:(1) 加、減法指令影響 SF,ZF,AF,PF,CF,OF;(2

2018-09-05 15:12:36 11

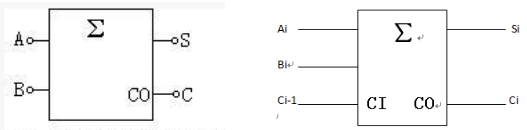

11 計算機最基本的任務之一是進行算數,在機器中四則運算——加、減、乘、除——都是分解成加法運算進行的,因此加法器便成為計算機中最基本的運算單元。

2018-07-25 15:14:09 37176

37176

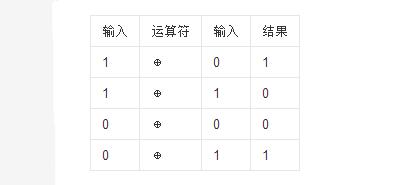

C語言位運算有6種: &, | , ^(亦或), (右移)。

注意:參與位運算的元素必須是int型或者char型,以補碼形式出現。

2018-03-22 16:00:24 8156

8156

BCD碼的運算規則:BCD碼是十進制數,而運算器對數據做加減運算時,都是按二進制運算規則進行處理的。這樣,當將 BCD碼傳送給運算器進行運算時,其結果需要修正。

2018-03-02 09:53:08 52230

52230

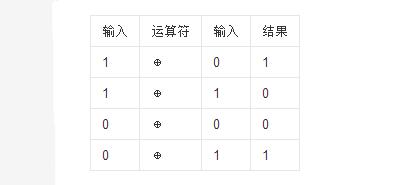

異或是一個數學運算符應用于邏輯運算本文開始介紹了異或運算的定義與異或運算規則,其次介紹了異或運算的作用,最后介紹了異或運算經典應用。

2018-03-01 14:22:01 36752

36752

我們平時說出或寫出某“數”,一般都是在十進制下,用10個不同的“碼”(此處的“碼”還和原碼補碼反碼的概念不同)來表示。分別是0~9。超過9,也就是比最大的碼還大的數,采用進位的方式來表示。于是有了“位”的概念。即個位,十位,百位等等。

2018-02-28 16:03:14 16524

16524

描述了浮點型算法的加、減、乘、除的verilog代碼,編寫了6位指數位,20位小數位的功能實現并且通過仿真驗證

2018-01-16 14:15:54 1

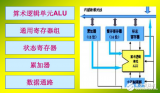

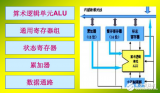

1 運算器由算術邏輯單元(ALU)、累加器、狀態寄存器、通用寄存器組等組成。算術邏輯運算單元(ALU)的基本功能為加、減、乘、除四則運算,與、或、非、異或等邏輯操作,以及移位、求補等操作。

2017-11-15 14:37:50 25969

25969

運算器:arithmetic unit,計算機中執行各種算術和邏輯運算操作的部件。運算器的基本操作包括加、減、乘、除四則運算,與、或、非、異或等邏輯操作,以及移位、比較和傳送等操作,亦稱算術邏輯部件(ALU)。

2017-11-14 21:45:30 8008

8008

運算放大器(簡稱“運放”)是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2017-05-22 14:25:08 27378

27378

運算放大器(簡稱“運放”)是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2017-05-15 14:49:03 9464

9464

具體詳細介紹初入門C語言源碼補碼,通俗易懂,一目了然。

2015-11-19 15:23:39 1

1 通過發射波形的設計可以提高MIMO雷達性能。偽隨機編碼容易構造,但具有較高的互相關和自相關旁瓣的缺點。Frank補碼序列具有良好的相關特性,其距離旁瓣較低,可用于目標成像。

2011-10-19 15:08:54 24

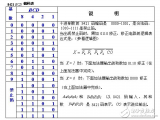

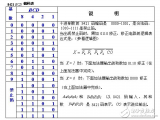

24 邏輯代數的運算規則 邏輯代數的基本定律

2010-09-19 11:16:51 6010

6010 集成運算放大器是一種高倍率的直流放大器。當選取不同的反饋電路時,它就可以對信號進行放大以及加,減微分,積分等運算。

2010-09-19 10:36:12 167

167 補碼解釋及運算

2010-06-30 10:36:55 5966

5966 摘要:本文主要介紹了集成運算放大器的種類、性質、應用、使用方法等方面。 例如利用集成運算放大器可非常方便的完成信號放大、信號運算(加、減、乘、除、對數、反對數、

2010-06-17 16:17:24 79

79 由輸入端選擇運算方式的加、減法運算電路

電路的功能

這是一種配

2010-05-08 11:32:23 1477

1477

二進制數值數據的編碼與運算算法

一、原碼、反碼、補碼的定義

1、原碼的定義

2、補碼的定義

2010-04-15 14:42:03 2423

2423 補碼一位乘法原理詳解

2010-04-13 14:12:41 16011

16011

補碼減法,補碼減法原理是什么? 負數的減法運算也要設法化為加法來做,其所以使用這種方法而不使用直接減法,是因為它可以和常規的加法運算使用同一

2010-04-13 11:45:46 6080

6080 補碼加法,補碼加法計算原理 負數用補碼表示后,可以和正數一樣來處理。這樣,運算器里只需要一個加法器就可以了,不必為了負數的加法運算,再配一個減

2010-04-13 11:41:28 16742

16742 多功能算術/邏輯運算單元(ALU) ,什么是多功能算術/邏輯運算單元(ALU)

由一位全加器(FA)構成的行波進位加法器,它可以實現補碼數的加法運算和減法運算。但是這種加法/

2010-04-13 11:24:11 25416

25416 補碼乘法,補碼乘法計算詳細解說 1.補碼與真值得轉換公式 補碼乘法因符號位參與運算,可以完成補碼數的“直接”乘法,而不需要求補級

2010-04-13 11:05:06 34913

34913 邏輯運算,什么是邏輯運算 計算機中除了進行加、減、乘、除等基本算術運算外,還可對兩個或一個邏輯數進行邏輯運算。所謂邏輯數,是指不帶符號的二進制

2010-04-13 10:48:38 29945

29945 HT MCU 加、減、乘、除法文件編碼:HA0014s簡介:本程序包含八位、十六位、二十四位及三十二位定點數據的基本運算。基本的運算包括:加法(有符號、無符號)、減法

2010-03-26 08:34:21 21

21 運算器,運算器的作用和原理是什么?

運算器:arithmetic unit,計算機中執行各種算術和邏輯運算操作的部件。運算器的基本操作包括加、減、乘、除四

2010-03-24 17:01:07 30372

30372 運算放大器是具有很高放大倍數的電路單元。在實際電路中,通常結合反饋網絡共同組成某種功能模塊。它是一種帶有特殊耦合電路及反饋的放大器。其輸出信號可以是輸入信號加、減或微分、積分等數學運算的結果。

2010-03-09 15:32:51 233688

233688

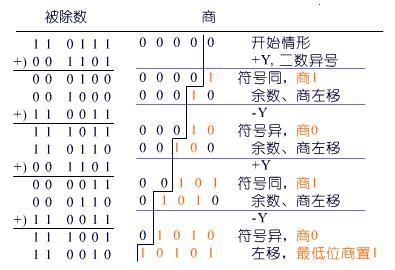

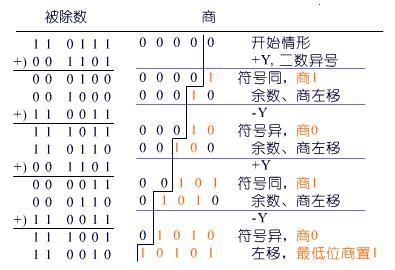

定點補碼一位除法的實現方案 與補碼乘法類似,也可以用補碼直接完成除法運算,即用 [X]補/[Y] 補 直接求得[X/Y]補 。補碼除法的規則比原碼除

2009-10-13 22:58:39 2865

2865

實現補碼加減運算的邏輯電路

運算前,X、Y寄存器分別存儲被加(減)數 和 加(減)數,計算結果存回X寄存器;F為加法器,能在命令X→F和Y→F信

2009-10-13 22:44:55 9442

9442

二進制數的運算規則 二進制數之間可以執行算術運算和邏輯運算,其規則簡單,容易實現。 (1) 加法運算規則 0 + 0 = 0 例如:

2009-10-13 16:24:15 21600

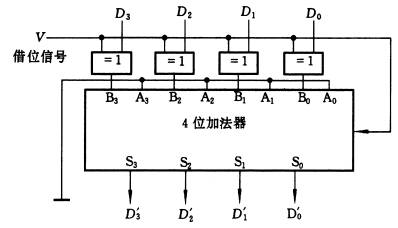

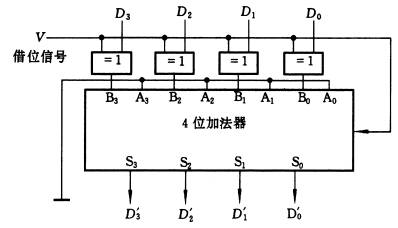

21600 減法運算

同加法運算一樣,減法運算可采用減法器來實現。半減器和全減器的設計方法和步驟與設計加法器相同。實用上,為了簡化系統結構,通常不另外設計減

2009-04-07 10:38:39 12577

12577

算術運算指令

MCS-51具有強大的加、減、乘、除四則算術運算指令。

1.程序狀態字PSW

MCS-51有一個程序狀態字寄存器PSW,用來保存指令執行結果的標志,供

2009-03-14 15:33:59 1884

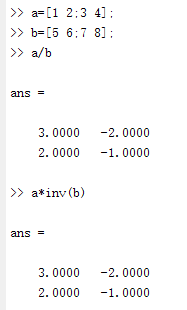

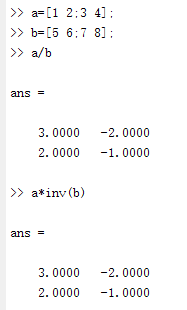

1884 matlab關系運算符

算數運算符

+ 矩陣加 - 減 * 乘 .* 數組乘 ^ 矩陣乘方 .^ 數

2008-06-18 14:47:16 2687

2687 算術運算指令共有24條,算術運算主要是執行加、減、乘、除法四則運算。另外MCS-51指令系統中有相當一部分是進行加、減1操作,BCD碼的運算和調整,我們都歸類為運算指令。雖然MC

2006-04-03 22:44:21 1194

1194

電子發燒友App

電子發燒友App

評論