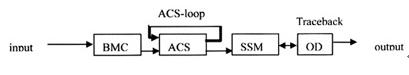

主要有代數譯碼和概率譯碼兩種。代數譯碼根據卷積碼自身的代數結構進行譯碼,計算簡單;概率譯碼則在計算時考慮信道的統計特性,計算較復雜,但糾錯效果好得多。典型的算法如:Viterbi 譯碼、序列譯碼等

2008-05-28 15:03:31

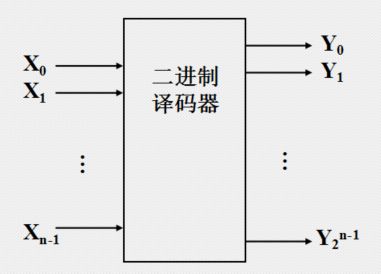

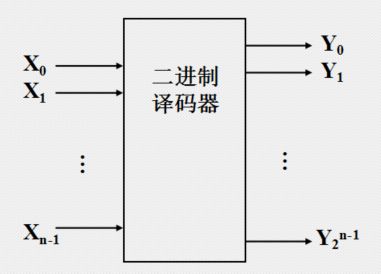

輸入:二進制代碼,有n個;

輸出:2^n 個特定信息。

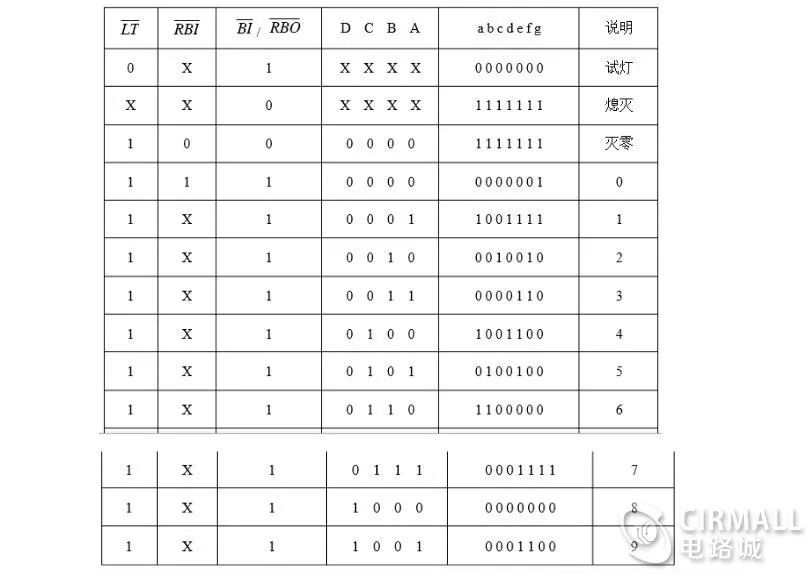

1.譯碼器電路結構

以2線— 4線譯碼器為例說明

2線— 4線譯碼器的真值表為:

2023-04-30 16:29:00 684

684

譯碼器的邏輯功能是將每個輸入的二進制代碼譯成對應的輸出的高、低電平信號。常用的譯碼器電路有二進制譯碼器、二--進制譯碼器和顯示譯 碼器。譯碼為編碼的逆過程。它將編碼時賦予代碼的含義“翻譯”過來。實現

2023-04-26 15:39:40 2201

2201

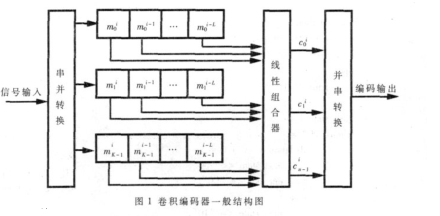

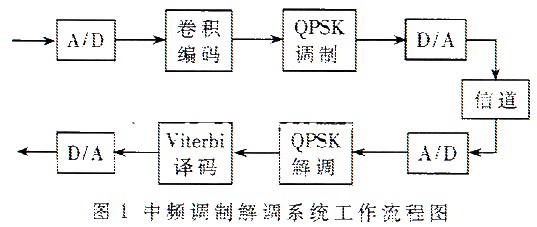

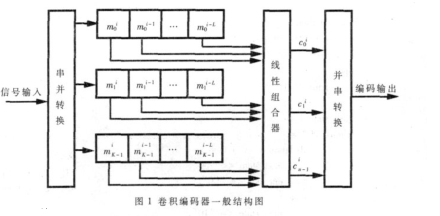

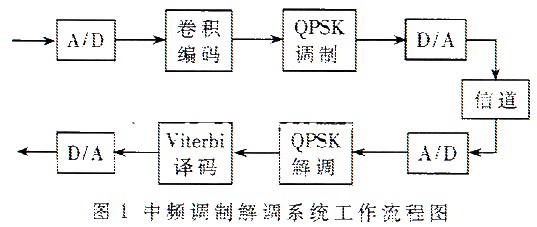

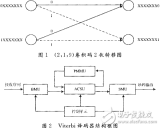

卷積碼是一種信道糾錯編碼,在通信中具有廣泛的應用。在發送端根據生成多項式進行卷積碼編碼,在接收端根據維特比(Viterbi)譯碼算法進行譯碼,能夠有效抵抗信道噪聲的影響,在誤碼率門限之下可以對傳輸過程中發生的突發錯誤進行糾錯。

2022-04-28 15:02:12 7304

7304 介紹并用VHDL語言實現了卷積編碼和維特比譯碼。根據編碼器特征設計了一種具有針對性的簡潔的維特比譯碼器結構,

2021-05-12 15:22:41 1868

1868

為了滿足復雜的無線通信系統功耗以及性能要求,提出并設計了一種指針反饋式Viterbi譯碼器。該譯碼器使相鄰時刻的

2021-04-28 09:35:41 1378

1378

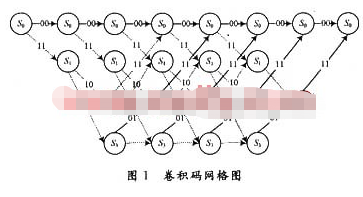

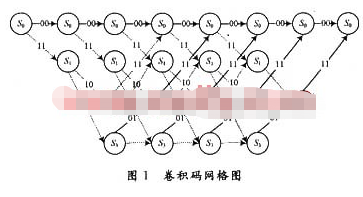

由于卷積碼優良的性能,被廣泛應用于深空通信、衛星通信和2G、3G移動通信中。卷積碼有三種譯碼方法:門限譯碼、概率譯碼和Viterbi算法,其中Viterbi算法是一種基于網格圖的最大似然譯碼算法

2020-08-11 17:41:23 605

605

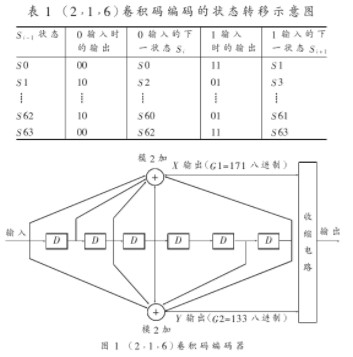

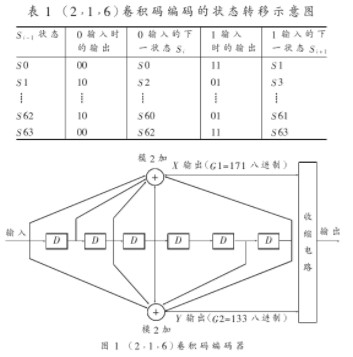

記(n0,k0,m)為卷積碼編碼器,該編碼器共有2k0×m個狀態,Viterbi譯碼器必須具備同樣的2k0×m個狀態發生器,且每個狀態必須有一個存儲路徑度量值的存儲器和一個存儲幸存路徑信息的存儲器,所以Viterbi譯碼器的復雜度呈2k0×m指數增長。

2020-07-15 20:53:51 1238

1238

隨著現代無線通信系統日益復雜化的發展,無線基帶通信系統中各模塊的實際性能、延時、功耗等參數成為基帶設計的重要考慮因素。Viterbi譯碼器廣泛應用于無線局域網和移動通信系統,并且作為基帶系統的重要

2019-10-06 11:09:00 323

323

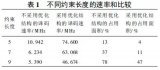

新一代移動通信系統目前主要采用多載波傳輸技術, 基帶傳輸速率較3G 有很大提高, 一般要求業務速率能達到30 Mb/ s 以上。約束長度卷積碼以及Viterbi譯碼器由于其性能和實現的優點, 在

2019-10-06 10:16:00 1753

1753

信道的是二進制信號序列。為了充分利用信道輸出信號的信息,提高傳輸系統譯碼的可靠性,首先把信道的輸出信號量化,將Q電平量化序列輸入Viterbi譯碼器,因此本文采用的VB譯碼算法為軟判決譯碼算法。

2019-07-11 08:01:00 2571

2571

和Viterbi譯碼是廣泛使用的信道編碼技術,具有一定的克服突發錯誤的能力,可以降低信道的誤碼率,帶來很高的編碼增益。

2019-05-13 08:04:00 5830

5830

卷積碼是廣泛應用于衛星通信、無線通信等各種通信系統的信道編碼方式。Viterbi算法是一種最大似然譯碼算法。在碼的約束度較小時,它比其它概率譯碼算法效率更高、速度更快,譯碼器的硬件結構比較簡單。隨著

2019-04-24 08:29:00 2438

2438

極化碼的譯碼算法研究近年來發展迅速,其中成為研究熱點的連續刪除(Successive Cancellation,SC)譯碼算法的基本思想是通過對信息位的比特似然概率值的判斷來進行譯碼。

2019-01-06 11:19:55 4472

4472

由網格圖的輸入支路特點分析可知,產生任意一個狀態節點Si的輸入條件mi是確定的,即mi=‘1’,i為偶數;mi=‘0’,i為奇數。輸入條件mi表示譯碼器最終需要輸出的比特信息。此外,譯碼器所要找的留選路徑是不同狀態的組合。

2018-10-02 01:07:16 4926

4926 在大多數無線通信系統中,卷積編碼是最好的方法。糾錯編碼以克服傳輸失真。這份報告概述了這一理論。卷積編碼和譯碼,解釋維特比的編程技術TI TMS3C35X數字信號處理器的解碼(DSPs)相同的基本方法對任何卷積碼進行譯碼。本申請報告用一般的觀點來考察問題,而不是為特定的問題勾勒出解決方案。

2018-04-25 09:47:38 3

3 本文主要介紹了譯碼器的分類和應用。譯碼器指的是具有譯碼功能的邏輯電路,譯碼是編碼的逆過程,它能將二進制代碼翻譯成代表某一特定含義的信號(即電路的某種狀態),以表示其原來的含義。譯碼器可以分為:變量

2018-04-04 11:51:12 35527

35527

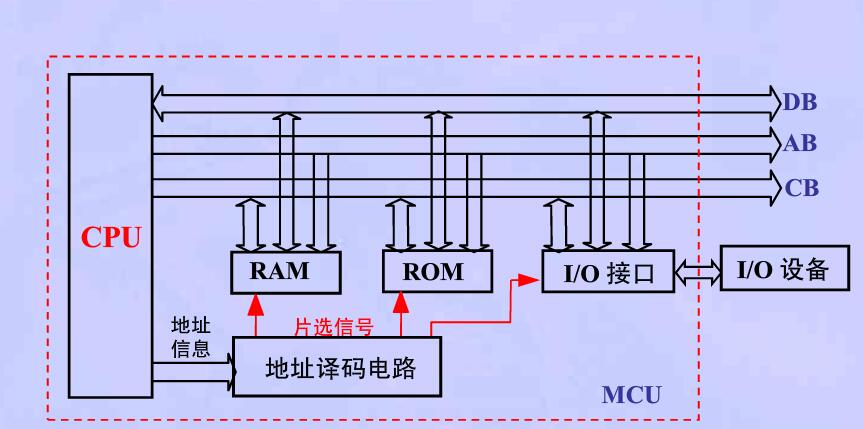

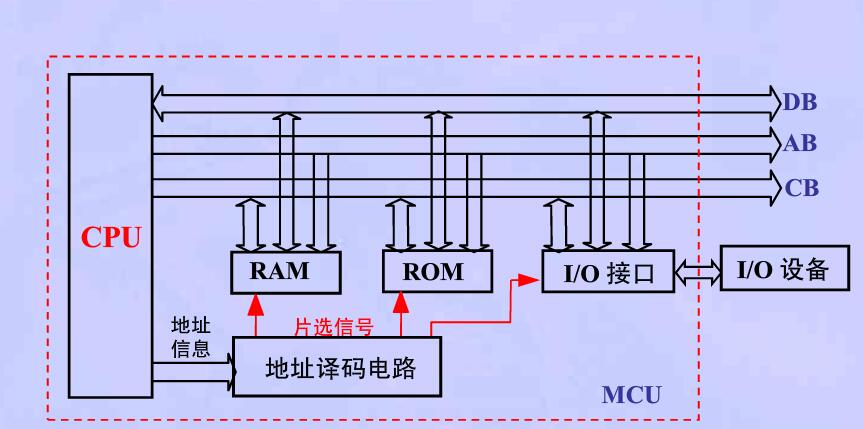

地址譯碼有兩種方式,一種是單譯碼方式,或稱為字結構方式;另一種是雙譯碼方式,或稱為X-Y譯碼結構。

2018-03-02 16:11:02 9355

9355

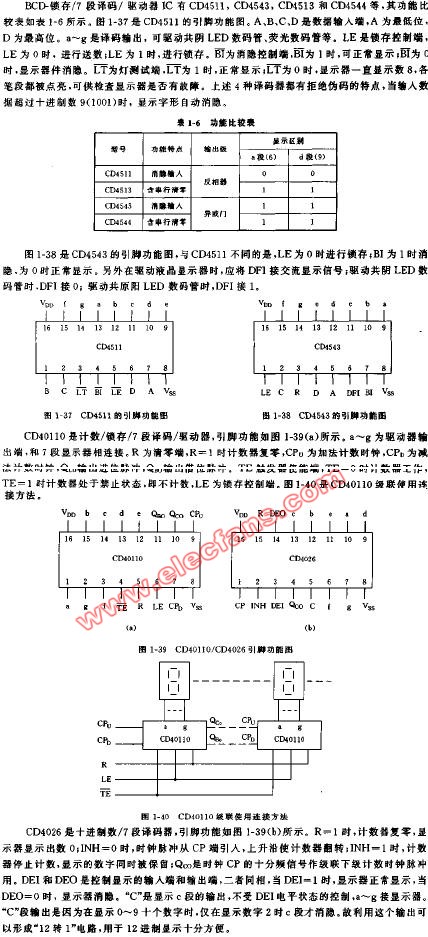

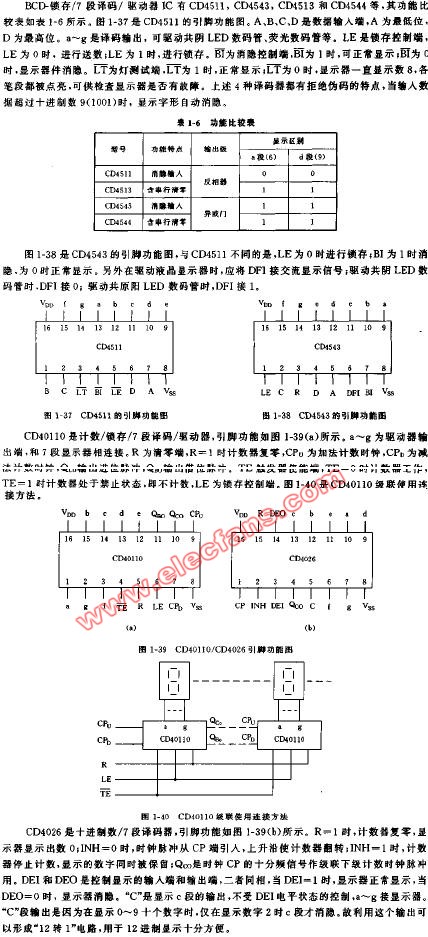

常用的譯碼電路有哪些?本文主要介紹了IO接口地址譯碼電路、BCD譯碼驅動器電路、4線16線譯碼電路、3.8線譯碼器電路以及繼電器譯碼電路。繼電器譯碼電路的作用是在單片機的控制下將1 536個測試點

2018-03-02 15:48:20 37712

37712

本文首先介紹了譯碼器的定義與譯碼器的分類,其次介紹了譯碼器的作用和譯碼器的工作原理,最后介紹了譯碼器的邏輯功能。

2018-02-08 14:04:06 104354

104354

針對無線通信系統中對于高頻率、高吞吐量的要求,提出了一種基于ASIC的高速Viterbi譯碼器實現方案。該譯碼器在約束度小于等于9的情況下,采用全并行結構的加比選模塊。性能分析結果表明,在SMIC

2017-11-11 17:56:15 6

6 為了解決在RS譯碼中存在的譯碼過程復雜、譯碼速度慢和專用譯碼器價格高等問題,以RS(255,239)碼為例,采用了基于改進的無求逆運算的Berlekamp-Massey( BM)迭代算法。結合FP

2017-11-07 15:27:06 15

15 2Mbps視頻數據流的Viterbi算法的移植與優化策略、技巧。 1 Viterbi算法原理簡介 Viterbi譯碼算法是由Viterbi于1967年提出的一種最大似然譯碼方法,譯碼器根據接收序列R按最大似

2017-10-24 11:41:30 0

0 DSP嵌入式系統開發典型案例,第9章 Viterbi譯碼及其實現

2017-10-20 14:23:37 4

4 應用于LTE_OFDM系統的Viterbi譯碼在FPGA中的實現

2016-05-11 11:30:19 11

11 設計、高速數據采集系統設計、常用自動控制系統設計、語音信號處理、編碼系統設計、ip電話系統設計、無線網卡系統設計、viterbi譯碼的實現、非均勻采樣理論及其實現等工程實例。

2015-12-24 14:07:16 22

22 介紹了符合CCSDS標準的RS(255,223)碼譯碼器的硬件實現結構。譯碼器采用8位并行時域譯碼算法,主要包括了修正后的無逆BM迭代譯碼算法,錢搜索算法和Forney算法。采用了三級流水線結構實現

2013-01-25 16:43:46 68

68 文中提出的卷積碼譯碼Matlab仿真方案,旨在用Viterbi譯碼實現對卷積碼譯碼的功能。仿真結果表明,維特比是一種良好的譯碼方式。

2012-03-22 17:21:11 57

57 本文主要對卷積碼編碼和Viterbi譯碼進行MATLAB實現,并在此基礎上分析移位寄存器對糾錯能力的影響。論文首先根據MATLAB的存儲特點及函數特征,主要介紹卷積編碼的原理,同時給出MA

2012-01-13 16:56:57 34

34 該文介紹了兩種Viterbi 譯碼器回溯譯碼算法,通過對這兩種算法硬件實現結構上的優化,給出了這兩種算法的FPGA 實現方法,比較了兩種實現方法的優缺點。最后將其應用在實際的Viter

2011-05-28 15:18:48 33

33 Viterbi譯碼是一種應用廣泛的最大似然估計算法; 而功耗是通信系統設計中的一個重要制約因素,介紹了3種Viterbi譯碼的低功耗設計方法。對這3種設計方法的原理和實際使用效果作了詳

2011-05-16 15:54:11 11

11 Viterbi算法代表了統計概率的模式匹配算法,而DTW算法代表了模版匹配的模式匹配算法,它們之間是否存在關系至今尚無定論

2011-02-22 14:51:23 17

17 Turbo碼雖然具有優異的譯碼性能,但是由于其譯碼復雜度高,譯碼延時大等問題,嚴重制約了Turbo碼在高速通信系統中的應用。因此,如何設計一個簡單有效的譯碼器是目前Turb

2010-11-25 10:10:26 1677

1677

本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FPGA中實現

2010-07-21 17:20:04 22

22 卷積碼/Viterbi譯碼,卷積碼/Viterbi譯碼是什么意思

卷積碼在一個二進制分組碼(n,k)當中,包含k個信息位,碼組長度為n,每個碼組的(

2010-03-18 14:09:21 2193

2193 譯碼器,譯碼器是什么意思

譯碼器是組合邏輯電路的一個重要的器件,其可以分為:變量譯碼和顯示譯碼兩類。 變量譯碼一

2010-03-08 16:32:18 5062

5062 文章分析了Turbo 碼的MAP 類譯碼算法后,針對傳統Log—MAP 譯碼算法的特性,提出了一種改進的Log—MAP 譯碼算法。仿真結果表明,新的算法在降低譯碼復雜度的同時較好地保持了譯

2010-01-15 11:51:47 13

13 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi 譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FP

2010-01-06 15:06:59 12

12 介紹了 TI 的TMS320C6416 DSP 片上Viterbi 譯碼協處理器(VCP)的結構與原理。給出了一種使用鏈式EDMA 結構和“乒乓”緩沖技術提高VCP 譯碼過程并行性的方法。設計出基于MATLAB 的Link for

2009-12-23 15:19:48 19

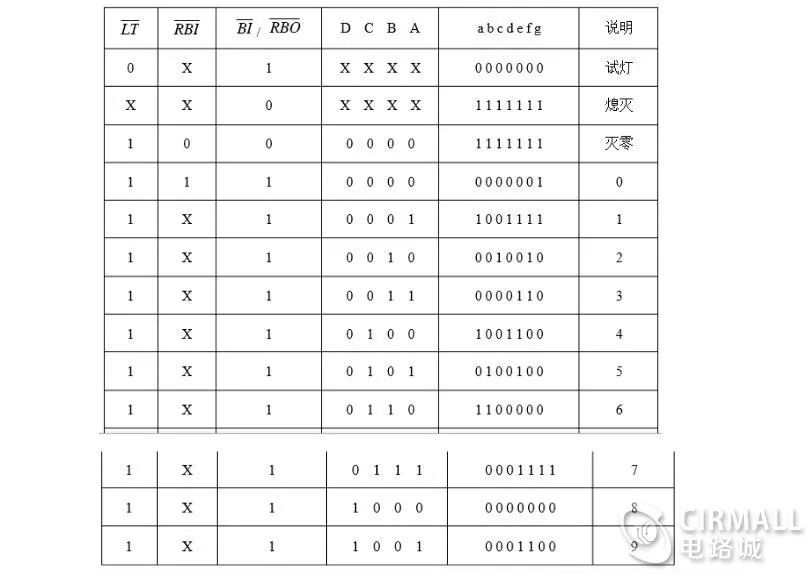

19 計數/譯碼顯示電路: 計數譯碼顯示在現代科學技術中應用非常廣泛,它由計數器、譯碼器和顯示器三部分組成,包含數字電子系統的組合邏輯電路和

2009-12-20 12:36:59 128

128 3G測試系統中的Viterbi譯碼及其DSP實現及優化

摘要 介紹了一種用于測試TD-SCDMA手機終端測試平臺中的關鍵技術——Viterbi譯碼。研究用約束度K=9的卷積編碼和最大似然Viterbi譯

2009-11-13 18:51:25 18

18 給出了由(2,1,N)系列卷積碼Viterbi 譯碼中路徑度量存儲器及其接口的使用FPGA實現時的設計方法,譯碼器采用四個ACS 并行運算的方式,狀態度量的更新采用乒乓模式,闡述了存

2009-09-08 14:49:05 9

9 基于對傳統Viterbi 譯碼器的分析和對改進的Viterbi 算法理論的修正,提出了一種新的Viterbi 譯碼器的實現方法。通過對路徑度量值的深入分析和對回溯信息的重新編碼,在不增加硬

2009-08-13 10:43:19 23

23

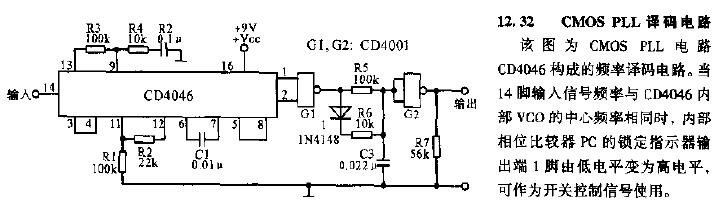

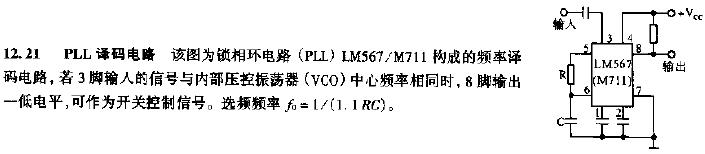

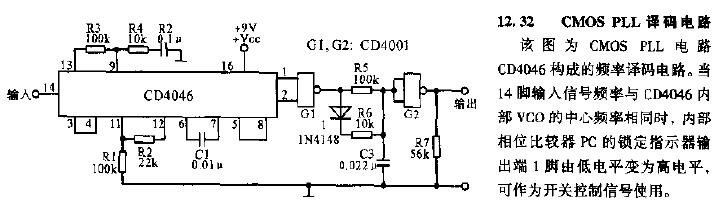

CMOS PLL譯碼電路

2009-04-18 11:07:44 542

542

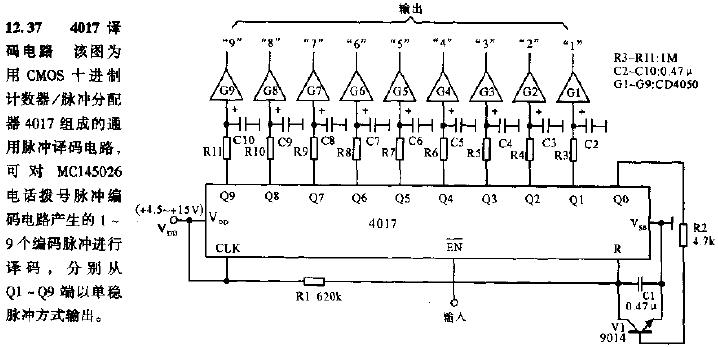

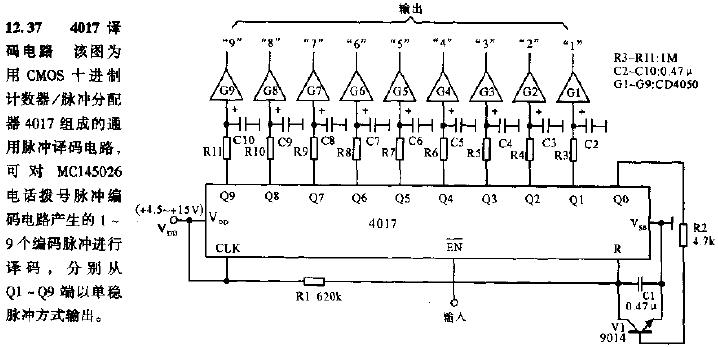

4017譯碼電路

2009-04-18 11:06:35 1248

1248

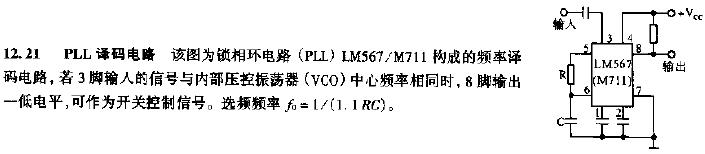

PLL譯碼電路

2009-04-12 13:15:57 496

496

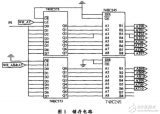

集成電路譯碼器

1.74138集成譯碼器

上圖為常用的集成譯碼器74138,其功

2009-04-07 10:24:17 7830

7830

譯碼器的定義及功能

譯碼是編碼的逆過程,它的功能是將具有特定含義的二進制碼進行辨別,并轉換成控制信號,具有譯碼功能的邏輯電路稱為譯碼器

2009-04-07 10:23:42 15826

15826

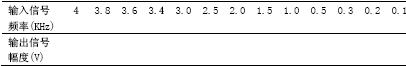

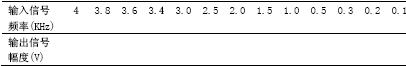

實驗九 PCM編譯碼 一、實驗目的

1. 掌握PCM編譯碼原理。 2. 掌握PCM基帶信號的形成過程

2009-04-01 14:44:49 9420

9420

Altera viterbi compiler v1.0 下載

2009-03-23 09:45:42 31

31 LDPC編譯碼LDPC碼是一種線性分組奇偶校驗碼,它采用基于因子圖的置信傳播(Belief Propagation,BP)迭代譯碼算法進行譯碼。其性能接近Turbo碼,不規則LDPC碼甚至超過Tur

2009-03-01 17:36:05 1696

1696

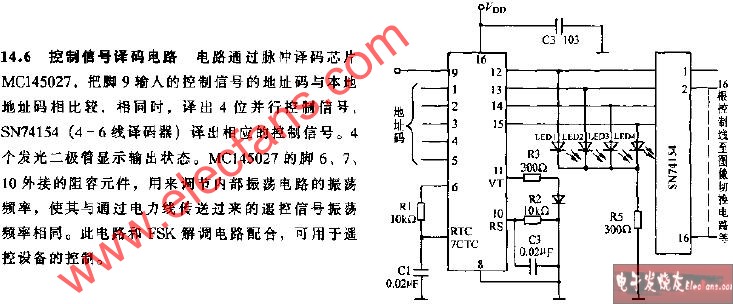

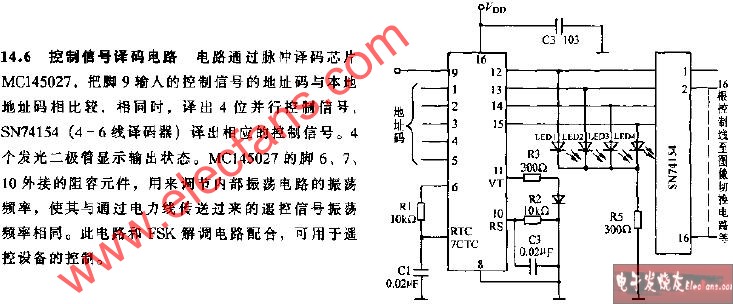

控制信號譯碼電路

2009-02-25 21:54:51 472

472

顯示譯碼器的應用:

2008-12-17 14:35:06 1199

1199

數碼譯碼器的應用:譯碼器課件ppt

2008-12-17 14:31:20 999

999

PCM編譯碼實驗

一、實驗目的1. 掌握PCM編譯碼

2008-10-21 13:35:45 7675

7675

譯碼器

譯碼是編碼的逆過程,即將某個二進制翻譯成電路的某種狀態。實現譯碼操作的電路稱為譯碼器。

2008-09-27 12:59:06 11977

11977

大約束度Viterbi譯碼器中路徑存儲單元的設計

1 引言 Viterbi譯碼算法是一種最大似然譯碼算法,目前廣泛應用于各種數據傳輸系統,特別是衛星

2007-08-15 17:21:47 815

815

Altera viterbi compiler

2006-03-25 15:45:58 18

18 Viterbi Compiler MegaCore Function User Guide

好東西哦。網上搜集,希望對你有用。

2006-03-25 15:40:49 32

32

電子發燒友App

電子發燒友App

評論