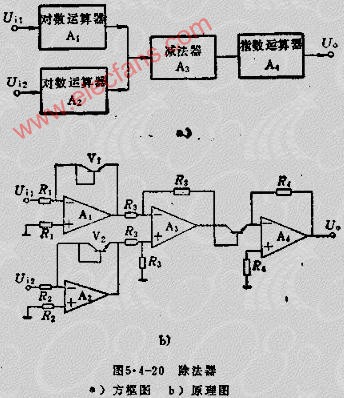

除法器對數運算電路的應用

- 除法器(13808)

相關推薦

運算放大電路的設計實驗

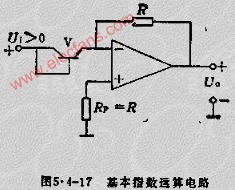

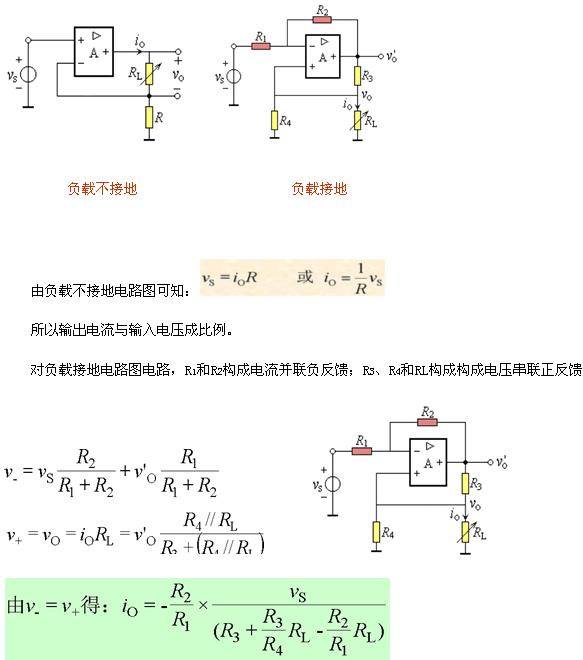

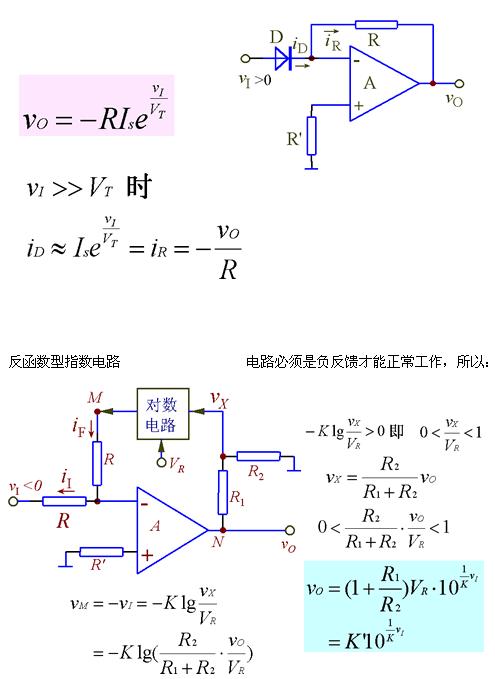

,可以實現乘法、除法、對數等模擬運算功能。如果加入線性或者非線性正反饋網絡(或將正、負兩種反饋形式同時加入),就可以構成一個振蕩器產生各種不同的形態的模擬信號(如正弦波、三角波等)由運算放大器和深度負反饋網絡組成的模擬運算電路如圖1所示。

2008-09-22 13:09:28

AD534KDZ 模擬IC乘法器除法器

AD534是一款單芯片激光調整四象限乘法器除法器,其精度規格以前只有昂貴的混合或模塊化產品才有。無需任何外部調整,AD534L的最大乘法誤差保證為0.25%。出色的電源抑制性能、低溫度系數以及片內

2023-08-09 16:52:53

FPGA基于線性迭代法的除法器設計

FPGA實現除法的方法有幾種,比如直接用/來進行除法運算,調用IP核進行除法運算,但這兩種方式都有個共同的問題——都是黑盒子,在進行時序違例處理時,往往不好操作,比如想打打拍改善下時序都不知從何下手。

2023-07-04 10:03:39 236

236

236

236

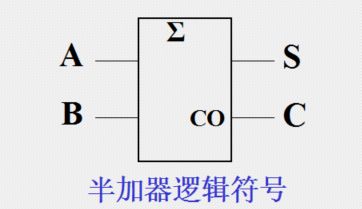

FPGA常用運算模塊-加減法器和乘法器

本文是本系列的第二篇,本文主要介紹FPGA常用運算模塊-加減法器和乘法器,xilinx提供了相關的IP以便于用戶進行開發使用。

2023-05-22 16:13:57 1336

1336

1336

1336

如何使用LM358運算放大器來演示加法器電路

運算放大器(Opamp)有許多有趣的應用,我們已經使用運算放大器創建了許多電路。今天我們將研究運算放大器的另一個應用,即添加兩個或多個輸入電壓,該電路稱為求和放大器或運算放大器加法器。在這里,我們將使用 LM358 運算放大器來演示加法器電路。

2022-11-11 15:29:29 7919

7919

7919

7919

如何實現FPGA中的除法運算

FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且通常無法在一個時鐘周期內完成。因此FPGA實現除法運算并不是一個“/”號可以解決的。

2022-04-27 09:16:03 5168

5168

5168

5168實例九— 除法器設計

4.3 實例九 除法器設計4.3.1. 本章導讀要求掌握除法器原理,并根據原理設計除法器模塊以及設計對應的測試模塊,最后在 Robei可視化仿真軟件經行功能實現和仿真驗證。設計原理這個除法器的設計為

2021-11-07 10:51:04 17

17

17

17乘法器原理_乘法器的作用

乘法、除法、乘方和開方等模擬運算的主要基本單元,而且還廣泛用于電子通信系統作為調制、解調、混頻、鑒相和自動增益控制;另外還可用于濾波、波形形成和頻率控制等場合,因此是一種用途廣泛的功能電路。

2021-02-18 15:08:01 22932

22932

22932

22932

基于FPGA的除法器純邏輯設計案例

除法運算。很多人覺得不就是除法嘛,直接打上/即可,但是,FPGA是不能正確綜合這個除法器的,綜合的結果只是一個固定數值,而不像其他微處理器。可以這么說,用FPGA實現除法運算是比較麻煩的。

2020-06-17 10:17:27 6157

6157

6157

6157

四款常見的除法電路圖分享

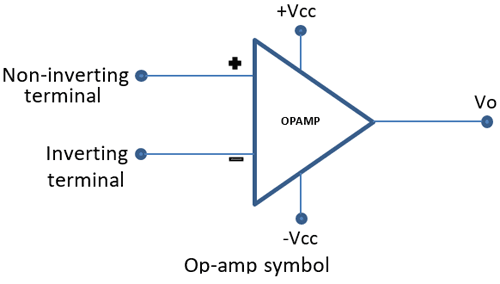

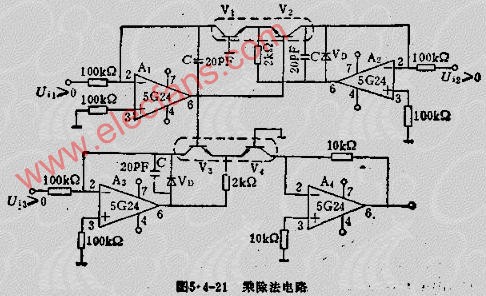

輸入信號為V1、V2,輸出Vo為Vo=10V2/V1。這種除法器是將乘法器接在運算放大器的反院回路組成的。V1的輸入范圍為-0.2V到10V,V2的輸入范圍為-10V到10V。

2019-12-31 14:12:44 15859

15859

15859

15859

用于除法運算的運行時ABI輔助方法過載

SAMC21(一款 Cortex-M0+ MCU)非常適合需要數學計算的應用。SAMC21 MCU 具有可進行乘法運算的快速單周期乘法器選項,還具有一個新的外設,稱為除法和平方根加速器

2018-07-19 09:25:25 5141

5141

5141

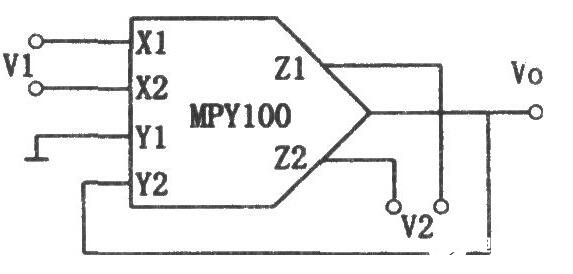

5141微功率乘法器/除法器電路原理

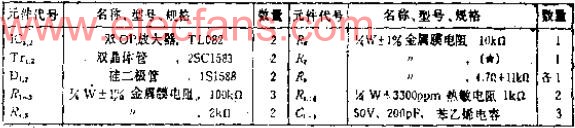

X、Y 和 Z 輸入放大器執行伺服操作,以根據施加的信號來控制晶體管的發射極電流。晶體管 Vbe 隨電流呈對數變化,因此 Q2 的發射極包括 X 和 Y 對數之和。Z信號對數在 Q4 的基極上提供,于是 Q4 上最終的 Vbe 為 Vbe1 + Vbe2 - Vbe3。

2018-07-05 10:07:00 3082

3082

3082

3082

一文讀懂FPGA中的除法運算及初識AXI總線

FPGA中的硬件邏輯與軟件程序的區別,相信大家在做除法運算時會有深入體會。若其中一個操作數為常數,可通過簡單的移位與求和操作代替,但用硬件邏輯完成兩變量間除法運算會占用較多的資源,電路結構復雜,且

2018-05-18 01:15:00 3961

3961

3961

3961基于delta碼的乘除法運算錯誤檢測改進算法

為確保安全苛求系統中程序執行的正確性,研究人員將差錯控制理論用于對計算機指令進行編碼,但由于編碼大多涉及模運算,導致復雜度大量增加,應用于實時系統有困難。針對復雜度問題對delta碼的乘除法運算

2017-12-04 16:44:29 0

0

0

0信號的運算與處理電路--求和運算電路

運算電路是集成運算放大器的基本應用電路,它是集成運放的線性應用。討論的是模擬信號的加法、減法積分和微分、對數和反對數(指數)、以及乘法和除法運算。

2017-11-27 15:55:10 5

5

5

5進位保留Barrett模乘法器設計

乘法器,求模運算部分利用Barrett約減運算,用硬件描述語言進行FPGA設計與實現,避免了除法運算。對于192位的操作數,完成Barrett模乘需要約186個時鐘周期,計算速率可以達到269.17 Mb/s。

2017-11-08 15:18:19 32

32

32

32高效的C編程之除法運算

14.2 除法運算 因為ARM體系結構本身并不包含除法運算硬件,所以在ARM上實現除法是十分耗時的。ARM指令集中沒有直接提供除法匯編指令,當代碼中出現除法運算時,ARM編譯器會調用C庫函數(有符合

2017-10-17 17:22:29 5

5

5

5一種模擬除法器的設計及仿真驗證CMOS工藝

模擬除法器是一種能實現兩個模擬量相除的電子器件。目前不僅應用于模擬運算方面,而且已擴展到無線通訊、電視廣播、人工神經網路、機器人控制技術等領域。此外,模擬除法器在模糊控制和測量儀表中也是非常重要的器件。

2014-09-19 15:14:31 2946

2946

2946

2946FPU加法器的設計與實現

浮點運算器的核心運算部件是浮點加法器,它是實現浮點指令各種運算的基礎,其設計優化對于提高浮點運算的速度和精度相當關鍵。文章從浮點加法器算法和電路實現的角度給出設計

2012-07-06 15:05:42 47

47

47

47基于Verilog計算精度可調的整數除法器的設計

除法器是電子技術領域的基礎模塊,在電子電路設計中得到廣泛應用。目前,實現除法器的方法有硬件實現和軟件實現兩種方法。硬件實現的方法主要是以硬件的消耗為代價,從而有實

2012-05-24 09:41:04 1757

1757

1757

1757

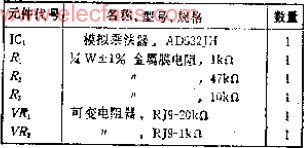

AD532,pdf (預調整的單芯片乘法器/除法器)

AD532是首款預調整的單芯片乘法器/除法器;無需任何外部調整電阻或輸出運算放大器,即可保證±1.0%的最大乘法誤差和±10 V的輸出電壓范圍。AD532經過內部調整,易于使用,為設計

2010-10-02 09:37:50 131

131

131

131乘除法和開方運算的FPGA串行實現

高精度的乘除法和開方等數學運算在FPGA實現中往往要消耗大量專用乘法器和邏輯資源。在資源敏感而計算時延要求較低的應用中,以處理時間換取資源的串行運算方法具有廣泛的應

2010-07-28 18:05:14 37

37

37

37乘法器對數運算電路應用

乘法器對數運算電路應用

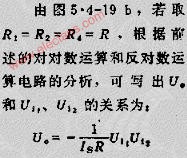

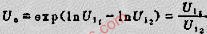

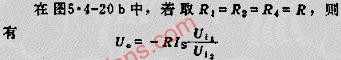

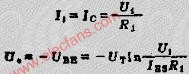

由對數電路實現乘法運算的數學原理是:UO=EXP(INU11+INU12)=U11+U12

圖5.4-19示出了滿足上式的乘法器的方框

2010-04-24 16:03:19 2115

2115

2115

2115

對數運算電路

對數運算電路

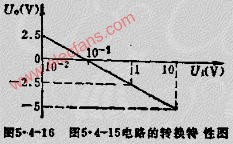

圖5.4-15是具有溫度補償和失調的對數運算電路,輸入電壓10MV~10V,動態范圍60DB。V1和V2應當用特性一致結溫相同的對管,為了提高精度,V1和V2應

2010-04-23 17:31:43 6561

6561

6561

6561

原碼除法運算原理是什么?

原碼除法運算原理是什么? 兩個原碼表示的數相除時,商的符號由兩數的符號按位相加求得,商的數值部分由兩數的數值部分相除求得。 設有n位定

2010-04-13 11:15:45 11412

11412

11412

11412并行除法器 ,并行除法器結構原理是什么?

并行除法器 ,并行除法器結構原理是什么?

1.可控加法/減法(CAS)單元 和陣列乘法器非常相似,陣列式除法器也是一種并行運算部件,采用大規模集成

2010-04-13 10:46:30 14405

14405

14405

14405模擬信號運算電路基礎

模擬信號運算電路基礎

7.1 理想運放的概念7.2 比例運算電路7.3 求和電路7.4 積分和微分電路7.5 對數和指數電路7.6 乘法和除法電路

2010-04-13 08:54:20 62

62

62

62TI發布可定制編程的3-PLL時鐘合成器乘法器除法器

TI推出的CDC706是目前市場上體積最小且功能強大的PLL合成器/乘法器/除法器之一。盡管其物理外形非常小巧,但卻極為靈活。該器件能夠在特定輸入頻率下生成幾乎獨立的輸出頻率。

2009-11-26 14:35:47 21

21

21

21 電子發燒友App

電子發燒友App

評論