摘要

在SoC設計中,EDA工具處理完網絡列表之后插入的邏輯均被稱作ECO。可以不必進行合成、地點和路線、提取、串音等整個SoC設計周期,從而節省完成ECO的時間。可以采用省錢方式來執行后掩膜工程變更清單。 如果只修改少量金屬層就能完成一項更改,那么涉及的成本要比將整個設計完全重做少得多。 ECO通常會使用到備用門模塊(在合成期插入)。通常,這些備用門模塊包括NAND、NOR、 觸發器、 緩沖器、逆變器以及其他可能使用到的邏輯單元。 本文重點介紹如何使用現有布局的緩沖器/逆變器(對)邏輯,使用備用單元模組來避免違反設計(DRV)規則。

介紹

實施工程變更訂單(ECO),是片上系統(SoC)設計階段十分常用的一個步驟。 在設計中采用ECO的原因有很多。

1.事先規劃好的ECO: 有時候,設計人員可以預先設定好采用ECO。 例如,有時候可能有這種情況:在ASIC設計周期的后期需要引入IP,因此設計人員要對其活動進行適當規劃,以免設計階段受到限制。 但有說法認為在設計周期中采用ECO,大部分屬于偶然。

2.功能性修改: ECO也可能是設計規范需要進行功能性修改的結果,如果客戶需要附加功能或者應用軟件要求硬件部署該功能,那就有可能需要進行此類修改了。

3.設計問題: 門級模擬(GLS)或類似技術中一些先前的測試芯片的硅結果中可能會出現設計問題。

要在邏輯門里實施ECO,設計人員需要一個最佳解決方案,因為增加額外的門可能導致要再制造基礎層(如激活層、多晶硅層、氮化物層)掩膜,這比互連掩膜的成本高得多。 因此理想的情況是,設計人員會希望只包含使用現有邏輯的邏輯,來減少因再制造產生的成本。

問題陳述:

使用額外的邏輯門來包含ECO,可能會對整個時序及設計的可路由性產生影響,具體來說,當ECO邏輯相當大時,受到影響的模塊實施密度將達到100%。

現行方法:

當前針對該問題所采取的解決方法是在設計的物理合成階段,在每個模塊內添加額外的門,因此在執行ECO時,現有的備用門在以后可以用來包含設計中的修改。這樣就不必增加更多的邏輯。 但這種方法具有一定的局限性。

現行方法的局限:

1.設計人員不能預測一個模塊的最佳備用門數量,以避免ECO的中途中止; 例如,假設功能性ECO需要在一個鏈里連接10個緩沖器。 但現有的備用單元模組只有6個緩沖器,由于沒有緩沖器/逆變器(對)所以我們必須重新轉動SoC。基本上,這個局限在于設計人員必須要在一個模塊中放置更多冗余邏輯,或在另一個模塊中備用放置有限的備用門。

2. 規模過大的ECO必然會違反保持時間并違反設計規則,例如違反邏輯門的最大過渡或最大驅動強度。 這需要額外的冗余緩沖器來解決保持時間違反問題,或提高DRV易發生的信號壓擺率性能。

建議的解決方案:

本文欲介紹一款我們可以使用現有布局來省去緩沖器/逆變器(對)的解決方案。

請記住,在備用規模塊中,可能必須增加冗余的NAND/NOR門和額外的觸發器/閂鎖,但不一定需要增加冗余的緩沖器和逆變器。

基本上,本文試圖演示一種創新方法,它使用優化技術,可從現有布局恢復緩沖器/逆變器邏輯。

算法和偽代碼

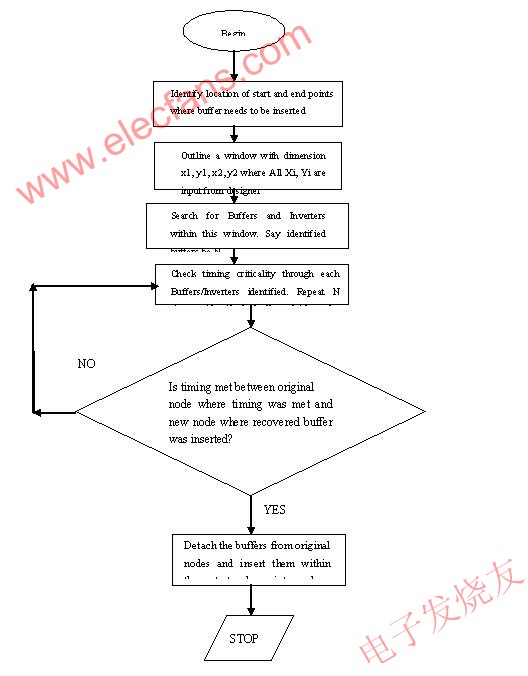

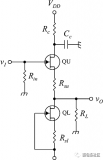

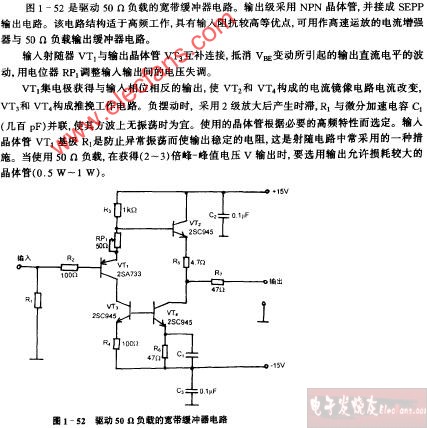

圖1: 一個(x1,y1,x2,y2)窗口大小所要實施的基本算法

生成窗口大小的偽代碼:

開頭

x=x1;y=y1;

當 x < x2,

y < y2時

x’ = x + a, y’ = y + b;

x=x’,y=y’

如果 x > x2 或 y > y2

x=x2, y="y2";

結束

生成的每個窗口坐標用 (x, y, x’, y’)表示

此處a、b需要根據具體的設計和技術而定。 如果SoC的SoG(Sea of Gates)區域是 7 mm2 或更大,設計人員在計算窗口大小時需要注意計算的復雜性。

描述:

如上面的流程圖所示,該思路的核心是如何識別非關鍵性的緩沖器(w.r.t時序余量)。 在實施ECO時,我們不可避免地需要使用備用單元模組的緩沖器。 現在,這個緩沖器的放置是比較隨意的,使用它會違反DRV規則。

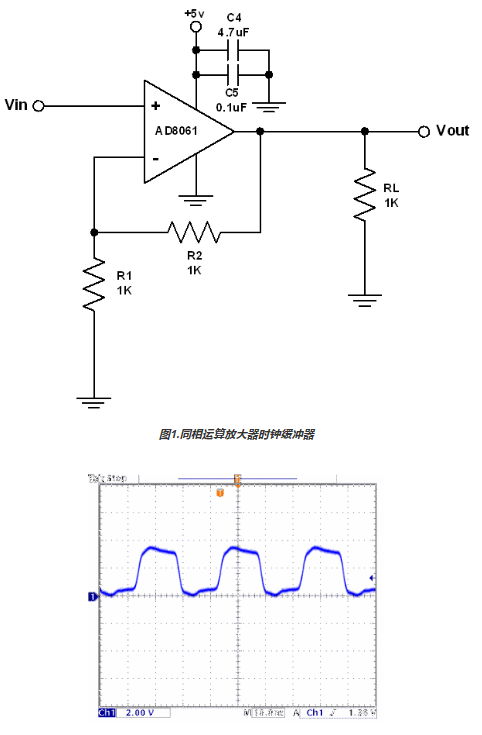

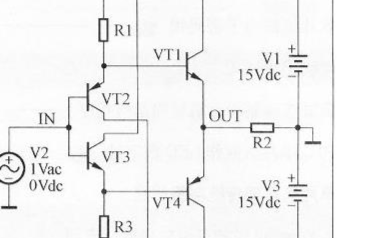

例如,我們假設使用BUFX8來驅動5個扇出。總的容量負荷(包括線路和引腳)是200fF。現在根據該緩沖器的SPICE特征,任何高于150fF的負荷都會導致不好的輸出壓擺。差的輸出壓擺不僅會違反最大過渡值,而且還會影響扇出驅動電路的時序。

因此,在這種情況下,明智的做法是遵從上面的算法,這樣我們可以進行以下步驟:

1.找出ECO的目標點: 我們應當找出開始點和結束點位置,這是放置緩沖器元件的位置。該位置決定著窗口大小,我們應當在這個窗口里搜索非關鍵性緩沖器/逆變器(對)。

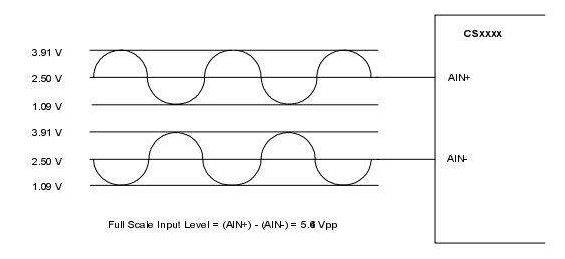

2.決定窗口大小: 這完全由設計人員決定。 他可以根據技術選擇窗口大小。如果緩沖器能驅動的最大負荷是200fF,那么窗口大小應當相應地進行修改。

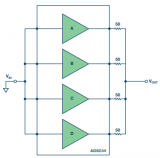

3.緩沖器/逆變器(對)的識別: 現在,該算法將在特定窗口上運行,并且嘗試識別已標記位置中出現的所有緩沖器/逆變器(對)。

4.計算時序余量: 一旦緩沖器/逆變器(對)做了標記,算法應嘗試通過這些標準單元找出時序余量。如果這些標準單元對時序很關鍵,那么該緩沖器/逆變器(對)就不需要標記。只要該緩沖器/逆變器(對)保留為標記狀態,那么取消哪一個都不會對該設計的現有時序情況產生影響。

5.最后一步: 現在,帶標記的緩沖器/逆變器(對)可以用于ECO。

結論

布局優化和冗余單元的使用可以幫助設計人員在以后數百萬個門SOC的設計階段,消化復雜的ECO,同時避免對整個產品的上市時間造成影響。

電子發燒友App

電子發燒友App

評論