ASIC的復(fù)雜性不斷提高,同時工藝在不斷地改進(jìn),如何在較短的時間內(nèi)開發(fā)一個穩(wěn)定的可重用的ASIC芯片的設(shè)計(jì),并且一次性流片成功,這需要一個成熟的ASIC的設(shè)計(jì)方法和開發(fā)流程。本文結(jié)合NCverilog,DesignCompile,Astro等ASIC設(shè)計(jì)所用到的EDA軟件,從工藝獨(dú)立性、系統(tǒng)的穩(wěn)定性、復(fù)雜性的角度對比各種ASIC的設(shè)計(jì)方法,介紹了在編碼設(shè)計(jì)、綜合設(shè)計(jì)、靜態(tài)時序分析和時序仿真等階段經(jīng)常忽視的問題以及避免的辦法,從而使得整個設(shè)計(jì)具有可控性。

1基本的ASIC設(shè)計(jì)流程

ASIC設(shè)計(jì)流程可以粗分為前端設(shè)計(jì)和后端設(shè)計(jì),如果需要更細(xì)的劃分,可以分成如下幾個步驟:

1.包括系統(tǒng)結(jié)構(gòu)分析設(shè)計(jì)、RTL編碼以及功能驗(yàn)證;

2.邏輯綜合、PreLayoutSTA以及形式驗(yàn)證(RTL代碼與邏輯綜合生成的Netlist之間);

3.Floorplan、Placement、ClockTree插入以及全局布線(GlobalRouting)

4.形式驗(yàn)證(邏輯綜合的Netlist與帶有CT信息的Netlist之間)、STA;

6.PostlayoutSTA,帶有反標(biāo)延遲信息的門級仿真;

7.Tape-Out

當(dāng)然,這還是一個比較粗的流程,其中每個步驟還可以分得更細(xì),通常所說的前端設(shè)計(jì)主要包括上述流程中的1,2,4,6這幾個部分。同時,這個流程是一個迭代的過程。對于一些通常的問題以及其中的一些方法,已經(jīng)有大量的文獻(xiàn)中提到,本文將不再贅述,因此本文著力于討論在設(shè)計(jì)各個階段中一些容易被忽視的或者可能帶來潛在危險的地方。

2結(jié)構(gòu)分析設(shè)計(jì)、RTL編碼

這一階段在整個ASIC設(shè)計(jì)中占非常重要的地位,結(jié)構(gòu)分析設(shè)計(jì)階段主要是從產(chǎn)品的功能定義出發(fā),對產(chǎn)品采用的工藝、功耗、面積、性能以及代價進(jìn)行初步的評估,從而制定相應(yīng)的設(shè)計(jì)規(guī)劃,對于規(guī)模很大的ASIC設(shè)計(jì),在這一階段估算芯片的功耗面積非常困難。

在這里引入一個ASIC設(shè)計(jì)中很重要的概念:劃分(Partitioning),在不同的設(shè)計(jì)階段這個概念都將提到。首先,必須在芯片的Top-1級進(jìn)行功能劃分,Top-1級通常可以分為4個大的功能模塊,IOPads、邊界掃描邏輯、核心功能邏輯,以及PLL時鐘模塊,然后再對核心功能邏輯依據(jù)功能進(jìn)一步細(xì)化。核心功能部分將是RTL編碼設(shè)計(jì)的重點(diǎn)部分,下面就這一部分展開說明。

2.1良好的編碼風(fēng)格

編碼風(fēng)格對芯片的正確性、可讀性、可維護(hù)性以及綜合后芯片的性能、面積都有很大的影響。自然,對于編碼中遇到的所有問題一一闡述不是一篇論文所能做到的,下面只對一些經(jīng)常遇到的可能產(chǎn)生錯誤的地方進(jìn)行重點(diǎn)說明。

無論從可重用設(shè)計(jì)的角度還是代碼仿真行為與實(shí)際芯片的行為一致性的角度來說,采用工藝獨(dú)立的設(shè)計(jì)是必要的,一些工程師在編碼時可能用到一些延遲單元或者延遲線,來生成一個脈沖來操作,由于延遲單元對溫度、電壓以及制造工藝敏感,這些因素的改變也會改變生成的脈沖的寬度,因此,可能在仿真的時候沒有問題,或者在某些操作條件下沒有問題,而實(shí)際芯片工作時或者工作條件改變時芯片就沒有按照設(shè)計(jì)目標(biāo)工作了。

在RTL級編碼時應(yīng)該盡量避免采用例化標(biāo)準(zhǔn)單元門的方式編碼,這不僅降低代碼的可讀性,當(dāng)采用新的單元庫或者新的工藝時,這些代碼就需要反復(fù)的修改,綜合工具也不會對這些代碼進(jìn)行邏輯優(yōu)化。

其他問題如:由于沒有對所有的條件分支賦值引起潛在的Latch問題、always塊中的敏感列表問題,以及阻塞賦值與非阻塞賦值的選擇問題很多文獻(xiàn)中都提到,就不再贅述。下面提到一個容易被忽視的問題,在定義時序塊時,有些信號是需要復(fù)位的,有些不需要復(fù)位,如果編碼時把它們寫在一個always塊中,綜合出來的電路就不是我們設(shè)想的。對于那些不需要復(fù)位的信號,綜合后可能把復(fù)位信號連到對應(yīng)的觸發(fā)器使能端,這樣導(dǎo)致RTL代碼和Netlist的行為不一致,而這類問題在形式驗(yàn)證時也沒法發(fā)現(xiàn),需要通過大量的門級仿真才可能發(fā)現(xiàn)。

ASIC設(shè)計(jì)應(yīng)該盡量避免采用Latch作為時序單元,Latch設(shè)計(jì)潛在的問題,如:如果使能輸入端有Glitch,就會導(dǎo)致鎖存噪聲數(shù)據(jù)。或者你能夠保證數(shù)據(jù)穩(wěn)定時間可以包住使能信號,可你很難保證在使能關(guān)閉的瞬間D輸入端沒有Glitch,尤其在接收總線數(shù)據(jù)的時候。同時,Latch設(shè)計(jì)還帶來STA和DFT的困難,而采用觸發(fā)器的設(shè)計(jì),通過Setup/Hold時間的檢查報出這些問題。因此,盡管Latch設(shè)計(jì)有面積、低功耗等方面的優(yōu)勢,由于這些潛在的風(fēng)險使得設(shè)計(jì)變得不可控,因此不推薦使用。

盡量避免把時鐘當(dāng)作信號使用,在RTL驗(yàn)證時不會出現(xiàn)什么問題,但是,如果在后端設(shè)計(jì)的時候忽略了對這些點(diǎn)的時鐘skew控制,就會產(chǎn)生意想不到的結(jié)果。例如:

例1:

這個代碼在RTL級仿真時是不會有任何問題的,其中潛在的問題留待后面討論。

2.2同步設(shè)計(jì)和跨時鐘域數(shù)據(jù)傳輸

盡管異步系統(tǒng)有很多優(yōu)勢,如低功耗,也沒有同步系統(tǒng)中讓工程師頭疼的時鐘分布以及skew問題,但是其復(fù)雜的各種握手協(xié)議,以及異步電路在測試上的困難,使得同步系統(tǒng)還是數(shù)字電路設(shè)計(jì)的首選。同步設(shè)計(jì)的一個特點(diǎn)就是所有的時序單元都是對統(tǒng)一的時鐘邊沿敏感。要使整個芯片只采用一個時鐘并不現(xiàn)實(shí),因此,異步時鐘域之間的數(shù)據(jù)傳輸以及其中的一些問題將是本節(jié)討論的重點(diǎn)。

通常,為了能夠更好的綜合和STA,需要對設(shè)計(jì)進(jìn)行劃分,一般的原則是將異步時鐘域之間有數(shù)據(jù)交換的部分獨(dú)立出來單獨(dú)處理,其他的模塊都在單一的同步時鐘域中工作。對于這些模塊如何在綜合過程中特殊處理在下面的章節(jié)中討論,本節(jié)主要討論在代碼設(shè)計(jì)中需要考慮的問題。

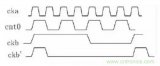

異步時鐘之間的亞穩(wěn)態(tài)(Metastability)問題,亞穩(wěn)態(tài)主要是由于被采樣數(shù)據(jù)的變化十分靠近采樣時鐘的邊沿引起的,這樣接收(采樣)觸發(fā)器的輸出就是亞穩(wěn)態(tài),并在傳輸過程中發(fā)散而引發(fā)邏輯錯誤,也就是通常所說的同步失敗。在同步時鐘域中的這種問題是Hold問題,可以通過EDA工具或插入buffer消除,因?yàn)镋DA工具可以檢測到這種問題。那么在異步接收設(shè)計(jì)中通過兩級Flipflop來消除這種可能出現(xiàn)的亞穩(wěn)態(tài)。現(xiàn)在也有工具檢測代碼中可能出現(xiàn)的亞穩(wěn)態(tài)問題。多位接收控制信號之間的skew引起的問題如圖1,如果其中一位如C2延遲大于C1,Ck采樣的數(shù)據(jù)就變成了C2=1,C1=0,如果按照無skew傳輸?shù)牟ㄐ问荂2’的樣子,應(yīng)該是00才對。而skew是不可避免的,可能是由于C2C1信號的Launch時鐘本身的skew引起,也可能是傳輸延遲引起。對于簡單的情況,我們可以通過簡化邏輯,盡量讓控制信號是1位寬。而這樣的問題同樣出現(xiàn)在多位寬的數(shù)據(jù)接收情況。這時通常推薦使用異步FIFO接收,或者通過握手協(xié)議接收。有的系統(tǒng)設(shè)計(jì)數(shù)據(jù)交換協(xié)議約定,異步接收過程中,當(dāng)某個事件發(fā)生后(如圖1中采樣到V信號為1后)的1個Cycle后(也可以約定多個Cycle)數(shù)據(jù)肯定是正確的;也可以消除這種skew問題,但是,這種實(shí)現(xiàn)需要后端設(shè)計(jì)時保證這些相關(guān)信號的skew不會超過約定的周期,同時發(fā)送方的數(shù)據(jù)也要保持足夠的周期數(shù)。如圖1中C2”信號,如果skew2>Period(一個CKCycle),則收到V信號一個Cycle后采樣數(shù)據(jù)還是錯誤的。

2.3復(fù)位策略

復(fù)位信號中最主要的問題是Removal,也就是要保證所有的觸發(fā)器必須在同一節(jié)拍內(nèi)離開Reset狀態(tài),另外,Reset信號完成的時刻不能與時鐘邊沿太靠近,以防止觸發(fā)器進(jìn)入亞穩(wěn)態(tài)(Metastability)。同步復(fù)位和異步復(fù)位各有利弊,很難說哪種更有優(yōu)勢。除了在編碼風(fēng)格時講到的一個問題,在這里再對兩種策略中可能出現(xiàn)的問題進(jìn)行分析說明。

同步復(fù)位有一個好處就是復(fù)位的時刻發(fā)生在時鐘的邊沿,這樣可以防止復(fù)位信號的Glitch。如果是內(nèi)部生產(chǎn)的Reset信號,就必須保證Reset脈沖有足夠的寬,至少2個Cycles,能夠讓時鐘采樣到。同時,這也是它的缺點(diǎn),因?yàn)樗枰粋€活動的時鐘,在加電時無法對一些電路產(chǎn)生復(fù)位。另外,綜合可能把同步復(fù)位的邏輯移到觸發(fā)器的D輸入端,作為普通的信號處理,由于Reset信號通常有傳輸負(fù)載和延遲,這樣處理會導(dǎo)致DataPath上較長的延遲。

異步復(fù)位的最大好處就是不需要活動的時鐘,對于一些需要加電復(fù)位的電路,如總線,是很必要的;同時,不像同步復(fù)位那樣,復(fù)位信號會被用作D端的輸入邏輯,使得整個DataPath非常干凈。如果異步復(fù)位有Glitch可能使芯片進(jìn)入復(fù)位狀態(tài),這時可以通過兩級DFF接收Reset,再通過tree給復(fù)位觸發(fā)器使用,這樣可以消除輸入引起的Glitch,如果設(shè)計(jì)中有多個時鐘域,可以對每個時鐘分配兩個DFF接收Reset信號。

2.4門控時鐘

GatedClock主要的優(yōu)點(diǎn)在于能夠降低功耗面積,也可以簡化邏輯從而提高頻率。在編碼時需要考慮無Glitch的門控信號設(shè)計(jì)。同時,在DFT設(shè)計(jì)時,由于觸發(fā)器的時鐘是前一級邏輯的輸出(其他派生時鐘也有同樣的問題),為了測試這類觸發(fā)器,需要為時鐘增加一級Mux,在正常工作模式下,采用派生時鐘,在掃描測試時采用正常的時鐘。門控時鐘的主要問題出現(xiàn)在綜合、CTS插入以及STA分析的時候,在后面將進(jìn)行特別的分析討論。

2.5總線實(shí)現(xiàn)

在這里只討論總線實(shí)現(xiàn)的方式,不涉及總線的協(xié)議。在設(shè)計(jì)總線時將面臨著兩種基本方式的選擇,是采用三態(tài)總線還是采用多路選擇結(jié)構(gòu)的總線。在全定制設(shè)計(jì)時,設(shè)計(jì)者似乎更喜歡采用三態(tài),掛在總線上的各個部件可以分布在芯片的各個部分。同時,由于可以減少連線的數(shù)量,它必須保證在任何時候,不發(fā)生總線沖突,如果多個驅(qū)動總線可能導(dǎo)致嚴(yán)重的錯誤,需要通過一些措施消除這種隱患,比如三態(tài)的使能通過解碼器產(chǎn)生Onehot的編碼,防止多驅(qū)動引起的邏輯錯誤和對芯片的損害;同時,三態(tài)總線需要連到上拉電阻上,以防止在一段時間內(nèi)不驅(qū)動總線產(chǎn)生總線數(shù)據(jù)不確定,而DC等綜合并不支持。另外,三態(tài)總線的電容負(fù)載也是一個不可忽視的問題,對性能和面積造成不利的影響,其負(fù)載主要來自總線連接的多個電路單元,總線布局本身帶來一定的負(fù)載;最后,三態(tài)總線給DFT設(shè)計(jì)也帶來困難。基于這些理由,在非定制ASIC設(shè)計(jì)時,我們實(shí)在不必要選擇三態(tài)總線的方式。相比之下,采用多路選擇器的問題是較多連線帶來的布線擁塞問題,選擇器的延遲問題基本上不是什么問題,深亞微米設(shè)計(jì)中,門的延遲差別已經(jīng)變少,同時多層金屬也帶來了足夠的布線資源。

3邏輯綜合以及后端設(shè)計(jì)相關(guān)問題

3.1編碼風(fēng)格檢查

DC對編碼風(fēng)格的檢查提供良好的支持,在進(jìn)行邏輯綜合之前最好先分析一下DC的log文件,看是否有上述的或其他的一些編碼風(fēng)格問題。通過set_dont_use命令可以禁止使用一些工藝相關(guān)的單元,all_registers帶參數(shù)也可以報告出設(shè)計(jì)中所用到的Latch。下面主要討論前面提到的一些情況在綜合以及后端實(shí)現(xiàn)時的特殊處理。同時,還有很多EDA工具提供編碼風(fēng)格進(jìn)行檢查。

3.2異步時鐘域

在編碼設(shè)計(jì)中我們通過劃分,將異步時鐘域接收模塊分離成獨(dú)立的模塊,其他模塊都采用單獨(dú)的時鐘,綜合約束相對簡單。對于那些帶有異步時鐘域的模塊,如果不進(jìn)行約束,DC總是試圖去滿足采樣時鐘的setup/hold時間,事實(shí)上,設(shè)計(jì)者并不關(guān)心異步時鐘域之間的這些問題,而其Metastability問題在編碼階段已經(jīng)解決。通常,可以設(shè)置異步時鐘域之間的Path為false_path。如:

set_false_path-from[get_clocksCLKB]-to[get_clocksCLKA]

如果異步接口數(shù)據(jù)的控制按照最后一種方式

(也就是在約定的節(jié)拍內(nèi)讀取數(shù)據(jù)),也就需要發(fā)送方的數(shù)據(jù)skew控制在一定范圍內(nèi)。由于沒有對這些路徑進(jìn)行約束(雖然可以設(shè)置這些path的Maxdelay,但是這種約束對于skew的控制并不能取得好的效果),工具無法對這些路徑進(jìn)行自動優(yōu)化。因此最好采用手工布局的方法,讓這些skew在一個可控的范圍內(nèi),在STA階段,也需要對這些skew進(jìn)行單獨(dú)的分析。

3.3特殊時鐘信號處理

門控時鐘像所有的內(nèi)部時鐘一樣,時鐘的skew可能引起一些保持時間問題,默認(rèn)條件下,時鐘樹綜合工具并不把邏輯門相連的時鐘信號連到時鐘樹上,非門控的觸發(fā)器上的時鐘是連在時鐘樹上,這個時鐘延遲是相當(dāng)可觀的,為了控制門控時鐘與非門控時鐘的skew,通常從時鐘樹葉子節(jié)點(diǎn)的上一級引出時鐘信號作為控制門的時鐘輸入。在STA階段需要對門控時鐘的Setup/Hold時間進(jìn)行特殊分析,以及Glitch檢查。然后,我們再回顧一下例1的代碼中的情況,可以用圖2的示意圖表示。

電子發(fā)燒友App

電子發(fā)燒友App

評論