通過本文可以了解時鐘信號的數字定時以及諸如抖動、漂移、上升時間、下降時間、穩定時間、遲滯和眼圖等常用術語。 本教程是儀器基礎教程系列的一部分。

1. 時鐘信號

?

發送數字信號其實發送的就是一串由0或1組成的數字序列。 然而,與不同設備進行通信時,定時信息要與發送的位相關聯。 數字波形作為時鐘信號的參考。 您可以將時鐘信號看成是一個指揮者,它為數字電路系統的各個部分提供定時信號,使每個過程都可在精確的時間點觸發。

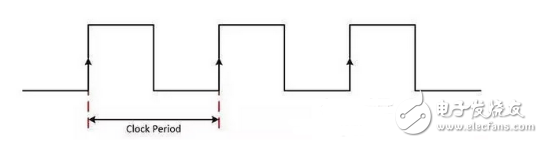

時鐘信號是具有固定周期的方波。 周期是指一個時鐘邊沿到下一個同類時鐘邊沿之間的時間間隔,最常用的方式是一個上升沿到下一個上升沿之間的時間間隔。 時鐘的頻率等于時鐘周期的倒數。

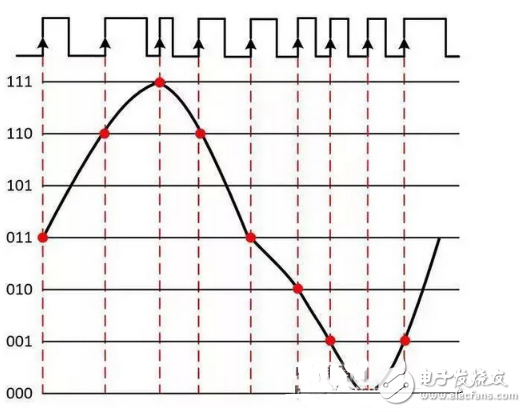

圖1. 數字波形作為時鐘信號的參考,時鐘信號具有固定周期,在數據傳輸過程中用固定的時間間隔來同步數字信號發射器和接收器。

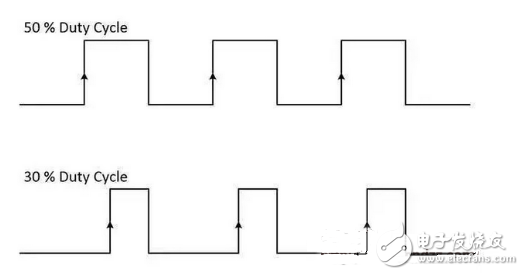

時鐘信號的占空比是波形處于所占的時間比。 圖2展示了兩個具有不同占空比的波形的區別 您可以發現占空比為30%的波形處于的時間少于占空比為50%的波形。

圖2.信號的占空比是指波形處于的時間百分比。

時鐘信號用于在數據傳輸過程中同步數字信號發射器和接收器。 比如,發射器可以在時鐘信號的每個上升沿發送一個數據位,接收器可使用相同的時鐘讀取數據。 在這種情況下,設備的確定邊沿是上升沿(從低電平到高電平)。 對于其他設備則可能是下降沿(從高電平到低電平)。 時鐘的確定邊沿又稱為有效時鐘邊沿。 數字信號發射器在每個有效時鐘邊沿觸發新的數據發送,而接收器則在每個有效時鐘邊沿上進行采樣。 后來的設備開始同時使用時鐘的上升驗和下降沿;這種設備被稱為雙倍數據速率傳輸(DDR)設備。 事實上,數據傳輸對于有效邊沿有短暫的短延;這種延時稱為時鐘到輸出時間。

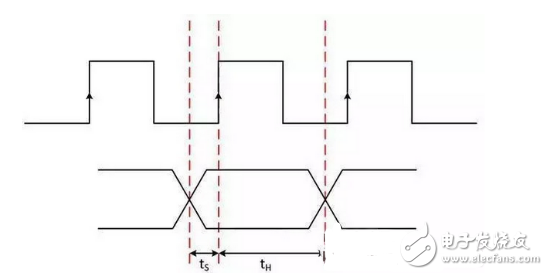

當接收器依據采集時鐘接收數據時,我們需要注意兩個定時參數,以確保接收數據的可靠性。 建立時間(ts)是指數據連續處于有效邏輯電平且接收器準備好接收輸入信號所需的時間。 保持時間(tH)是指接收器采樣后,數據發生變化前需要保持在原有狀態的時間。 建立時間和保持時間在接收器的時鐘有效邊沿附近形成了一個穩定的窗口,以便接收器能夠可靠地采集數據。 圖3給出了一個上升沿時鐘信號的建立時間和保持時間。 通常,數字信號會在上升軌跡的中間切換電壓;因此時間基準標志通常放置在信號邊沿的正中央。

圖3.建立時間和保持時間在接收器的時鐘有效邊沿附近形成了一個穩定的窗口,以便接收器能夠可靠地采集數據。

2. 常用術語

在數字電路系統中,定時是最重要的因素之一。 數字通信的可靠性和精確度均取決于定時的質量。 然而,在實際應用中,任何事物都不是理想的。 以下是一些可以幫助您理解特定數字信號定時功能的常用術語和方法。

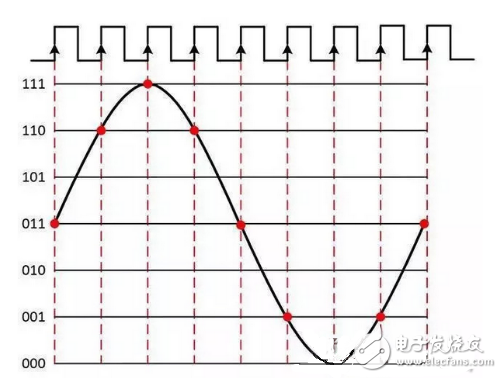

抖動

抖動是指事件的理想定時與實際定時之間的偏差。 為了理解這個概念,假設您正在發送一個數字正弦波并在坐標紙上繪制其圖形。 每個正方形相當于一個時鐘脈沖;由于垂直線之間的間隔是等距的,因此最后我們可以得到一個完美的周期性時鐘信號。 在每個時鐘脈沖上,您獲取3個數據點并將各點繪制在坐標紙上。 由于它具有周期性,因此您得到一個精準的正弦波。

圖4. 周期性采樣時鐘可讓數字系統進行正確、精準的通信。

現在,我們假設垂直線之間不是等距的。 這樣會使時鐘信號的周期性不那么明顯。 當您繪制數據時,它們之間的間隔并不相同,因此看起來不正確。

圖5. 如果時鐘信號發生了抖動,將引起數字波形發生變形。

在圖5中,您可以看到時鐘信號電平的切換距離是不均勻的;這就是時鐘的抖動。 盡管上圖抖動較為夸張,但是它說明了抖動的時鐘會導致采樣在不均勻的時間間隔上觸發。 這種不均勻導致要記錄和復制的波形發生變形。

現在看看只有1和只有0的數字信號的抖動。 請記住,抖動是指事件的理想定時與真實定時之間的偏差。 請注意單脈沖,抖動是指實際信號邊沿定時與理想時間位置的偏差。

圖6.單脈沖抖動是邊沿定時的偏差

抖動通常從基準信號的過零點處測量。 它通常來自于串擾、同步轉換輸出和其他定期發生的干擾信號。 抖動會隨著時間而發生改變,因此抖動的測量和量化可以是在秒級抖動范圍內通過示波器進行目視估算,也可以是按統計學方法進行測量,比如標準差隨時間的變化。

漂移

另一個常見的定時問題是漂移。 當發射器的時鐘周期與接收器的周期稍有不同時便會發生時鐘漂移。 起初,這種漂移影響不大。 然而,隨著時間的推移,這兩種時鐘信號之間的差別可能會變得顯著,并導致同步失敗或其他問題。

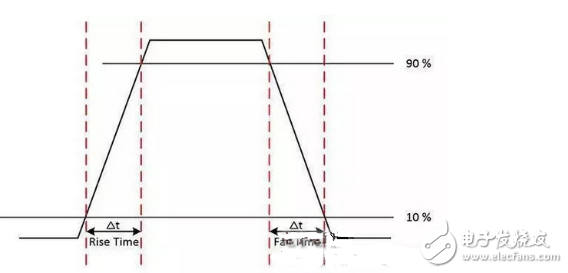

上升時間、下降時間和畸變

從理論上講,即使存在漂移,數字信號電平從0變化到1也只是瞬間發生。 然而,在實際中,信號從高電平變到低電平需要一定的時間。 上升時間(trise)是指信號從低電平變化到高電平,也就是從電壓的20%上升到80%所需要的時間。 下降時間(tfall) 是指信號從低電平變化到高電平,也就是從電壓的80%下降到20%所需要的時間。

圖7.上升時間和下降時間指示了信號在低電平和高電平之間轉換所需的時間。

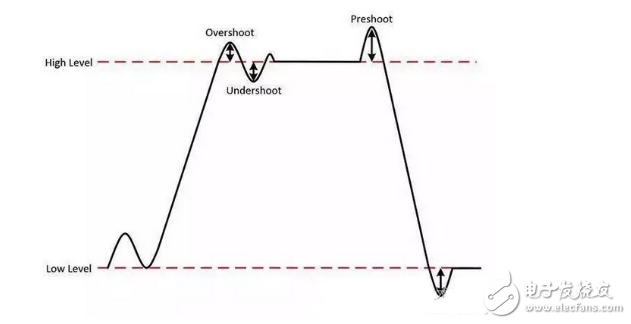

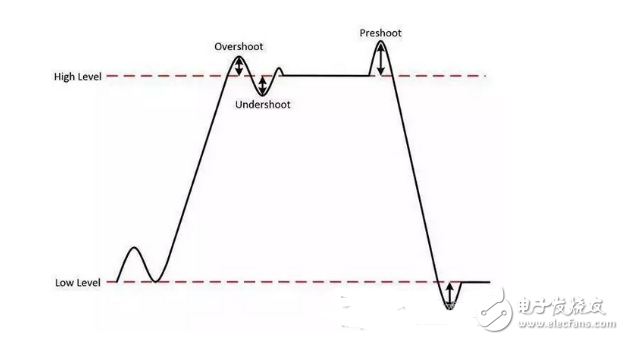

此外,在真實情況下,信號幾乎不會達到電壓電平并穩定地保持在該電平上。 當信號在邊沿之后超過電壓電平時,峰值失真被稱為過沖。 如果信號在邊沿之前超過了電壓電平時,峰值失真被稱為前沖。 在邊沿之間,如果信號漂移低于電壓電平時,則稱為下沖。

圖8.過沖、前沖和下沖統稱為偏差。

過沖、前沖和下沖統稱為偏差。 偏差的發生可能是由于電路板布局問題、不適時的終止或者半導體設備本身的質量問題。

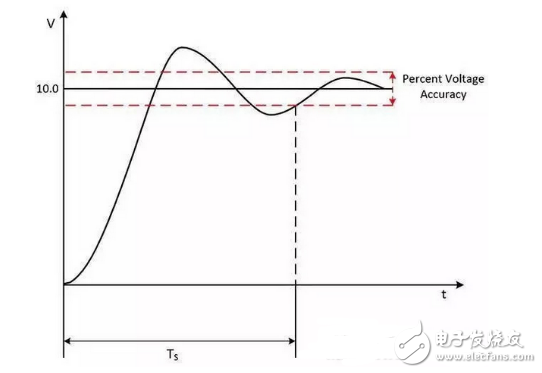

穩定時間

當數字信號到達電壓電平后,電壓會小幅反彈并穩定到一個常數值。 穩定時間(ts)是指放大器、繼電器或者其他電路達到穩定操作模式所需要的時間。 在進行數字信號采集的情況下,整個過程的穩定時間是指信號達到特定精確度并保持在該范圍所需要的總時間。

圖9.穩定時間是指信號達到特定精確度并保持在該范圍所需要的總時間。

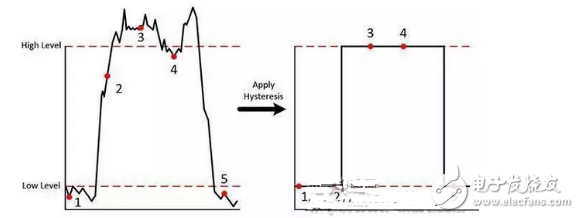

遲滯

遲滯是指從邏輯低電平到邏輯高電平以及從邏輯高電平到邏輯低電平的轉換之間探測到的電壓電平差。 它等于輸入低電壓減去輸入高電壓。

圖10.遲滯是指從邏輯低電平到邏輯高電平以及從邏輯高電平到邏輯低電平的轉換之間探測到的電壓電平差。

遲滯是一個有用的數字儀器屬性,因為它可以幫助數字系統過濾掉一些高頻率的噪聲。 這些噪聲的產生通常是由于邏輯電平轉換時的高邊沿速率反射,如果某個電壓閾值在邏輯狀態下發生改變,那么這些噪聲就會導致數字設備產生錯誤的電平轉換探 測。 圖11展示了這一現象。第一個樣本作為邏輯低電平被捕獲。 第二個樣本仍然是邏輯低電平,因為信號還沒有達到高電平閾值。 第三個和第四個樣本是邏輯高電平,第五個是邏輯低電平。

圖11. 遲滯可以過濾掉數字系統中部分高頻噪聲。

對于具有恒定電壓閾值的設備,系統的抗噪容量(NIM)和遲滯由用戶選擇的系統組件決定。 系統NIM和遲滯都會讓系統具有一定的抗噪水平,但是對于特定的邏輯系列,在這兩者之間總是存在一定的取舍—遲滯越多,NIM就越小,反之亦然。 在確定如何設置電壓閾值時,您需要仔細檢查系統的信號質量,并依此決定您是需要提高高電平和低電平(更大的NIM)時的抗噪性還是需要提轉換(更多的遲 滯)時的抗噪性。

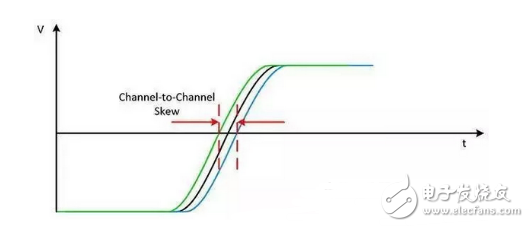

偏斜

偏斜是時鐘信號在不同時間到達不同部分。 與漂移不同的是,時鐘信號具有相同的周期;只不過它們到達的時間不相同。 達到時間的不同可能由很多因素引起,這些因素包括導線長度、溫度變化以及輸入電容的不同。 通道間偏斜通常指設備上所有數據通道的偏斜。 每次采集樣本時,每個數據通道采樣的時間點和其他數據通道的采樣時間點各不相同,但是每次時間差都會處在一個很小的窗口時間范圍內,這個窗口時間范圍稱為通道間偏斜。

圖12. 通道間偏斜通常指設備上所有數據通道的偏斜。

3. 總結

使用數字波形作為時鐘信號,時鐘信號具有固定周期,在數據傳輸過程中同步數字信號發射器和接收器。 時鐘信號的占空比是波形周期的百分比,也就是波形處于邏輯高電平所占的時間比。 時鐘的確定邊沿又稱為有效時鐘邊沿。 建立時間和保持時間在接收器的時鐘有效邊沿附近形成了一個穩定的窗口,以便接收器能夠可靠地采集數據。抖動是指事件的理論時間和實際時間之間的偏差;它會引起信號的失真。當發射器的時鐘周期與接收器的周期稍有不同時便會發生時鐘漂移,它將會導致同步失敗和其他錯誤。 上升時間和下降時間指示了信號在低電平和高電平之間轉換所需的時間。 過沖、前沖和下沖統稱為偏差,是系統出現錯誤的指示。 穩定時間是指信號達到一定的精度并保持在這個精度范圍內所經歷的時間。 遲滯可以過濾掉數字系統中的部分高頻噪聲。 偏斜會導致時鐘信號在不同時間到達不同分量。

電子發燒友App

電子發燒友App

評論