分配FPGA引腳的幾個原則

? ? ? ? 現在的FPGA正變得越來越復雜,向引腳分配信號的任務曾經很簡單,現在也變得相當繁復。下面這些用于向多用途引腳指配信號的指導方針有助于設計師根據最多到最少的約束信號指配原則提前考慮信號指配,并減少反復的次數。

這里有一個前提,即假定設計師已經根據設計的大概規模和信號要求確定了目標器件范圍和型號。對以下每一步都應在考慮單極信號前優先考慮差分對信號。

最先指配那些只能在特定引腳上工作的特殊信號,正常情況下是指串行I/O信號和全局時鐘信號。其次指配大型和/或高速信號總線,特別是那些要跨越多個庫或區域的信號。如果總線需要局部時鐘,那么就要考慮具有更多局部時鐘引腳的庫或區域,并先指配局部時鐘。

如果針對FPGA器件采用了多種I/O標準,那么設計師還必須先考慮將I/O信號映射到庫/區。這一步需要慎重考慮,因為許多I/O標準和參考電壓是不兼容的。一些I/O標準要求在特殊引腳上輸入參考電壓,使得這些引腳不可再用于一般用途。將高速輸出和雙向信號分開指配在一定程度上可避免同時開關輸出噪聲(SSO)問題。

第三,采用第二步中相同的基本規則指配速度較慢和約束較少的總線,但不用太多考慮SSO等問題。第四,最后完成個別信號的指配。如果只剩下少量引腳,或在第一次反復時用完了所有的引腳,可以考慮選用具有更多I/O數量的下一種器件,因為根據市場情況肯定還會臨時增加某些功能,而且沒有哪個設計師愿意在設計的最后階段再做一遍指配過程吧。

在以上每一步中,要建立含有正確信號分配和I/O標準的約束文件,以及含有I/O設計部分的HDL文件。然后再開始布局和布線,因為按從最多約束信號到最少約束信號的順序可以更好地發現錯誤

在芯片的研發環節,FPGA 驗證是其中的重要的組成部分,如何有效的利用 FPGA 的資源,管腳分配也是必須考慮的一個重要問題。一般較好的方法是在綜合過程中通過時序的一些約束讓對應的工具自動分配,但是從研發的時間段上來考慮這種方法往往是不可取的,RTL驗證與驗證板設計必須是同步進行的,在驗證代碼出來時驗證的單板也必須設計完畢,也就是管腳的分配也必須在設計代碼出來之前完成。所以,管腳的分配更多的將是依賴人,而非工具,這個時候就更需要考慮各方面的因素。

? ? ? ?如何分配FPGA引腳信號

綜合起來主要考慮以下的幾個方面:

1、 FPGA 所承載邏輯的信號流向。

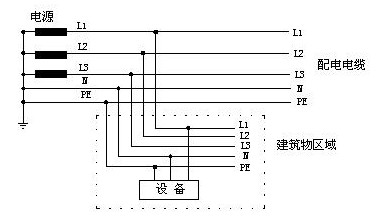

IC 驗證中所選用的 FPGA 一般邏輯容量都非常大,外部的管腳數量也相當的豐富,這個時候就必須考慮到PCB 設計時的布線的難度,如果管腳的分配不合理,那么有可能在PCB 設計時出現大量的交叉的信號線,這給布線帶來很大的困難,甚至走不通,或者是即便是布線走通了,也有可能由于外部的延時過大而不滿足時序方面的要求。所以在管腳分配前對 FPGA 工作的環境要相當的熟悉,要對其中的信號來自哪里去向何方非常的清楚,這就按照連線最短的原則將對應的信號分配到與外部器件連線最近的 BANK 中

2、 掌握 FPGA 內部 BANK 的分配的情況。

現在 FPGA 內部都分成幾個區域,每個區域中可用的 I/O 管腳數量各不相同。在 IC 驗證中都是采用了ALTERA 與 XILINX系列的 FPGA ,這兩個廠商的 FPGA中內部BANK的分配有一定的差異,這可以在設計中查閱相關的手冊。下面與 ALTERA 中 Stratix II系列的 FPGA 內部 BANK 的分配為例來進行說明。

圖中詳細說明了 FPGA 內部 BANK 的分配情況和每個 BANK 中所支持的 I/O 標準。根據 FPGA 中內部BANK 的分配的情況,同時結合圖 1 中信號的流向也就可以大體固定

FPGA 在單板中的方向,同時按照就近的原則將相關的信號分配到相關的 BANK 中,這樣的方法可以完成一般信號的分配。

3、 掌握所選 FPGA 每個 BANK 所支持的 I/O 標準。

可以看出 FPGA 內部的每個 BANK 所支持的 I/O 的標準不盡相同,所以管腳的分配時要將支持相同標準的管腳都集中到一個 BANK 中,因為 FPGA 中同一個BANK一般不同時支持兩種 I/O 標準,當然也有例外,這就需要查閱相關 I/O 標準所要求的工作條件。

4、 關注特殊信號的管腳的分配

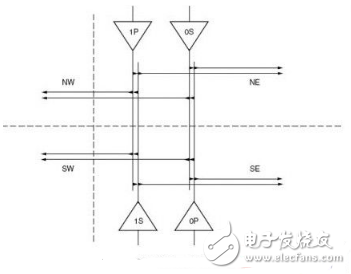

這里的特殊信號主要是指時鐘信號與復位信號,或者是一些要求驅動能力較高的信號。時鐘信號一般都是要求分配到全局的時鐘管腳,這樣獲得的時間的延遲將是最小的,驅動也最強。復位信號因為要求同步性好驅動的能力強,所以一般的情況下也會從全局的時鐘管腳送入。在分配時鐘時,根據時鐘的多少分配的策略差別很大,也需要重點關注,這需要查閱相應的手冊看哪些時鐘分別能到達哪些區域,一般的時鐘都是差分時鐘,這個時候如果所用的不是差分時鐘就需要注意 P 端與 N 端一般不能同時分配給不同的時鐘信號。如下圖所示 XILINX 系列的 FPGA 中成對的時鐘如果是同時采用那么就不能同時到達相同的區域,因為到達相同區域的時鐘線只有一根。

所以在時鐘較少時最好成對的P和S不要同時使用,而是只是選擇P或者是N這樣就不會出現沖突的情況。

5、 兼顧信號完整性的考慮。

由于在分配中常常會出現總線分配的情況,同時大量的總線又有可能常常是同時翻轉,這樣就會帶來了一系列信號完整性的問題,所以在管腳分配時大量同時翻轉的信號盡量分開。

電子發燒友App

電子發燒友App

評論