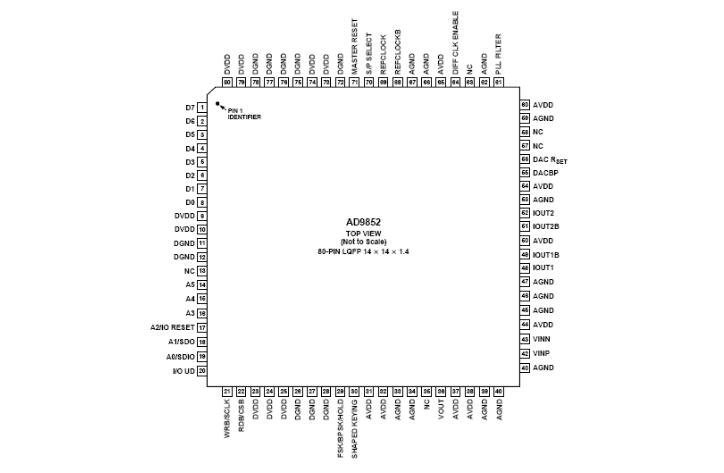

AD9854的結構與功能介紹

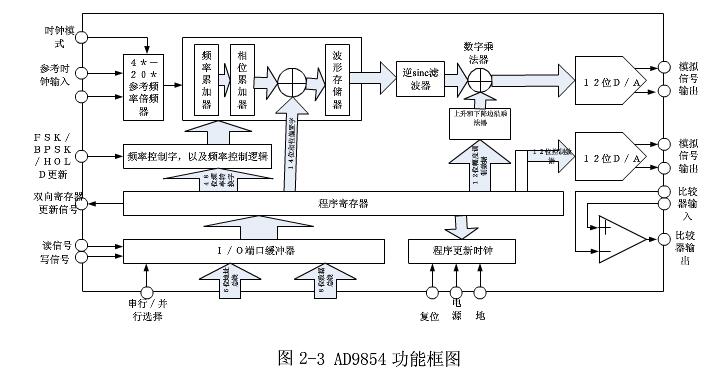

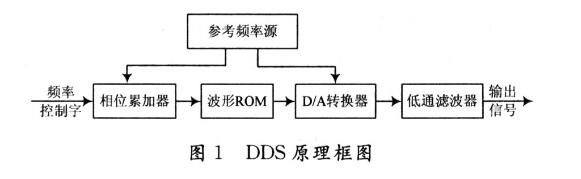

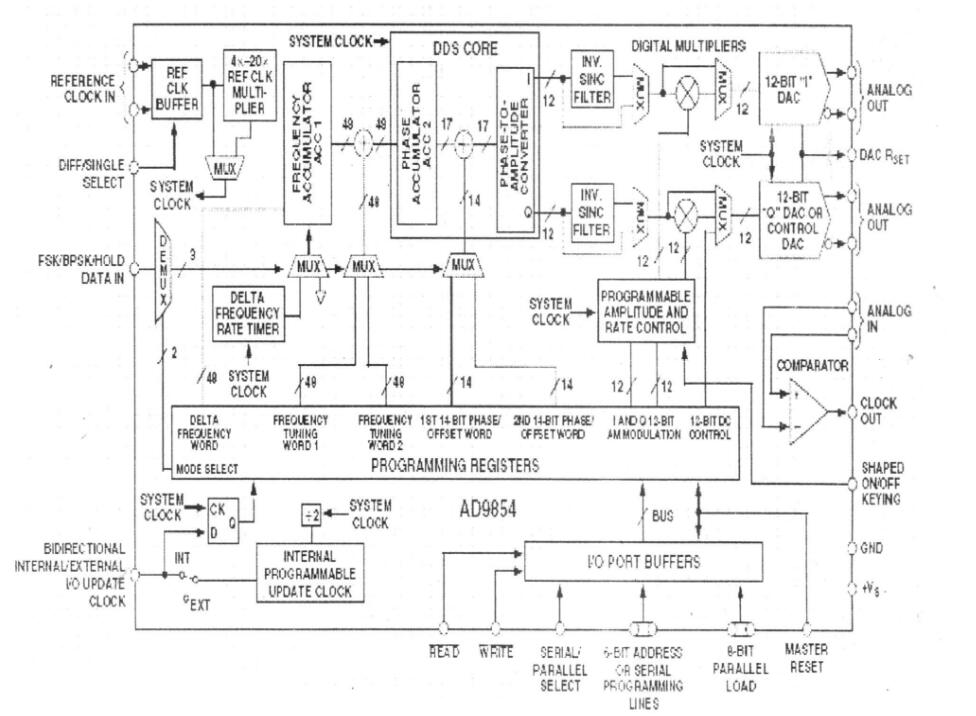

AD9854是ADI公司的一款CMOS工藝300MSPS正交的完整DDS芯片。AD9854是一款高度集成的芯片,采用先進的DDS技術,內部集成了300MHz的DDS核(ASVZ系列為300MHz,ASTZ系列為200MHz)、高速高性能雙路正交DAC、反辛格濾波器、雙路48位頻率寄存器、雙路14位相位寄存器、4~20倍時鐘倍頻器、調幅模塊和3ps均方根抖動超高速比較器。DDS核內含48位相位累加器和正弦表。當用穩定精密的時鐘源作為基準時,AD9854能產生頻率和相位非常穩定、幅度編程可調的正弦或余弦信號,可用作通信、雷達和其它許多應用中的捷變LO。

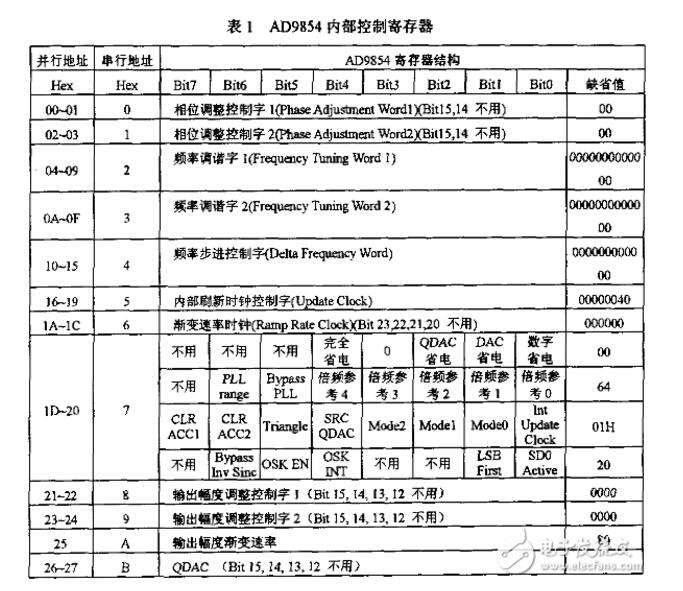

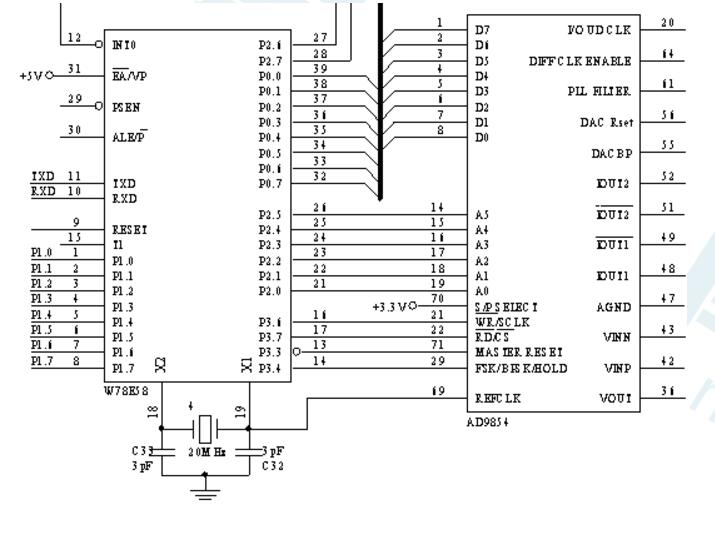

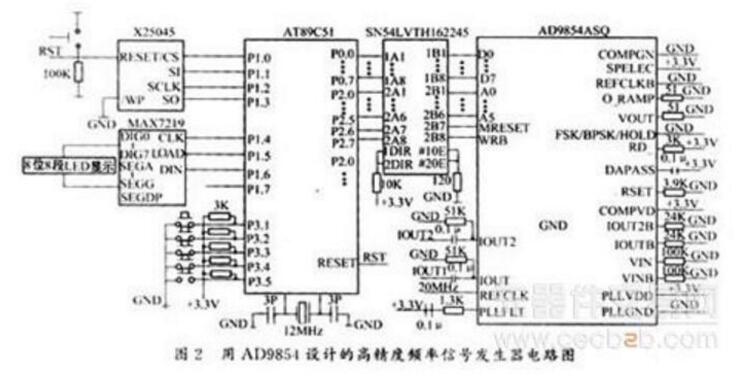

AD9854采用3.3V單電源供電,允許電源誤差為+5%,最大功耗4.06W。由于整體功耗很大,器件內部控制寄存器設置了可以關斷比較器、QDAC、數字部分、PLL、反辛格濾波器等模塊的關斷位,用戶可以將未使用的模塊關閉,需要時再打開,減小芯片功耗和發熱。AD9854的控制接口采用節省I/O口的2線或3線SPI協議串行接口和100MHz高速并行接口。AD9854片上重要模塊介紹如下:

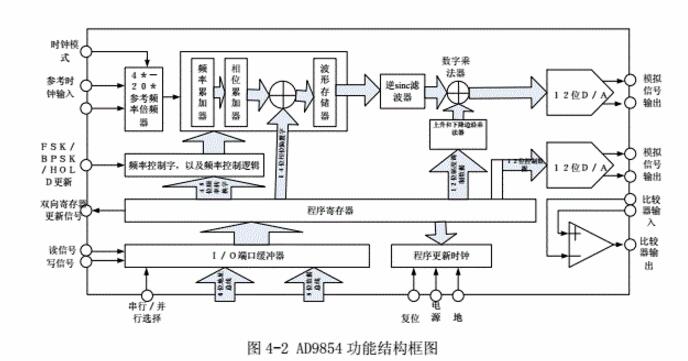

(1)DDS核

AD9854中的新型高速DDS核提供了48位頻率分辨率,在系統時鐘300MHz的情況下仍能夠精確到1,保持17位即可確保該芯片具有優秀的無雜散動態范圍(SFDR),100MHz()輸出下SFDR達到80dB。

根據奈奎斯特采樣定理,在300MHz系統時鐘下,AD9854理論上最高可以輸出150MHz的信號,在實際應用中,輸出信號達到150MHz時,信號質量很差,幅度衰減非常大,實際可用最高頻率大概在130MHz左右。AD9854的輸出信號數字調諧頻率可以達到每秒1億次。

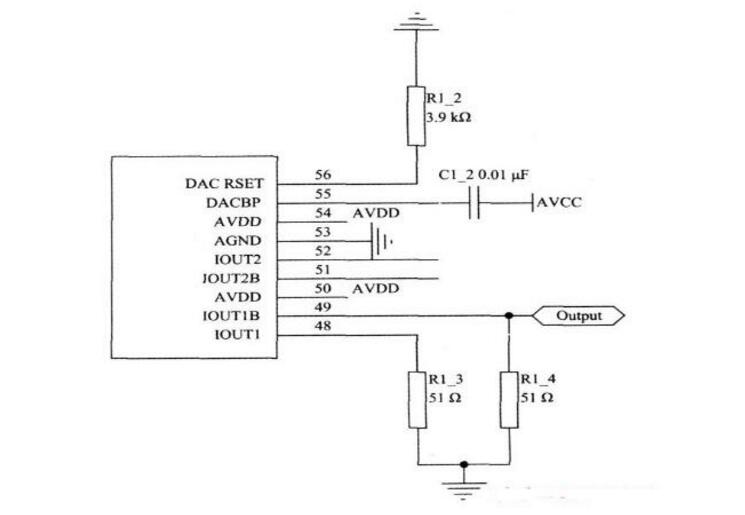

(2)雙路正交DAC

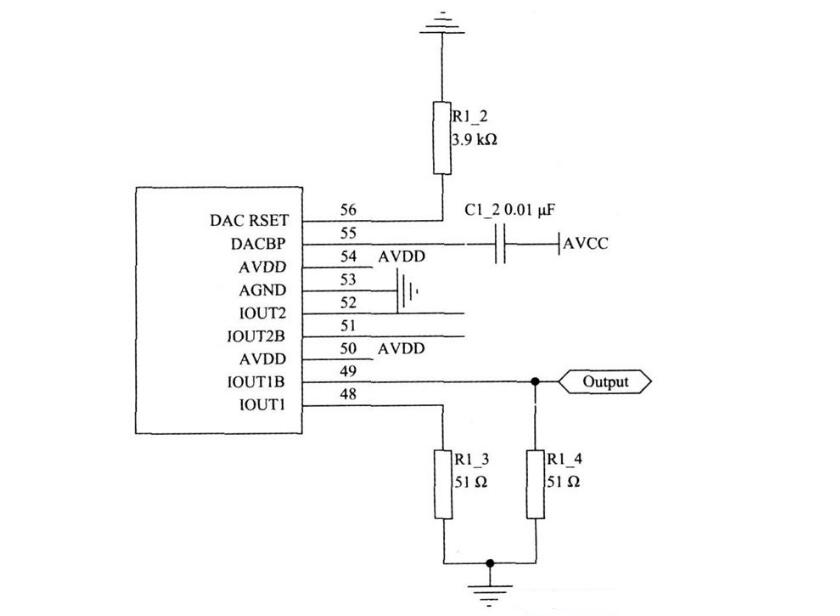

AD9854內部有兩路DAC——IDAC和QDAC。兩路DAC的滿量程輸出幅度由第56引腳的電阻——中電流決定,最大不超過20mA,當設置滿量程電流在20mA時可獲得最佳SFDR性能。的電流由下式決定:

式中,為輸出滿量程電流。在輸出高頻信號時,總諧波失真變得明顯,雙路DAC的滿量程電流更應合理設置以獲得最佳SFDR。兩路DAC都可以由程序設定是否經過反辛格濾波器。

IDAC內部固定于正弦表連接,QDAC可配置為與內部余弦表連接或獨立出來,作為一個單獨的高速電流DAC使用,此時QDAC的輸出幅度由用戶寫入的12位二進制補碼決定。當QDAC不用時可以關斷以降低功耗。

(3)反辛格濾波器(反sinc濾波器)。

DDS是靠高速DAC將模擬正弦信號量化輸出的過程,輸出信號是由一個一個小臺階構成的。這時信號的頻譜為sinc包絡,由于DAC的零階保持效應,輸出信號的頻譜為sinc包絡與脈沖流經過付里葉變換的乘積,所以輸出頻譜會有遵從sine響應的固有的畸變。反辛格濾波器的頻譜響應為反sinc包絡,數據經過該濾波器就可以校正sinc包絡形的畸變。反辛格濾波器使得寬帶信號在低頻和高頻使得幅度變化不會太大,如QPSK信號。反辛格濾波器能起到穩定幅度的作用,但功耗很大,在300MHz頻率下達到400mA以上,且會帶來插入損耗。

(4)時鐘倍頻器。

AD9854的參考時鐘為300MHz,在最大時鐘頻率下頁能夠精確到1。但是這是基于所提供的時鐘源為高精度時鐘源,如何提供這一高精度、高頻參時鐘是一個不得不解決的問題。

有廠商生產這樣的振蕩器,但性價比太低,一個300MHz的高精度振蕩器不比AD9854便宜。而且300MHz的振蕩信號還很容易耦合到其他電路中,干擾有用信號。為此,AD9854內設了一個4-20倍可編程時鐘倍頻器,用戶可以外接一個高精度、低頻的時鐘源,然后經內部倍頻后再共給DDS核使用。需要指出的是,AD9854提供兩種時鐘輸入方式——單端輸入和雙端輸入。建議用戶將單端時鐘經用變壓器或時鐘芯片(如MC100LVEL16)把單端時鐘轉換為差分信號再輸入到DDS芯片,這樣能獲得更好的性能。

(5)調幅模塊。

AD9854在內部還集成了調幅模塊,可以通過程序設定DAC輸出最大幅度。可以通過高速控制器,如FPGA、DSP對信號進行調幅操作,同時可以用此功能軟件穩幅。

(6)比較器

AD9854的片上比較器具有300MHz切換速率、3ps均方根抖動,輸出可以用作其他電路的高精度時鐘源。

4.總結

AD9854充分體現了DDS技術的高分辨率、快速轉換時間、易于程序控制的特點。AD9854的高性能使得其在諸多場合得以應用,如可編程時鐘發生器、雷達和掃描系統的FM線性調頻源、測試與測量設備等。

電子發燒友App

電子發燒友App

評論