什么是共模輸入電壓

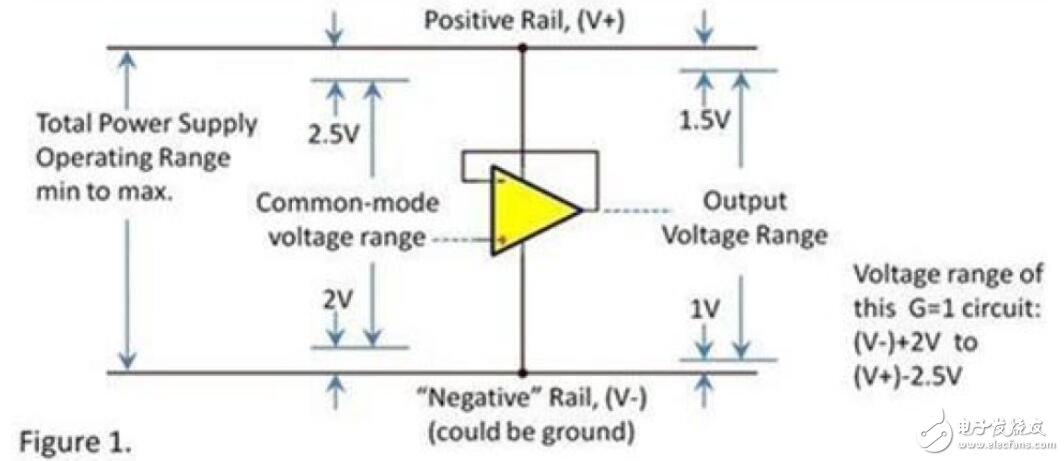

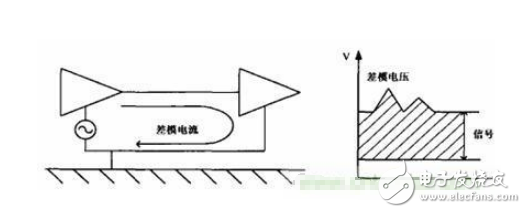

共模輸入電壓,指的是相對于公共地而言的信號。共模和差模其實沒有嚴格的定義。只是說共模是相對于公共地而言的信號,而差模則是兩個信號的差(注意這里沒有強調公共地,你也可以將地作為一個信號處理)。單純孤立地討論共模和差模沒有多大的意義,必須結合具體的設計對象——如差分信號線。

定義

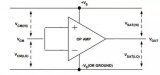

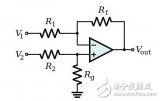

設差分信號線的正端電壓為Vp,負端電壓為Vn。自然你可以定義Vp或Vn為共模電壓(都相對于公共地),而Vp - Vn為差模電壓。但是這種孤立的定義和分析沒有意義。最簡單的,Vp和Vn到底哪個代表了差分信號線上的“共模”電壓?如果干擾只作用在Vp或Vn上(或不平衡),那算什么干擾?“共模抑制”對此是否有效?

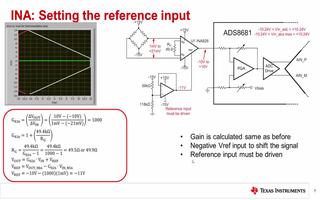

看看這兩個式子:(Vp + Vn) / 2,(Vp - Vn) / 2。前一個是兩個信號線相對于公共地的平均值。不僅如此,這兩個式子把差分信號線上的共模和差模特性非常自然地區分開來了,而且具有等權。如果只有(Vp + Vn) / 2干擾,而沒有(Vp - Vn) / 2的干擾(這就是所謂的共模干擾),共模抑制就會完全抑制它。如果只有(Vp - Vn) / 2 信號,而沒有(Vp + Vn) / 2 信號(其實Vp和Vn都有信號,只是抵消而已),那便是我們非常熟悉的差分信號。

公式

電子發燒友App

電子發燒友App

評論