AT89S52各引腳的功能:

下面簡單介紹AT89S52各引腳的功能,更多信息請查閱Atmel公司的技術(shù)文檔。 VCC:電源。 GND:地。

P0 口:P0 口是一個8 位漏極開路的雙向I/O 口。作為輸出口,每位能驅(qū)動8 個TTL邏輯電平。對P0 端口寫“1”時,引腳用做高阻抗輸入。當(dāng)訪問外部程序和數(shù)據(jù)存儲器時,P0 口也被作為低8 位地址/數(shù)據(jù)復(fù)用。在這種模式下,P0 具有內(nèi)部上拉電阻。在Flash編程時,P0 口也用來接收指令字節(jié);在程序校驗(yàn)時,輸出指令字節(jié)。在程序校驗(yàn)時,需要外部上拉電阻。

P1 口:P1 口是一個具有內(nèi)部上拉電阻的8 位雙向I/O 口,P1 輸出緩沖器能驅(qū)動4 個TT

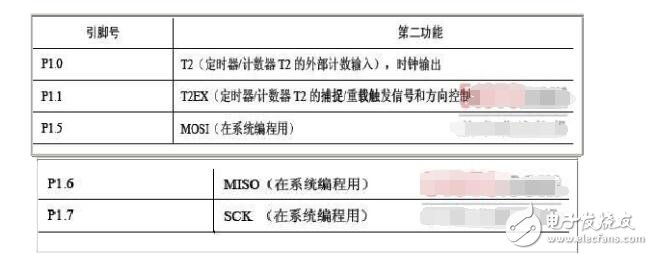

邏輯電平。當(dāng)對P1 端口寫“1”時,內(nèi)部上拉電阻把端口拉高,此時可以作為輸入口使用。當(dāng)作為輸入使用時,被外部拉低的引腳由于內(nèi)部電阻的原因,將輸出電流(IIL)。此 外,P1.0 和P1.2 分別作為定時器/計(jì)數(shù)器2 的外部計(jì)數(shù)輸入(P1.0/T2)和定時器/計(jì)數(shù)器2的觸發(fā)輸入(P1.1/T2EX),具體如表1-1 所示。在Flash編程和校驗(yàn)時,P1口接收低8 位地址字節(jié)。

P2 口:P2 口是一個具有內(nèi)部上拉電阻的8 位雙向I/O 口,P2 輸出緩沖器能驅(qū)動4 個TT邏輯電平。對P2 端口寫“1”時,內(nèi)部上拉電阻把端口拉高,此時可以作為輸入口使用。當(dāng)作為輸入使用時,被外部拉低的引腳由于內(nèi)部電阻的原因,將輸出電流(IIL)。在訪問

表1口部分管腳的第二功能

外部程序存儲器或用16 位地址讀取外部數(shù)據(jù)存儲器(如執(zhí)行MOVX @DPTR)時,P2 口送出高8 位地址。在這種應(yīng)用中,P2 口使用很強(qiáng)的內(nèi)部上拉發(fā)送1。在使用8 位地址(如MOVX @RI)訪問外部數(shù)據(jù)存儲器時,P2口輸出P2鎖存器的內(nèi)容。在Flash編程和校驗(yàn)時,P2 口也接收高8位地址字節(jié)和一些控制信號。 P3 口:P3 口是一個具有內(nèi)部上拉電阻的8 位雙向I/O 口,P2 輸出緩沖器能驅(qū)動4 個TT

邏輯電平。對P3 端口寫“1”時,內(nèi)部上拉電阻把端口拉高,此時可以作為輸入口使用。當(dāng)作為輸入使用時,被外部拉低的引腳由于內(nèi)部電阻的原因,將輸出電流(IIL)。P3 口也作為AT89S52 特殊功能(第二功能)使用,如表1-2所示。在Flash編程和校驗(yàn)時,P3口也接收一些控制信號。

表2 P3口部分管腳的第二功能

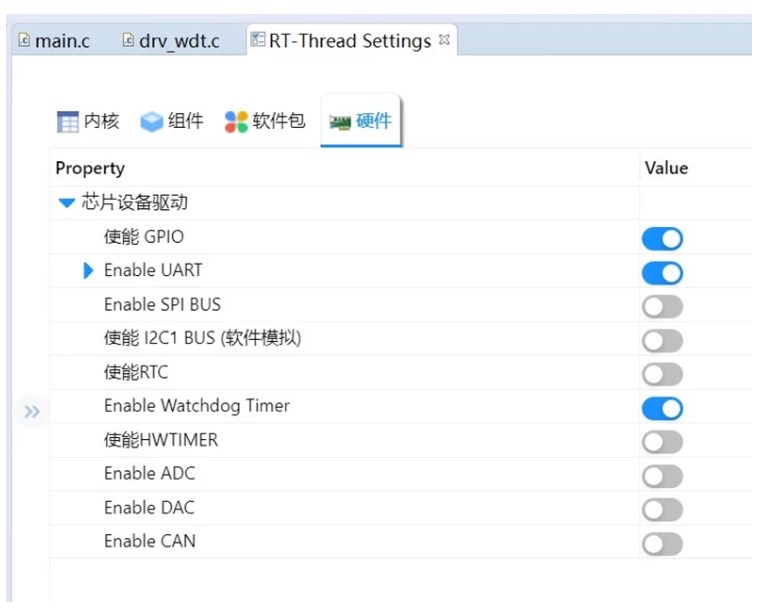

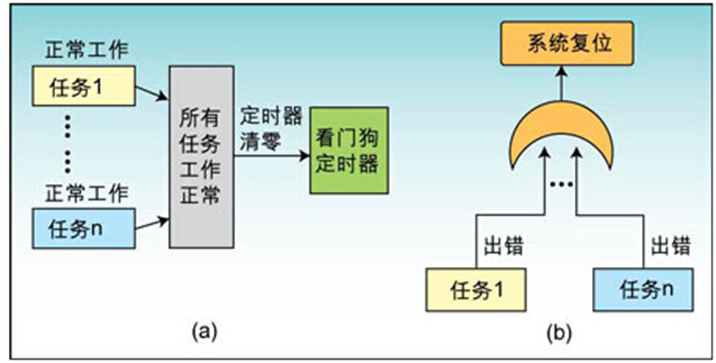

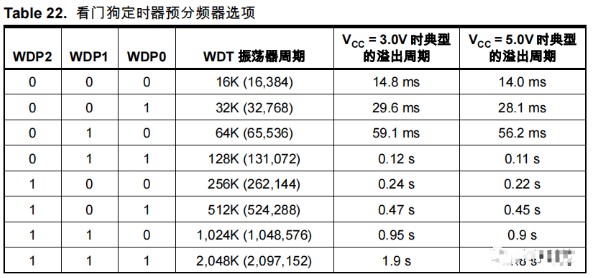

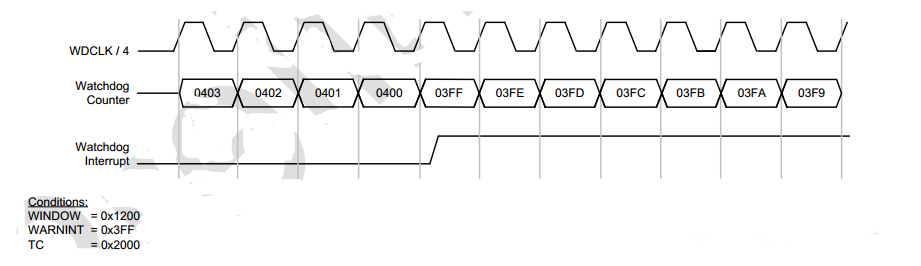

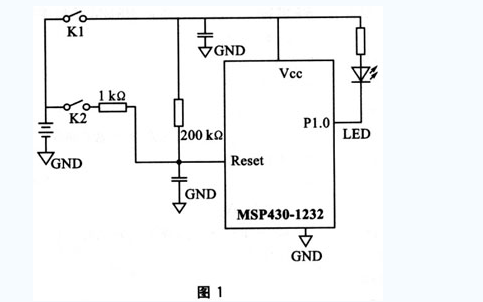

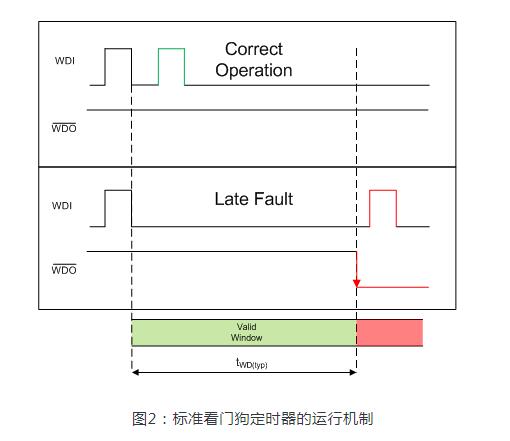

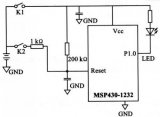

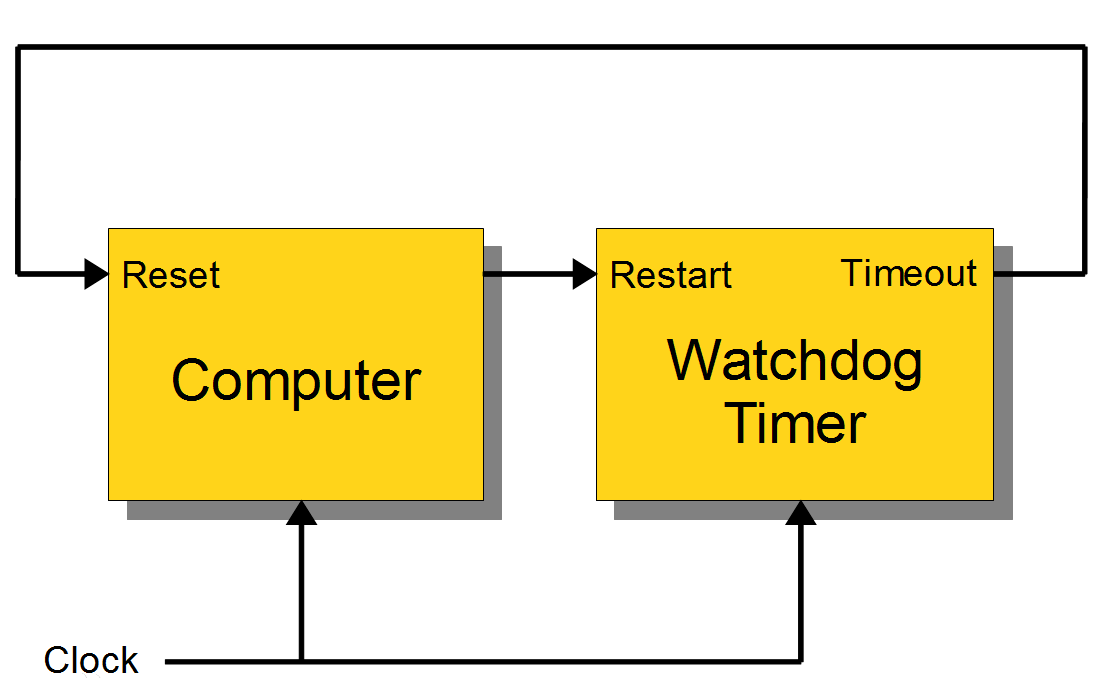

RST: 復(fù)位輸入。在晶振工作時,RST腳持續(xù)兩個機(jī)器周期高電平將使單片機(jī)復(fù)位。看門狗計(jì)時完成后,RST 腳輸出96 個晶振周期的高電平。特殊寄存器AUXR(地址8EH)上的DISRTO 位可以使此功能無效。在DISRTO 默認(rèn)狀態(tài)下,復(fù)位高電平有效。

ALE/PROG:地址鎖存控制信號(ALE)在訪問外部程序存儲器時,鎖存低8 位地址的輸出脈沖。在Flash編程時,此引腳(PROG)也用做編程輸入脈沖。 在一般情況下,ALE 以晶振六分之一的固定頻率輸出脈沖,可用來作為外部定時器或時鐘使用。然而,特別強(qiáng)調(diào),在每次訪問外部數(shù)據(jù)存儲器時,ALE 脈沖將會跳過。如果需要,通過將地址為8EH的SFR的第0 位置“1”,ALE 操作將無效。這一位置“1”,ALE 僅在執(zhí)行MOVX 或MOVC指令時有效。否則,ALE 將被微弱拉高。這個ALE 使能標(biāo)志位(地址為8EH的SFR的第0 位)的設(shè)置對微控制器處于外部執(zhí)行模式下無效。

PSEN:外部程序存儲器選通信號(PSEN)是外部程序存儲器選通信號。當(dāng)AT89S52從外部程序存儲器執(zhí)行外部代碼時,PSEN 在每個機(jī)器周期被激活兩次,而在訪問外部數(shù)據(jù)存儲器時,PSEN將不被激活。

EA/VPP:訪問外部程序存儲器控制信號。為使能從0000H 到FFFFH 的外部程序存儲器讀取指令,EA必須接GND。為了執(zhí)行內(nèi)部程序指令,EA應(yīng)該接VCC。在Flash編程期間,EA也接收12伏VPP電壓。

電子發(fā)燒友App

電子發(fā)燒友App

評論