D觸發器,是時序邏輯電路中必備的一個基本單元,學好 D 觸發器,是學好時序邏輯電路的前提條件,其重要性不亞于加法器,二者共同構成數字電路組合、時序邏輯的基礎。

2023-10-09 17:26:57 234

234

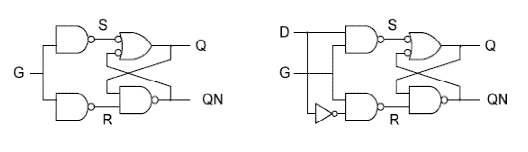

在數字電路中,RS觸發器(也稱為RS鎖存器)是一種基本的雙穩態觸發器,它可以通過特定的輸入信號來實現置位(Set)和復位(Reset)操作。

2023-09-28 16:31:07 1317

1317 觸發器(Flip-Flop)是數字電路中的一種時序邏輯元件,用于存儲二進制位的狀態。它是數字電路設計中的基本構建塊之一,常用于存儲數據、實現狀態機、控制信號的生成等。觸發器可以看作是一種特殊

2023-08-31 10:50:19 1436

1436

在傳統的異步 RS 觸發器中,當輸入的 R 和 S 同時為 1 時,會引發互鎖問題,輸出結果是不確定的。為了避免這個問題,常常使用帶有使能控制的同步觸發器,如帶有時鐘信號的 D 觸發器或 JK 觸發器。這些觸發器在時鐘邊沿上才會響應輸入信號,解決了異步 RS 觸發器的互鎖問題。

2023-08-28 15:44:35 641

641 信號發生變化時,觸發器會切換到另外一種狀態并輸出相應的信號。觸發器在數字電路中起著至關重要的作用,其可靠性和穩定性是數字電路設計的關鍵因素之一。 觸發器的種類繁多,如SR觸發器、D觸發器、JK觸發器等。其中,JK觸發器是

2023-08-24 15:50:35 235

235 D觸發器組成音頻信號發生器? D觸發器是一種數字邏輯電路元件,它是由若干個邏輯門組成的,常用于數字系統中的寄存器、計數器等。D觸發器在數字系統中起到很重要的作用,它能夠存儲和傳輸數字信號,并且能

2023-08-24 15:50:29 160

160 觸發器的輸出狀態由什么決定? 觸發器是一種數字電路元件,用于存儲和轉換電信號。它通常由幾個門電路構成,并能夠在符合特定條件時改變輸出狀態。觸發器的輸出狀態是由輸入信號和內部反饋電路共同決定的。在本篇

2023-08-24 15:50:23 276

276 用D觸發器設計一個序列發生器 怎么用D觸發器做序列信號發生器? 序列發生器是數字電子技術中常用的電路模塊之一,它可以用來生成一系列的數字信號序列。在數字電路中,D觸發器是一種被廣泛使用的數字邏輯組件

2023-08-24 15:50:17 549

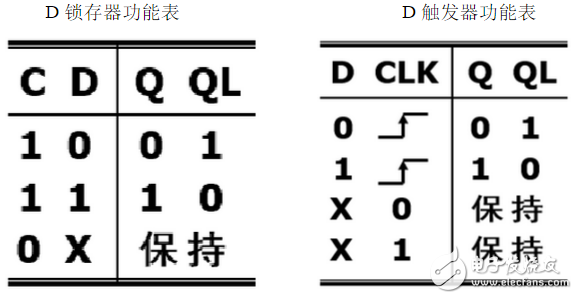

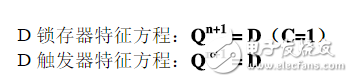

549 請簡述鎖存器與觸發器的概念,并分析二者的區別。

2023-08-15 09:24:10 646

646

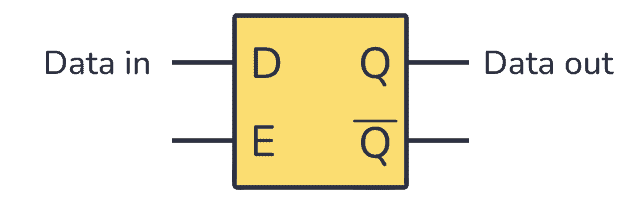

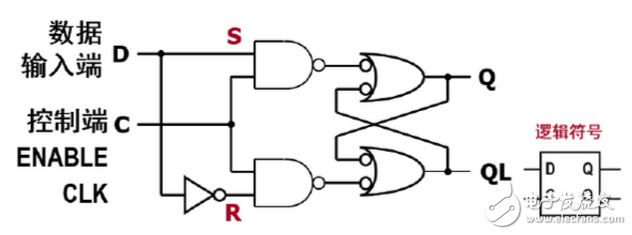

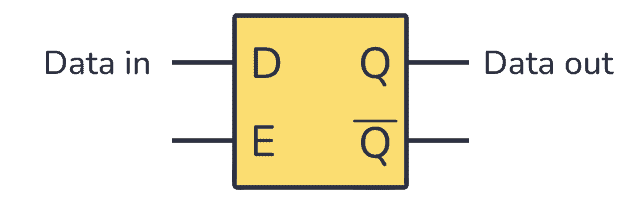

D鎖存器是最常用于在數字系統中存儲數據的邏輯電路。它基于 S-R鎖存器,但沒有“未定義”或“無效”狀態問題。在本教程中,您將了解它的工作原理、其真值表以及如何使用邏輯門構建一個。

2023-06-29 14:14:03 1246

1246

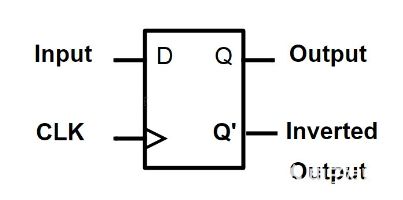

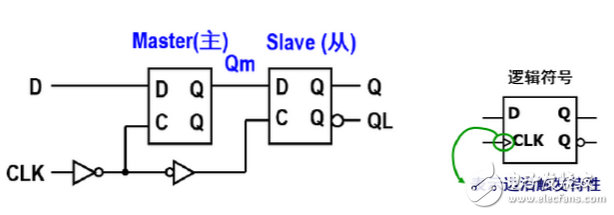

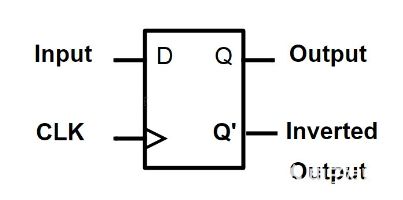

鎖存器和觸發器有時組合在一起,因為它們都可以在其輸出上存儲一位(1或0)。與鎖存器相比,觸發器是需要時鐘信號(Clk)的同步電路。D 觸發器僅在時鐘從

2023-06-29 11:50:18 5258

5258

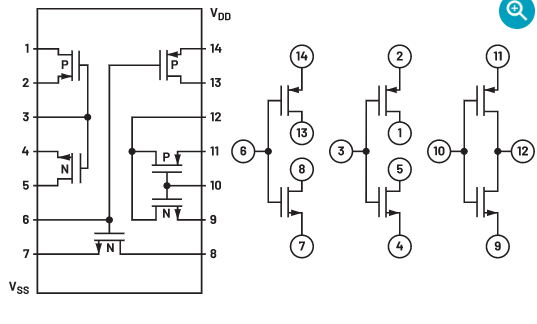

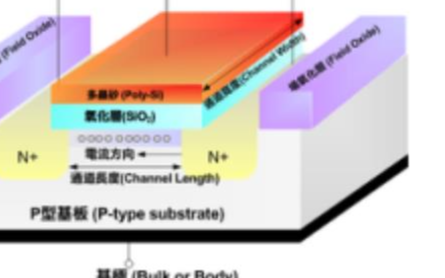

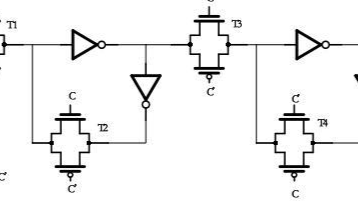

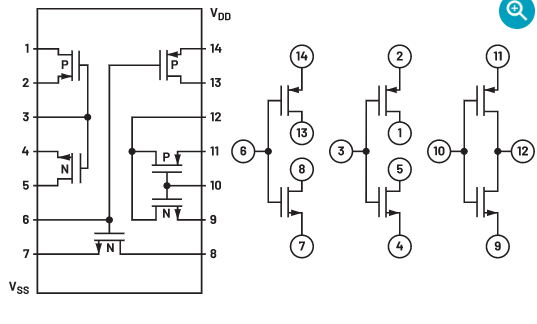

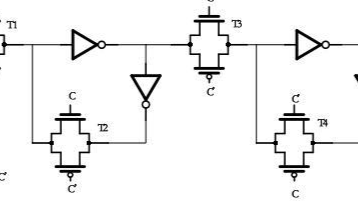

本實驗活動的目標是進一步強化上一個實驗活動 “ADALM2000實驗:使用CD4007陣列構建CMOS邏輯功能” 中探討的CMOS邏輯基本原理,并獲取更多使用復雜CMOS門級電路的經驗。具體而言,您將了解如何使用CMOS傳輸門和CMOS反相器來構建D型觸發器或鎖存器。

2023-05-29 14:16:27 345

345

本文旨在總結近期復習的數字電路D觸發器(邊沿觸發)的內容。

2023-05-22 16:54:29 3707

3707

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的那些事。

2023-05-12 16:37:31 975

975

鎖存器(Latch)是一種基本的數字電路元件,用于存儲二進制數字的狀態信息,并能夠在需要時通過加電或控制信號的作用保持狀態。它通常由幾個邏輯門組成,可以實現簡單的存儲、移位、計數等功能。鎖存器在數字電路

2023-04-09 18:45:34 4102

4102 鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態,當Gate輸入為高電平時,輸入D透明傳輸到輸出Q;當Gate從高變低或者保持低電平時,輸出Q被鎖存保持不變。鎖存器是電平觸發的存儲器。

2023-03-23 14:48:54 1357

1357

的數據和運算結果,它被廣泛的用于各類數字系統和計算機中。其實寄存器就是一種常用的時序邏輯電路,但這種時序邏輯電路只包含存儲電路。寄存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1

2011-10-09 16:19:46

八進制透明鎖存器(三態);八進制 D 觸發器(三態)-74F373_374

2023-03-03 20:05:16 0

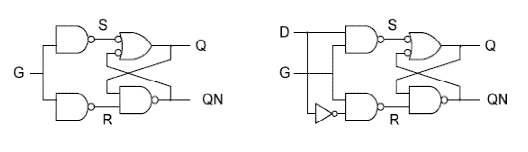

0 其中R、S分別是英文復位Reset和置位Set的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。

2023-02-08 09:19:45 2572

2572 主要內容: ·雙穩態器件 ·鎖存器常見結構 ·鎖存器的應用 ·觸發器 ·觸發器的建立時間和保持時間 1、雙穩態器件 ** 雙穩態器件**是指穩定狀態有兩種,一種是0,一種是1的器件;雙穩態器件

2023-01-28 09:28:00 2426

2426

D 觸發器或數據觸發器是一種觸發器,它只有一個數據輸入“D”和一個時鐘脈沖輸入, 這種觸發器也稱為延遲觸發器,經常用于許多時序電路,如寄存器、計數器等。下面一起來了解一下D觸發器不同應用下的電路圖。

2023-01-06 14:19:46 1874

1874 1:鎖存器、觸發器、寄存器的關聯與區別 首先應該明確鎖存器和觸發器是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合邏輯電路的特性。 鎖存

2022-12-19 12:25:01 3721

3721 來源:羅姆半導體社區 觸發器的電路圖由邏輯門組合而成,其結構均由R-S鎖存器派生而來(廣義的觸發器包括鎖存器)。觸發器可以處理輸入、輸出信號和時鐘頻率之間的相互影響。 在R-S鎖存器的前面加一個由

2022-11-29 17:35:40 1584

1584 什么是RS觸發器 其中R、S分別是英文復位 Reset 和置位 Set 的縮寫,作為最簡單的一種觸發器,是構成各種復雜觸發器的基礎。RS觸發器的邏輯電路圖如下圖所示。 RS觸發器可以用與非門實現或者

2022-10-19 17:49:59 5720

5720

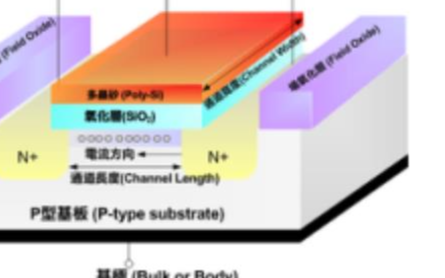

D觸發器也稱為“延遲觸發器”或“數據觸發器”,主要用于存儲1位二進制數據,是數字電子產品中廣泛使用的觸發器之一。除了作為數字系統中的基本存儲元件外,D觸發器也被視為延遲線元件和零階保持元件。

2022-10-11 17:21:02 97371

97371

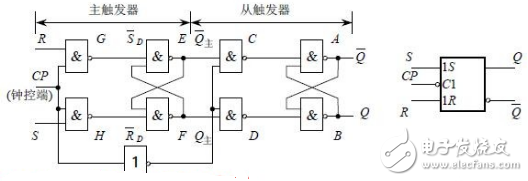

上圖是用與非門實現的D觸發器的邏輯結構圖,CP是時鐘信號輸入端,S和R分別是置位和清零信號,低有效; D是信號輸入端,Q信號輸出端;

2022-09-19 15:22:24 3240

3240 每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

2022-07-22 10:05:01 2518

2518 每個 Slice 有 8 個 FF 。四個可以配置為 D 型觸發器或電平敏感鎖存器,另外四個只能配置為 D 型觸發器,但是需要記得是:當原來的四個 FF 配置為鎖存器時,不能使用這四個 FF 。

2022-03-15 11:59:34 7158

7158 這是一個系列文章,從最簡單的門電路介紹,從基礎的鎖存器、觸發器、編碼器、譯碼器等一系列數字邏輯電路開始,最終構造一個簡易版的CPU實物

2021-11-06 09:20:58 16

16 首先應該明確鎖存器和觸發器也是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合電路的特性。 組合電路就是一個真值表,一個函數,一組輸入對應

2021-08-12 10:26:12 3567

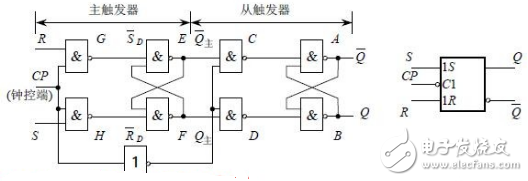

3567 D融發器工作原理及過程說明: SD和RD接至基本RS觸發器的輸入端,它們分別是預置和清零端,低電平有效。 ? ? ? ?當SD=0且RD=1時,不論輸入端D為何種狀態,都會使Q=1,Q非=0,即

2021-08-09 23:17:49 7277

7277 均無效(高電平式)時,符合建立時間要求的D數據在CP上升沿作用下傳送到輸出端。 74ls74雙d觸發器引腳圖 在ttl電路中,比較典型的d觸發器電路有74ls74。74ls74是一個邊沿觸發器數字電路器件,每個器件中包含兩個相同的、相互獨立的邊沿觸發d觸發器電路模塊

2021-06-04 15:40:41 63776

63776

,鎖存器有兩個輸入,一個是有效信號EN,一個是輸入數據信號DATA_IN,有一個輸出Q,它的功能就是在EN有效的時候把DATA_IN的值傳給Q,也就是鎖存的過程。 2)觸發器 觸發器(Flip-Flop,簡寫為FF)也叫雙穩態門,又稱雙穩態觸發器,是一種可以在兩種

2020-11-29 11:02:11 20662

20662 文章都對鎖存器有個誤解,我們后面會詳細說明。 這篇文章,我們包含如下內容: ①鎖存器、觸發器和寄存器的原理和區別,為什么鎖存器不好? ② 什么樣的代碼會產生鎖存器? ③ 為什么鎖存器依然存在于FPGA中? 鎖存器、觸發器和寄存器的原理和區別,為什么鎖存器

2020-11-16 11:42:00 7206

7206

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2019-11-08 14:48:44 79654

79654

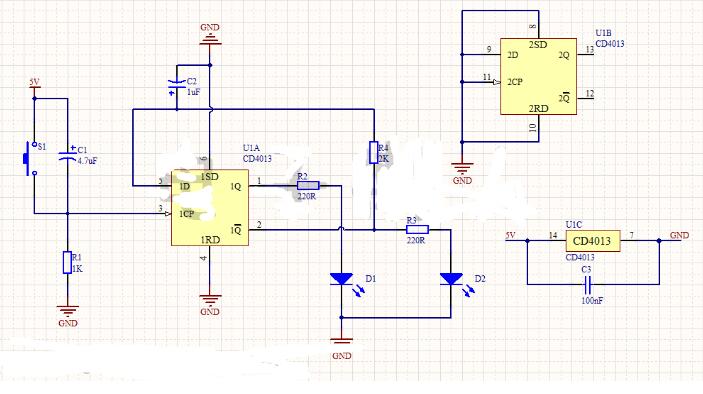

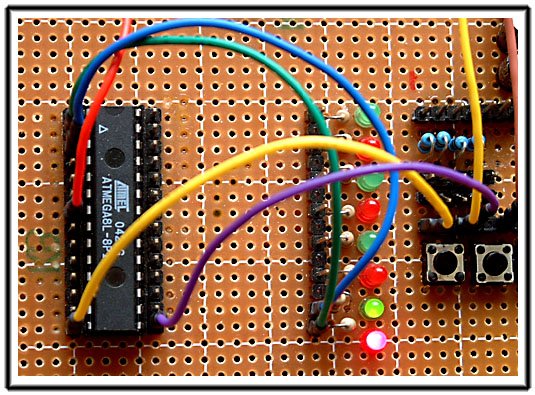

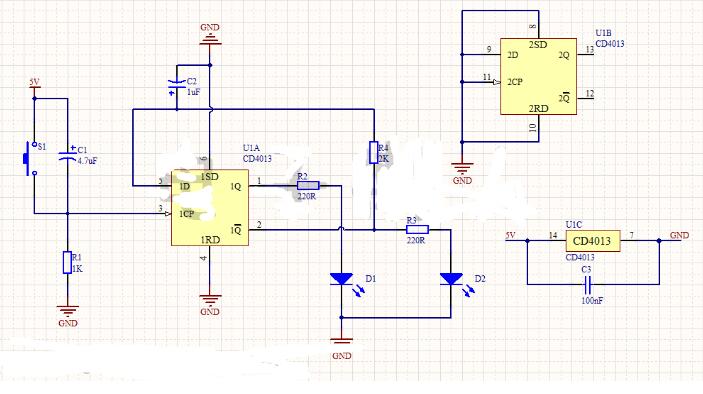

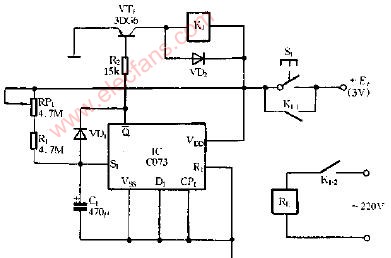

所謂自鎖開關就是按一下,開關接通并保持接通狀態;再按一下,開關解鎖復位到初始狀態。本例通過D觸發器而設計的電子自鎖開關,當每按一下電路中的輕觸按鍵S1時,都可以使D觸發器翻轉一次,同時利用CD4013的特性,按鍵松開后電路仍然保持自鎖狀態。

2019-10-01 11:03:00 16749

16749

鎖存器(有時也稱為S/R鎖存器)是最小的存儲器塊。它們可以使用兩個NOR邏輯門(S和R為高電平有效)或兩個NAND門(輸入為低電平有效)構建,并用于構建更復雜的鎖存器和觸發器。

2019-07-30 11:23:28 5658

5658

CP=1時,門。。打開,門。。被封鎖,從觸發器保持原來狀態不變,D信號進入主觸發器。但是要特別注意,這時主觸發器只跟隨而不鎖存,即。。跟隨D變化,D怎么變。。也隨之怎么變。

2019-07-15 08:57:32 42337

42337

數字時序電路中通常用到的觸發器有三種:電平觸發器、脈沖觸發器和邊沿觸發器。

2019-07-05 14:38:54 12670

12670

D型觸發器是一個改進的置位復位觸發器,增加了一個反相器,由此可見以防止S和R輸入處于相同的邏輯電平,此狀態將強制兩個輸出都處于邏輯“1”,超越反饋鎖存動作,無論哪個輸入先進入邏輯電平“1”都將失去控制,而另一個仍處于邏輯“0”的輸入控制鎖存器的結果狀態。

2019-06-26 15:36:28 14537

14537

本文檔的主要內容詳細介紹的是數字電路教程之觸發器課件的詳細資料說明主要內容包括了:一 SR鎖存器,二 電平觸發的觸發器,三 脈沖觸發的觸發器,四 邊沿觸發的觸發器,五 觸發器的邏輯功能及其描述方法

2018-12-28 08:00:00 17

17 本文首先介紹了鎖存器Latch結構和鎖存器latch的優缺點,其次介紹了觸發器Flip-flop的結構與優缺點,最后介紹了鎖存器Latch和觸發器Flip-flop兩者之間的區別。

2018-04-18 14:10:10 128942

128942

K觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2018-02-08 14:36:43 48950

48950

鎖存器就是把單片機的輸出的數據先存起來,可以讓單片機繼續做其它事。它的LE為高的時候,數據就可以通過它。當為低時,它的輸出端就會被鎖定RS觸發器是構成其它各種功能觸發器的基本組成部分。又稱為基本RS觸發器。

2018-01-31 14:48:13 28618

28618

JK觸發器是數字電路觸發器中的一種基本電路單元。JK觸發器具有置0、置1、保持和翻轉功能,在各類集成觸發器中,JK觸發器的功能最為齊全。在實際應用中,它不僅有很強的通用性,而且能靈活地轉換其他類型的觸發器。由JK觸發器可以構成D觸發器和T觸發器。

2017-12-25 17:30:03 172587

172587

鐘脈沖極性控制。CD4042內部為四個主從結構的D觸發器。當POL=O時,鎖存器在CP的低電平期間開通,D0~D3的數據分別傳送到Q0~Q3端,當CP的上升沿來到時數據被鎖存,所以這時鎖存的是CP上升沿來到前

2017-11-24 09:52:50 45919

45919

鎖存器(latch)---對脈沖電平敏感,在時鐘脈沖的電平作用下改變狀態 鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,僅當鎖存器處于使能狀態時,輸出才會隨著數據輸入發生變化。

2017-11-02 09:24:41 92855

92855

所謂鎖存器,就是輸出端的狀態不會隨輸入端的狀態變化而變化,僅在有鎖存信號時輸入的狀態被保存到輸出,直到下一個鎖存信號到來時才改變。典型的鎖存器邏輯電路是 D 觸發器電路。 PS:鎖存信號(即對LE賦高電平時Data端的輸入信號)。鎖存,就是把信號暫存以維持某種電平狀態。

2017-10-30 14:35:53 58733

58733

一種單鎖存器CMOS三值D型邊沿觸發器設計

2017-01-17 19:54:24 22

22 數字電路--若干種觸發器工作原理

2017-01-07 21:08:03 10

10 數字電路--觸發器原理

2016-12-29 19:03:12 11

11 數字電路--觸發器雙穩態觸發器

2016-12-20 17:32:40 14

14 圖中所示是用J-K觸發器組成的D觸發器電路。

從J-K觸發器的邏輯圖已知在D觸發器端增

2010-09-24 00:21:27 5729

5729

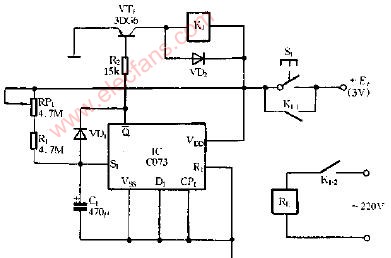

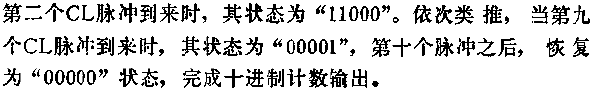

圖中所示是用CMOS電路D觸發器組成的十進制環形計數器.圖中先將D觸發器拼成移位寄存器,然后把最后一級D觸發器

2010-09-20 23:46:58 17359

17359

圖中所示是用CMOS電路D觸發器組成T型觸發器和J-K觸發器線路。圖示線路將D觸發器的Q端與D端相連,就可組成T

2010-09-20 03:31:35 15895

15895 1、掌握鎖存器、觸發器的電路結構和工作原理;

2、熟練掌握SR觸發器、JK觸發器、D觸發器及T 觸發器的邏輯功能;

3、正確理解鎖存器、觸發器的動態特性

2010-08-18 16:39:35 233

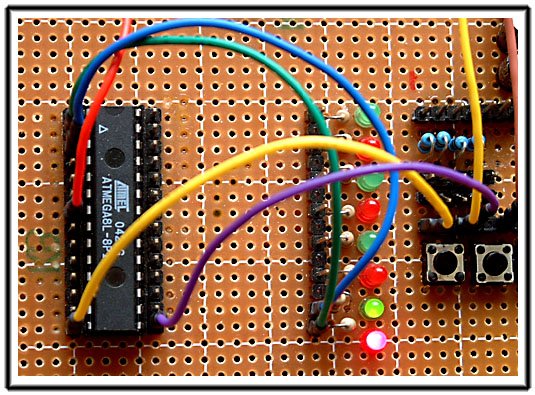

233 8路鍵盤D觸發鎖存器的制作

實現目的:

當管腳設定為輸入時,了解如何可以編程設定上拉電阻,以達到簡化硬件的目的。

2010-05-12 10:06:48 1016

1016

觸發器的分類, 觸發器的電路

雙穩態器件有兩類:一類是觸發器,一類是鎖存器。鎖存器是觸發器的原始形式。基本

2010-03-09 09:59:59 1491

1491 鎖存器,鎖存器是什么意思

鎖存器定義一位鐘控D觸發器只能傳送或存儲一位二進制數據,而在實際工作中往往是一次傳送或存

2010-03-09 09:44:12 11794

11794 D觸發器工作原理是什么?

邊沿D 觸發器:

負跳沿觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高電平期間輸入端出

2010-03-08 13:56:50 68940

68940

D觸發器,D觸發器是什么意思

邊沿D 觸發器: 電平觸發的主從觸發器工作時,必須在正跳沿前加入輸入信號。如果在CP 高

2010-03-08 13:53:13 4130

4130 40174 CMOS 六D觸發器:

2009-08-08 11:32:28 46

46 D觸發器實現二分頻電路(D觸發器構成的2分頻電路)&

2009-06-12 13:58:56 73460

73460

D觸發器的制作及電路圖

2009-05-19 09:35:49 33

33

D觸發器構成的定時電路圖

2009-05-08 15:15:26 3107

3107

D觸發器電路圖

2009-05-08 14:26:44 3484

3484

D觸發器的功能測試74LS74型雙D觸發器芯片引腳圖,D觸發器功能測試的引腳連線圖,D觸發器功能測試的引腳連線圖,用D觸發器構成二進制計數器,用D觸發器構成四位移位寄存器

J-K

2009-02-14 15:27:51 290

290 同步式D觸發器邏輯電路圖

2008-10-20 09:58:19 7678

7678

D觸發器

同步式D觸發器邏輯電路圖

D觸發器功能

2008-10-20 09:57:54 1846

1846

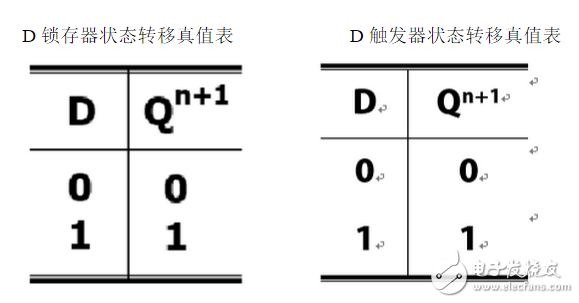

D觸發器真值表分析:

1. D 觸發器真值表

Dn

2007-09-11 23:15:20 17600

17600 CD4013 雙D觸發器 *CD4027 雙JK觸發器 *CD4042 四鎖存D型觸發器 *CD4043

2006-04-17 21:18:32 3219

3219

電子發燒友App

電子發燒友App

評論