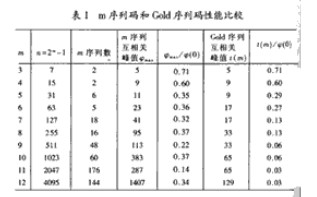

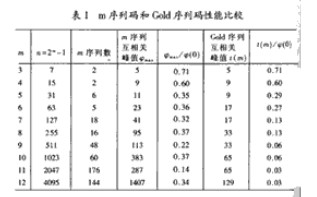

本文介紹一種基于現(xiàn)場(chǎng)可編程門陣列(FPGA)的通信系統(tǒng)同步提取方案的實(shí)現(xiàn)。本文只介紹了M序列碼作為同步頭的實(shí)現(xiàn)方案,對(duì)于m序列碼作為同步頭的實(shí)現(xiàn),只要稍微做一下修改,即加一些相應(yīng)的延時(shí)單元就可以實(shí)現(xiàn)。

2013-04-11 10:53:23 3829

3829

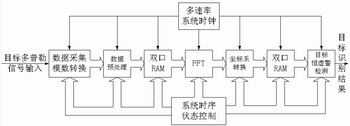

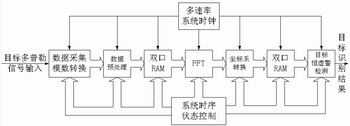

為了實(shí)現(xiàn)激光-水聲淺海地形遙感探測(cè)中水聲信號(hào)的實(shí)時(shí)解調(diào)與處理,本文提出了一種基于FPGA的激光多普勒測(cè)振計(jì)信號(hào)采集與處理系統(tǒng)的設(shè)計(jì)方案。以Cyclone Ⅱ系列FPGA為核心控制模塊,結(jié)合

2013-10-29 10:10:02 2157

2157

本文主要詳解基于FPGA的模糊PID控制器的設(shè)計(jì)實(shí)現(xiàn),首先介紹了FPGA工作原理、基本特點(diǎn)以及FPGA的優(yōu)勢(shì),其次闡述了使用Altera的FPGA設(shè)計(jì)實(shí)現(xiàn)的數(shù)字模糊PID控制器,具體的跟隨小編一起來(lái)了解一下。

2018-06-01 09:26:51 15747

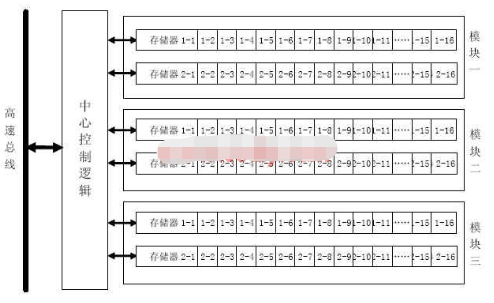

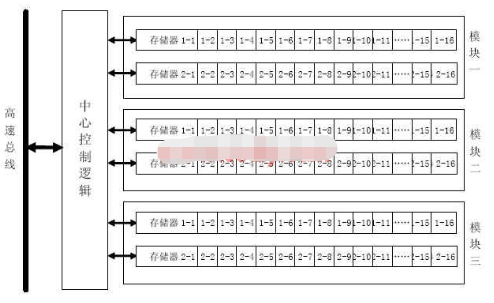

15747 本文介紹了一種以FPGA作為控制器,F(xiàn)LASH MEMORY作為主存儲(chǔ)器的大容量高速存儲(chǔ)系統(tǒng)方案,并對(duì)關(guān)鍵技術(shù)及實(shí)現(xiàn)途徑進(jìn)行了論述,在存儲(chǔ)容量及存儲(chǔ)速度上實(shí)現(xiàn)了突破。

2020-07-30 17:53:54 1917

1917

本帖最后由 mr.pengyongche 于 2013-4-30 02:57 編輯

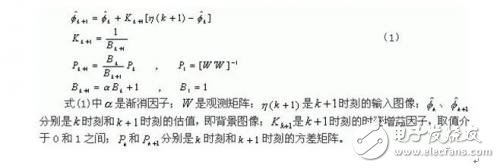

FPGA+DSP 在空中背景下運(yùn)動(dòng)目標(biāo)實(shí)時(shí)跟蹤系統(tǒng)中的應(yīng)用 摘要:針對(duì)電視跟蹤系統(tǒng)對(duì)飛行目標(biāo)的檢測(cè)與跟蹤受到速度瓶頸

2012-12-28 11:19:07

提高競(jìng)爭(zhēng)力,嵌入式系統(tǒng)開(kāi)發(fā)人員需要一種能夠幫助他們開(kāi)發(fā)獨(dú)具優(yōu)勢(shì)產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-14 08:00:00

1 SPARTAN-6 從并加載流程3]4]5 結(jié)束語(yǔ)使用基于CPLD 的FPGA 從并加載方案,相對(duì)于其它幾種加載方式,雖然加載管腳增多,但加載時(shí)間大大縮短,并且如果提高CPU 局部總線的寫速度,加載速度有進(jìn)一步提高空間,滿足通信系統(tǒng)快速啟動(dòng)的要求,具有很高的實(shí)用價(jià)值。

2019-06-14 06:00:00

架構(gòu)、嵌入式系統(tǒng)、實(shí)時(shí)操作系統(tǒng)、數(shù)字信號(hào)處理、圖像與視頻處理和數(shù)字通信等,可以實(shí)現(xiàn)片上課程理念。七、教學(xué)大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的課程安排如下: 第一天 課程目標(biāo)

2009-07-21 09:22:42

完成CF卡的讀寫,上位機(jī)軟件生成專用的ACE文件并下載到CF存儲(chǔ)卡中,上電后通過(guò)ACE控制芯片實(shí)現(xiàn)不同配置碼流間的切換。System ACE的解決方案需要購(gòu)買CF存儲(chǔ)卡和專用的ACE控制芯片,增加了系統(tǒng)

2019-06-10 05:00:08

。通過(guò)遵循推薦的電源序列,可以避免在啟動(dòng)期間吸取過(guò)大的電流,這反過(guò)來(lái)又可防止器件受損。對(duì)一個(gè)系統(tǒng)中的電源進(jìn)行排序可采用多種方法來(lái)完成。本文將詳細(xì)說(shuō)明可根據(jù)系統(tǒng)所要求的復(fù)雜程度來(lái)實(shí)現(xiàn)的電源排序解決方案

2019-06-10 08:30:00

詳解賽靈思All Programmable Smarter Vision解決方案

2021-06-02 06:56:12

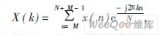

本文主要介紹各部分的算法方案及電路實(shí)現(xiàn)時(shí)所用的FPGA元件的基本結(jié)構(gòu)、設(shè)計(jì)思路。最后通過(guò)對(duì)電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿足多載波傳輸系統(tǒng)的同步要求。

2021-05-07 06:52:34

ROCm移動(dòng)WLAN解決方案詳解

2021-06-01 06:34:35

系統(tǒng)的角度出發(fā),把處理機(jī)制、模型算法、芯片結(jié)構(gòu)、各層次電路,直至器件的實(shí)際電路緊密連接起來(lái),在單個(gè)(少數(shù)幾個(gè))芯片上實(shí)現(xiàn)整個(gè)系統(tǒng)的功能。同時(shí)隨著現(xiàn)場(chǎng)可編程邏輯陣列(FPGA)技術(shù)的日益成熟,將PLD

2019-07-29 06:58:24

CY7C68013A-128AXC、FPGA芯片EP1C6Q240C8和SDRAM芯片IS61LV25616AL-10T共同組合完成,實(shí)現(xiàn)USB2.0的高速傳輸。本USB+FPGA開(kāi)發(fā)板的實(shí)際傳輸速度

2010-03-25 16:01:56

架構(gòu)、嵌入式系統(tǒng)、實(shí)時(shí)操作系統(tǒng)、數(shù)字信號(hào)處理、圖像與視頻處理和數(shù)字通信等,可以實(shí)現(xiàn)片上課程理念。七、教學(xué)大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的課程安排如下:第一天 課程目標(biāo)

2009-07-21 09:20:11

架構(gòu)、嵌入式系統(tǒng)、實(shí)時(shí)操作系統(tǒng)、數(shù)字信號(hào)處理、圖像與視頻處理和數(shù)字通信等,可以實(shí)現(xiàn)片上課程理念。七、教學(xué)大綱基于Xilinx FPGA的DSP系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的課程安排如下:第一天 課程目標(biāo)

2009-07-24 13:07:08

利用fpga開(kāi)發(fā)板設(shè)計(jì)mips32 cpu以及外圍控制邏輯(如uart、vga等),構(gòu)建一個(gè)完整的片上系統(tǒng),然后在此基礎(chǔ)上開(kāi)發(fā)bootloader和演示軟件,完成整個(gè)系統(tǒng)平臺(tái)。該方案只是試驗(yàn)版,作為

2012-07-31 14:25:10

、方案要點(diǎn)(1)圖像數(shù)據(jù)采集通過(guò)可編程邏輯器件(例如FPGA)進(jìn)行高速、高精度的圖像數(shù)據(jù)采集,且可靈活接入各種攝像頭,如CameraLink、SDI、PAL等。(2)目標(biāo)追蹤分析將采集得到的圖像數(shù)據(jù)通

2021-05-19 17:10:50

項(xiàng)目名稱:基于深度學(xué)習(xí)的目標(biāo)檢測(cè)系統(tǒng)設(shè)計(jì)試用計(jì)劃:嘗試在硬件平臺(tái)實(shí)現(xiàn)對(duì)Yolo卷積神經(jīng)網(wǎng)絡(luò)的加速運(yùn)算,期望提出的方法能夠使目標(biāo)檢測(cè)技術(shù)更便捷,運(yùn)用領(lǐng)域更廣泛。針對(duì)課題的研究一是研究基于開(kāi)發(fā)板低功耗

2020-09-25 10:11:49

特點(diǎn),采用數(shù)據(jù)流控制的方法實(shí)現(xiàn)了信息的并行處理,可以更加有效的實(shí)現(xiàn)多通道振動(dòng)信號(hào)采集;同時(shí)為了提高數(shù)據(jù)的可靠性采用時(shí)間標(biāo)定的方法進(jìn)行數(shù)據(jù)的存儲(chǔ)和校驗(yàn)。本文第一節(jié)介紹了該系統(tǒng)的整體設(shè)計(jì)方案,第二節(jié)

2019-07-01 06:11:15

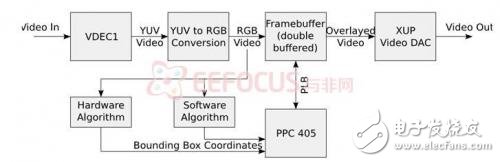

完成主要部分設(shè)計(jì)的。2 機(jī)器視覺(jué)系統(tǒng)設(shè)計(jì)2.1 設(shè)計(jì)原理系統(tǒng)原理框圖如圖1所示。這個(gè)解決方案基于Xilinx低功耗低成本的Spartan 3E FPGA芯片上實(shí)現(xiàn),它提供了整合CameraLink

2019-05-05 08:30:00

用的天網(wǎng)系統(tǒng)等都可以應(yīng)用本項(xiàng)目的設(shè)計(jì),加速目 標(biāo)檢測(cè)算法的運(yùn)算速度以及降低系統(tǒng)的功耗。

在本次項(xiàng)目的設(shè)計(jì)開(kāi)發(fā)過(guò)程中,我們參考 DAC 2019 低功耗目標(biāo)檢測(cè)系統(tǒng)設(shè)計(jì)挑戰(zhàn)賽

GPU、FPGA 組雙冠軍方案

2023-06-20 19:45:12

提高競(jìng)爭(zhēng)力,嵌入式系統(tǒng)開(kāi)發(fā)人員需要一種能夠幫助他們開(kāi)發(fā)獨(dú)具優(yōu)勢(shì)產(chǎn)品的解決方案,非常靈活,效率也非常高。基于FPGA的單芯片實(shí)現(xiàn)方法具有低成本和快速面市等優(yōu)點(diǎn),是多芯片和ASICSoC非常有吸引力的替代

2021-07-12 08:00:00

時(shí)間。針對(duì)上述研究現(xiàn)狀和分布式采集場(chǎng)景分析,本文介紹了一種基于FPGA和TOE架構(gòu),實(shí)現(xiàn)TCP/IP協(xié)議數(shù)據(jù)傳輸?shù)亩嗦凡杉c切換系統(tǒng)。該系統(tǒng)涉及并行數(shù)據(jù)采集、多路通道切換、TCP/IP協(xié)議通信等模塊

2021-07-12 08:30:00

,基于ARINC664規(guī)范第7部分,提出符合該規(guī)范的基于FPGA的AFDX端系統(tǒng)協(xié)議芯片和相應(yīng)AFDX端系統(tǒng)板卡的設(shè)計(jì)方案,并給出關(guān)鍵模塊的具體實(shí)現(xiàn);通過(guò)對(duì)端系統(tǒng)協(xié)議芯片進(jìn)行測(cè)試驗(yàn)證,證明該端系統(tǒng)協(xié)議芯片

2010-05-13 09:09:08

證過(guò)的網(wǎng)絡(luò)BSD編程實(shí)例;另外,也可提供利用DM9000A實(shí)現(xiàn)的FPGA以太網(wǎng)傳輸系統(tǒng)整套硬件和軟件解決方案。該方案不占用FPGA內(nèi)部邏輯資源,但性能與前述方案相比會(huì)降低。上述介紹完畢,如果您的項(xiàng)目

2014-06-19 12:04:25

證過(guò)的網(wǎng)絡(luò)BSD編程實(shí)例;另外,也可提供利用DM9000A實(shí)現(xiàn)的FPGA以太網(wǎng)傳輸系統(tǒng)整套硬件和軟件解決方案。該方案不占用FPGA內(nèi)部邏輯資源,但性能與前述方案相比會(huì)降低。上述介紹完畢,如果您的項(xiàng)目

2014-06-19 12:06:43

,其他部分不需要。本設(shè)計(jì)基于FPGA實(shí)現(xiàn),邏輯宏單元不能高于80%。

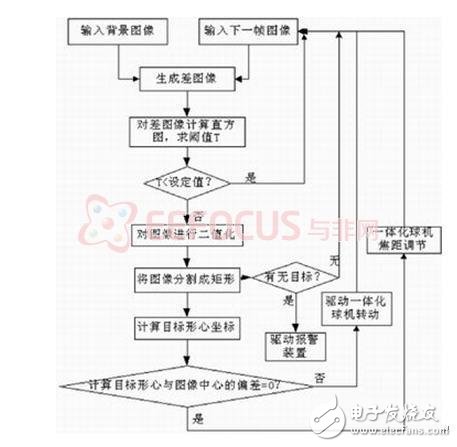

3.2 方案論證

備選方案:

方案一:基于顏色的攝像頭定位系統(tǒng)設(shè)計(jì)

方案二:基于幀差法的攝像頭定位系統(tǒng)設(shè)計(jì)

方案三:基于背景差法

2023-06-27 20:42:56

像素點(diǎn)賦予一個(gè)速度矢量的方法建立光流場(chǎng),利用光流場(chǎng)中矢量運(yùn)動(dòng)的連續(xù)性來(lái)檢測(cè)移動(dòng)目標(biāo)。該方法的計(jì)算量通常很大,難以實(shí)現(xiàn)實(shí)時(shí)性的檢測(cè)。2 FPGA實(shí)現(xiàn)本節(jié)實(shí)驗(yàn)將實(shí)現(xiàn)對(duì)鏡頭內(nèi)移動(dòng)物體(無(wú)論變大變小左右

2018-08-10 09:15:05

、野外試驗(yàn)以及生產(chǎn)應(yīng)用,證明結(jié)合FPGA技術(shù),時(shí)鐘恢復(fù)和系統(tǒng)同步技術(shù)在地震勘探儀器中具有獨(dú)到的優(yōu)勢(shì),其精度可達(dá)us級(jí),而且穩(wěn)定,實(shí)現(xiàn)方便。地震勘探儀器是一個(gè)高度集成的網(wǎng)絡(luò)采集系統(tǒng),在這些地震勘探儀器中

2019-06-18 08:15:35

信號(hào)并輸出。利用DSP/FPGA的高速計(jì)算性能、直接數(shù)字合成(DDS)技術(shù)和數(shù)字射頻存儲(chǔ)(DRFM)技術(shù),可以實(shí)現(xiàn)相位編碼、線性調(diào)頻、非線性調(diào)頻等多種復(fù)雜方式下的目標(biāo)回波信號(hào)的實(shí)時(shí)模擬,檢測(cè)雷達(dá)的跟蹤

2019-06-03 05:00:08

會(huì)受一定的影響。?本文所提出的基于DSP+FPGA的控制系統(tǒng)方案,利用FPGA的容量大、可編程實(shí)現(xiàn)很多功能,結(jié)合DSP具有高速的信息處理能力的特點(diǎn),使得本控制系統(tǒng)非常簡(jiǎn)潔,結(jié)構(gòu)靈活,通用性強(qiáng),系統(tǒng)也易于維護(hù)和擴(kuò)展。該方案基于軟件無(wú)線電的思想,是采用通用平臺(tái)的設(shè)計(jì)。?

2019-07-29 06:08:47

為了實(shí)現(xiàn)—是彈武器瞄準(zhǔn)自動(dòng)化,本文設(shè)計(jì)了基于DSP和FPGA的高速高精確度雙通道CCD圖像采集系統(tǒng),采用QUartuBn在AJtera的FPGA器件CYCLONEII上設(shè)計(jì)了CCD驅(qū)動(dòng)時(shí)序電路,采用

2014-11-07 14:54:07

目標(biāo)跟蹤算法作為一種有著非常廣泛的應(yīng)用的算法,在航空航天、智能交通、智能設(shè)備等領(lǐng)域有著非常廣泛的應(yīng)用。本系列博客將教大家在410c開(kāi)發(fā)板上基于linux操作系統(tǒng)環(huán)境,采用QT+Opencv來(lái)實(shí)現(xiàn)

2018-09-21 10:42:31

安捷倫公司數(shù)字測(cè)試資深技術(shù)/市場(chǎng)工程師 冀衛(wèi)東為滿足日益復(fù)雜的數(shù)字化系統(tǒng)的設(shè)計(jì)要求,FPGA的密度及復(fù)雜性也在急速增長(zhǎng),越來(lái)越多的系統(tǒng)或子系統(tǒng)功能在FPGA內(nèi)部實(shí)現(xiàn),其先進(jìn)的功能和高集成度使FPGA成為極具吸引力的解決方案,進(jìn)而也使得基于內(nèi)核的FPGA測(cè)試方案浮出水面。

2019-07-11 06:15:12

大家下午好,我計(jì)劃使用主fpga板的IO引腳配置目標(biāo)cpld板,即菊花鏈。我使用主fpga板的IO引腳連接cpld的JTAG頭。如何編程master fpga的IO引腳來(lái)配置目標(biāo)cpld?請(qǐng)發(fā)送與此相關(guān)的任何文件....謝謝問(wèn)候Vimala

2020-03-24 06:43:09

本文介紹了采用Xilinx公司的Spartan-3 FPGA實(shí)現(xiàn)通用視頻采集系統(tǒng)的設(shè)計(jì)方案。

2021-06-08 06:34:30

怎么實(shí)現(xiàn)SoPC目標(biāo)板Flash編程設(shè)計(jì)的創(chuàng)建?目標(biāo)板Flash編程設(shè)計(jì)在實(shí)際Flash編程中的應(yīng)用

2021-04-30 07:06:11

要畢業(yè)了,畢設(shè)是完全沒(méi)學(xué)過(guò)的FPGA課題,求助各位大哥幫幫忙,要求:了解并掌握LFMCW雷達(dá)的工作原理、用途及優(yōu)缺點(diǎn);了解常用的雷達(dá)目標(biāo)檢測(cè)方法,選取其中一種完成其Verilog實(shí)現(xiàn),并用FPGA

2018-04-08 23:48:36

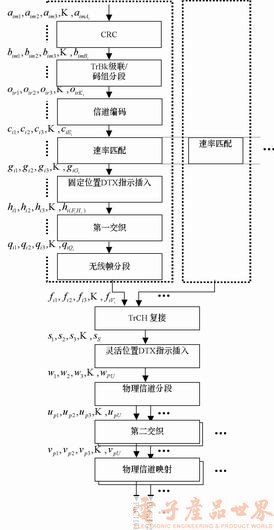

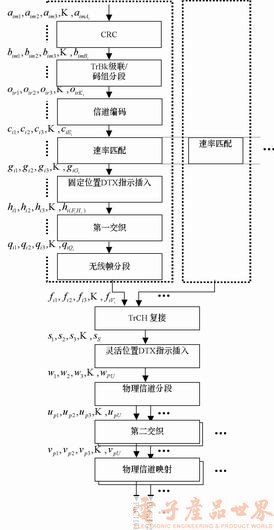

本文首先介紹WCDMA系統(tǒng)的無(wú)線信道的基帶發(fā)送方案,說(shuō)明其對(duì)多媒體業(yè)務(wù)的支持以及實(shí)現(xiàn)的復(fù)雜性。然后,從硬件實(shí)現(xiàn)角度,進(jìn)行了DSP和FPGA的性能比較,提出DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案,并以基站分系統(tǒng)(BTS)的發(fā)送單元為例,具體給出了該實(shí)現(xiàn)方案在下行無(wú)線信道基帶發(fā)送單元中的應(yīng)用。

2021-05-06 07:40:39

與PCB設(shè)計(jì)手機(jī)PCB可靠性的設(shè)計(jì)方案詳解RF與數(shù)模電路的PCB設(shè)計(jì)RF電路及其音頻電路PCB設(shè)計(jì)方案簡(jiǎn)述集成系統(tǒng)PCB板設(shè)計(jì)的新技術(shù)詳解在PCB設(shè)計(jì)中采用時(shí)間交替超高速模數(shù)轉(zhuǎn)換器完整的PCB設(shè)計(jì)系統(tǒng)

2014-12-16 13:55:37

電源解決方案 那么,如何才能簡(jiǎn)化設(shè)計(jì)呢?幸運(yùn)的是,有多種解決方案都有助于實(shí)現(xiàn)簡(jiǎn)化。在本文中,我將重點(diǎn)介紹兩種能夠幫助您快速便捷地實(shí)現(xiàn)設(shè)計(jì)目標(biāo)的創(chuàng)新技術(shù)…

2022-11-23 07:14:47

紅芯FPGA開(kāi)發(fā)板例程詳解

2013-07-28 20:25:33

實(shí)現(xiàn)技術(shù)是使用SRAM配置單元。同樣,我們會(huì)在以后的文章中討論更多的細(xì)節(jié)。這里我們所要知道的僅是當(dāng)電路板第一次上電時(shí),基于SRAM的FPGA會(huì)加載配置信息(我們可以把這個(gè)過(guò)程想像為器件的編程)。作為

2017-09-26 15:13:48

系統(tǒng)工程經(jīng)行綜合與布局布線,通過(guò)Modelsim進(jìn)行功能與時(shí)序仿真,并后將配置文件下載到FPGA中以實(shí)現(xiàn)目標(biāo)利用FPGA對(duì)圖像進(jìn)行運(yùn)動(dòng)目標(biāo)跟蹤算法處理 采用Verilog HDL語(yǔ)言編寫

2016-05-10 15:36:09

基于雙DSP的運(yùn)動(dòng)目標(biāo)智能跟蹤系統(tǒng)是怎樣設(shè)計(jì)并實(shí)現(xiàn)的?

2021-04-27 06:59:18

針對(duì)遙感系統(tǒng)的工作環(huán)境特點(diǎn)、待處理信號(hào)的頻譜特征以及系統(tǒng)信噪比等要求,綜合比較多種信號(hào)采集系統(tǒng)方案的優(yōu)缺點(diǎn),本文提出了一種基于FPGA的激光多普勒測(cè)振計(jì)信號(hào)采集與處理系統(tǒng)的設(shè)計(jì)方案,該方案可以實(shí)現(xiàn)光

2019-06-24 07:16:30

SoC面臨的挑戰(zhàn)是什么采用FPGA方案進(jìn)行數(shù)字顯示系統(tǒng)設(shè)計(jì)有什么特性?

2021-04-29 06:24:26

。為了更進(jìn)一步擴(kuò)大同一時(shí)間實(shí)時(shí)監(jiān)控范圍,本文介紹的傘降-目標(biāo)跟蹤系統(tǒng)通過(guò)同步控制器控制微秒級(jí)外部時(shí)鐘同步、子系統(tǒng)測(cè)試形變等手段,將多個(gè)單一的高速相機(jī)系統(tǒng)視場(chǎng)進(jìn)行視場(chǎng)拼接,從而將視場(chǎng)放大至單一系統(tǒng)的數(shù)倍,實(shí)現(xiàn)大視場(chǎng)

2016-04-07 15:14:38

減壓活門性能試驗(yàn)臺(tái)系統(tǒng)方案設(shè)計(jì):主要介紹了減壓活門性能試驗(yàn)臺(tái)的實(shí)現(xiàn)機(jī)理、采用的方案。關(guān)鍵詞* 工控機(jī); 位置傳感器; 載荷傳感器; 智能計(jì)數(shù)器; 液壓伺服系統(tǒng); +,

2009-06-06 17:53:05 23

23 本文介紹了一種基于FPGA 的圖像目標(biāo)發(fā)生器的設(shè)計(jì)方法,介紹了它的設(shè)計(jì)原理、硬件電路結(jié)構(gòu)、各功能的實(shí)現(xiàn)方法。該圖像發(fā)生器能產(chǎn)生灰度階圖像、靜態(tài)目標(biāo)圖像和運(yùn)動(dòng)目標(biāo)

2009-09-02 11:16:55 27

27 斑梨電子FPGA CycloneII EP2C5T144 學(xué)習(xí)板 開(kāi)發(fā)板產(chǎn)品參數(shù)1. 采用ALTERA公司的CyclonellEP2C5T144芯片作為核心最小系統(tǒng),將FPGA

2023-02-03 15:14:29

基于ARM和FPGA的圓網(wǎng)印花機(jī)控制器的實(shí)現(xiàn):根據(jù)傳統(tǒng)圓網(wǎng)印花機(jī)的結(jié)構(gòu)以及存在的問(wèn)題。提出了基于ARNi和FPGA的嵌入式圓網(wǎng)印花機(jī)控制器的設(shè)計(jì)方案。并開(kāi)發(fā)了試驗(yàn)樣機(jī)系統(tǒng)。充分利用

2009-11-20 17:43:36 12

12 闡述了在引信虛擬樣機(jī)建模、虛擬目標(biāo)建模和虛擬環(huán)境建模基礎(chǔ)上所進(jìn)行的虛擬試驗(yàn)系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)的技術(shù)途徑和方法,論述了機(jī)電引信虛擬試驗(yàn)系統(tǒng)的功能模塊,提出了其系統(tǒng)構(gòu)

2009-12-19 14:02:27 13

13 一種基于FPGA的洗片機(jī)控制系統(tǒng)的設(shè)計(jì),給出了系統(tǒng)的工作原理與設(shè)計(jì)方案,重點(diǎn)論述了FPGA在系統(tǒng)中應(yīng)用與具體實(shí)現(xiàn)。該系統(tǒng)實(shí)現(xiàn)了在0℃~50℃范圍內(nèi)精度0.1℃的測(cè)量與控制。相

2009-12-23 15:29:54 19

19 摘 要: 本文在闡述某種近距雷達(dá)目標(biāo)檢測(cè)原理和FPGA技術(shù)發(fā)展?fàn)顩r的基礎(chǔ)上,著重討論用FPGA設(shè)計(jì)高性能的數(shù)字信號(hào)處理系統(tǒng)的方法,并給出一個(gè)應(yīng)用實(shí)例。

2006-03-11 13:16:43 1698

1698

摘? 要: 本文在分析WCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,結(jié)合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價(jià)比上都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 引言 隨

2006-03-11 13:29:42 670

670

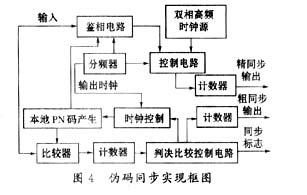

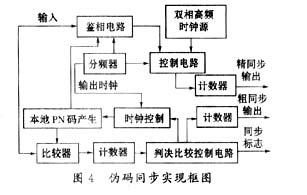

【摘 要】 介紹了基于偽碼測(cè)距的某定位系統(tǒng)的設(shè)計(jì)方案,簡(jiǎn)要分析了偽碼測(cè)距的原理,研究了用FPGA實(shí)現(xiàn)偽碼的捕獲與跟蹤的方法。

2009-05-14 20:58:06 720

720

服務(wù)器集群系統(tǒng)實(shí)現(xiàn)方案詳解

一、集群的基本概念

有一種常見(jiàn)的方法可以大幅提高服務(wù)器的安全性,這就是集

2010-01-27 17:03:17 640

640 摘要:本文在分析TD-SCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,提出了一種在性能、靈活性和性價(jià)比方面都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 關(guān)鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

2011-03-02 01:38:41 60

60 為了解決空間目標(biāo)與航天器發(fā)生碰撞的問(wèn)題,設(shè)計(jì)了一種基于FPGA,以在軌目標(biāo)三維坐標(biāo)為待處理數(shù)據(jù)進(jìn)行快速并行處理的目標(biāo)碰撞預(yù)警系統(tǒng)。該系統(tǒng)基于Xilinx 公司FPGA芯片中的內(nèi)容可尋址存儲(chǔ)器(Content Addressable Memory,CAM) IP核和MicroBlaze軟核控制器,

2011-03-07 15:29:58 43

43 該文提出了一種FPGA 可實(shí)現(xiàn)的跳頻MSK 信號(hào)實(shí)時(shí)截獲和識(shí)別的設(shè)計(jì)方案,經(jīng)過(guò)試驗(yàn)證明,可以對(duì)寬帶跳頻信號(hào)進(jìn)行實(shí)時(shí)的截獲,并能夠?qū)ζ渲械腗SK 目標(biāo)信號(hào)完成準(zhǔn)確識(shí)別,可應(yīng)用于針對(duì)特

2011-06-08 11:48:00 3540

3540

本文將著重介紹運(yùn)用FPGA技術(shù)實(shí)現(xiàn)基群與二次群之間復(fù)接與分接系統(tǒng)的總體設(shè)計(jì)方案。

2011-08-15 17:00:27 1299

1299 現(xiàn)場(chǎng)可編程門陣列(FPGA)是在專用ASIC的基礎(chǔ)上發(fā)展出來(lái)的,它克服了專用ASIC不夠靈活的缺點(diǎn).本文介紹的就是一種可以應(yīng)用于軍事偵察的紅外動(dòng)目標(biāo)識(shí)別跟蹤系統(tǒng)的設(shè)計(jì)。

2011-09-16 11:00:16 1214

1214

賽靈思(Xilinx)推出首款鎖定28奈米7系列現(xiàn)場(chǎng)可編程邏輯閘陣列(FPGA)的目標(biāo)設(shè)計(jì)平臺(tái)方案,協(xié)助客戶加速其系統(tǒng)開(kāi)發(fā)與整合作業(yè)。

2012-02-06 09:25:41 476

476 為滿足雷達(dá)數(shù)據(jù)處理系統(tǒng)目標(biāo)跟蹤算法的測(cè)試需求,介紹了一種基于USB和FPGA技術(shù)的雷達(dá)目標(biāo)信號(hào)模擬器設(shè)計(jì)方案。文中重點(diǎn)討論了模擬器的結(jié)構(gòu)和目標(biāo)數(shù)據(jù)形成、傳輸、存儲(chǔ)、信號(hào)波形

2013-09-02 14:41:00 76

76 基于FPGA實(shí)現(xiàn)POWERlink的方案

2015-11-17 15:55:08 19

19 機(jī)器人捕捉運(yùn)動(dòng)目標(biāo)技術(shù)的研究電子論文!資料來(lái)源網(wǎng)絡(luò),如有侵權(quán),敬請(qǐng)見(jiàn)諒

2015-11-30 11:39:02 18

18 FPGA入門試驗(yàn)精品,有需要的下來(lái)看看啊

2016-05-10 11:24:05 27

27 FPGA實(shí)現(xiàn)嵌入式系統(tǒng),有需要的下來(lái)看看

2016-05-10 11:24:33 21

21 基于FPGA的多功能圖像目標(biāo)發(fā)生器的設(shè)計(jì)與實(shí)現(xiàn)

2016-08-30 15:10:14 6

6 紅外動(dòng)目標(biāo)識(shí)別跟蹤系統(tǒng)的實(shí)現(xiàn)方案

2017-01-12 22:13:34 24

24 本文針對(duì)由FPGA構(gòu)成的高速數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)處理能力弱的問(wèn)題,提出FPGA與單片機(jī)實(shí)現(xiàn)數(shù)據(jù)串行通信的解決方案。

2017-02-11 14:30:00 11246

11246 軟核進(jìn)行改進(jìn)以搭建起這個(gè)多核網(wǎng)絡(luò)。 這個(gè)目標(biāo)捕獲系統(tǒng)的圖像處理算法的硬件實(shí)現(xiàn)方式和多核軟件實(shí)現(xiàn)方式將在一個(gè)基于FPGA試驗(yàn)板上進(jìn)行比較。以此證明通過(guò)合理配置和編程多核軟件實(shí)現(xiàn)同樣很容易達(dá)到和硬件實(shí)現(xiàn)一樣的低功耗性能,并只有

2017-10-16 11:22:36 0

0 基于DSP運(yùn)動(dòng)目標(biāo)檢測(cè)系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

2017-10-19 14:16:47 9

9 本文檔內(nèi)容介紹了基于xilinxFPGA選型詳解,供參考查閱

2018-03-15 15:58:01 4

4 受限的缺點(diǎn);克服了VR設(shè)備常有的遮擋問(wèn)題,可以準(zhǔn)確實(shí)時(shí)地還原如下蹲、擁抱、扭打等動(dòng)作。此外,慣性式動(dòng)作捕捉系統(tǒng)還可以實(shí)現(xiàn)多目標(biāo)捕捉。

2018-05-25 17:40:07 17734

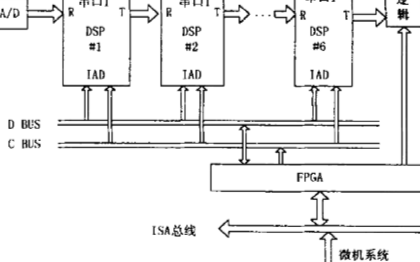

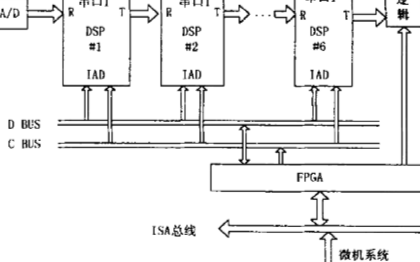

17734 通用多DSP 目標(biāo)系統(tǒng)的構(gòu)成由6片ADSP2181、2片A/D變換器以及實(shí)現(xiàn)邏輯功能的FPGA組成,其原理框圖如圖1所示。

2020-03-12 07:55:00 1754

1754

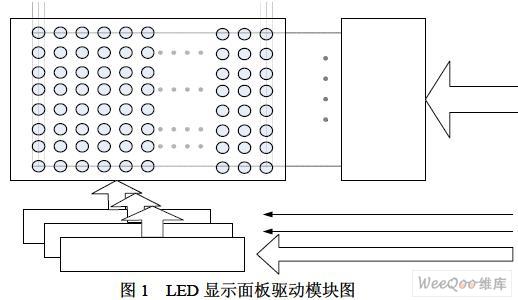

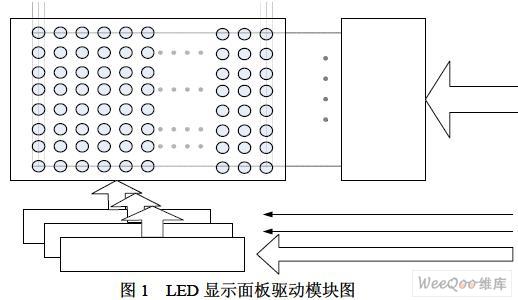

提出了一種基于FPGA 的LED 掃描屏控制系統(tǒng)的實(shí)現(xiàn)方案,通過(guò) 硬件和軟件的輔助設(shè)計(jì),完全實(shí)現(xiàn)了對(duì)LED 顯示屏的掃描控制。基于FPGA 的硬件設(shè)計(jì)大 大降低了電路系統(tǒng)的復(fù)雜性,提高了整個(gè)系統(tǒng)的開(kāi)發(fā)效率。

2018-12-30 10:20:00 4194

4194

建立了一個(gè)基于FPGA的可實(shí)現(xiàn)流水化運(yùn)行的OFDM系統(tǒng)的硬件平臺(tái),包括模擬前端、基于FPGA的OFDM調(diào)制器和OFDM 解調(diào)器。重點(diǎn)給出了OFDM調(diào)制解調(diào)器的實(shí)現(xiàn)構(gòu)架,對(duì)FPGA實(shí)現(xiàn)方法進(jìn)行了詳細(xì)的描述,介紹了系統(tǒng)調(diào)試方法,并對(duì)系統(tǒng)進(jìn)行了性能評(píng)價(jià)。

2018-12-13 16:45:51 22

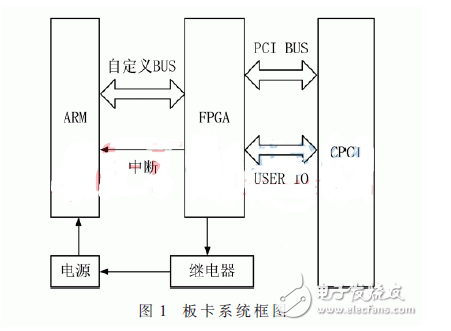

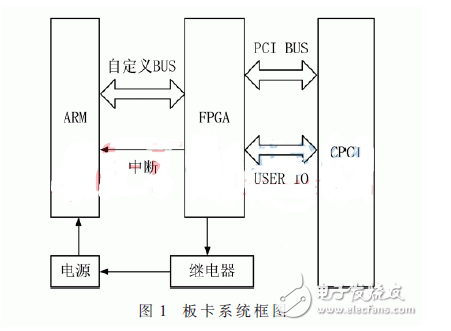

22 本文提出了一種基于FPGA的CPCI系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn),使用廉價(jià)FPGA芯片實(shí)現(xiàn)CPCI通信協(xié)議,同時(shí)利用FPGA的可編程特性實(shí)現(xiàn)電源控制、靈活中斷、外部觸發(fā)、外部通信等特殊應(yīng)用的功能,解決了CPCI協(xié)議經(jīng)過(guò)CPCI橋時(shí)的沖突問(wèn)題。

2019-01-06 11:37:13 2443

2443

電子發(fā)燒友網(wǎng)站提供《如何使用PXI平臺(tái)實(shí)現(xiàn)主動(dòng)懸架臺(tái)架試驗(yàn)測(cè)控系統(tǒng)的方案概述.pdf》資料免費(fèi)下載

2020-11-26 04:26:00 7

7 本文介紹了一種基于FPGA的圖像目標(biāo)發(fā)生器的設(shè)計(jì)方法,介紹了它的設(shè)計(jì)原理、硬件電路結(jié)構(gòu)、各功能的實(shí)現(xiàn)方法。該圖像發(fā)生器能產(chǎn)生灰度階圖像、靜態(tài)目標(biāo)圖像和運(yùn)動(dòng)目標(biāo)圖像,用來(lái)對(duì)圖像采集系統(tǒng)進(jìn)行評(píng)估。

2021-01-26 15:57:03 7

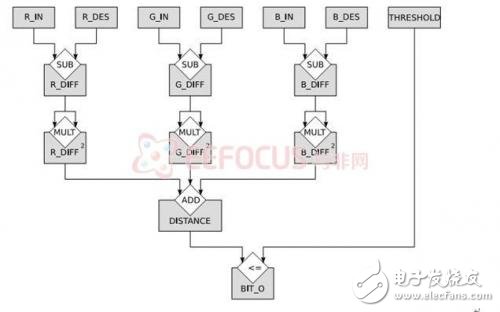

7 采用FPGA搭建圖像處理系統(tǒng),通過(guò)硬件算法實(shí)現(xiàn)圖像的流水線及并行處理,實(shí)現(xiàn)了對(duì)具有特定顏色的物體的識(shí)別與跟蹤

2021-04-06 14:07:15 4319

4319

基于多相機(jī)捕捉系統(tǒng)下的通用物體運(yùn)動(dòng)捕捉方法

2021-06-25 10:34:32 29

29 FPGA-DCM使用詳解(通信電源技術(shù)期刊編輯部電話)-該文檔為FPGA-DCM使用詳解文檔,是一份還算不錯(cuò)的參考文檔,感興趣的可以下載看看,,,,,,,,,,,,,,,,

2021-09-28 11:22:17 6

6 本文詳細(xì)描述了FPGA實(shí)現(xiàn)圖像去霧的實(shí)現(xiàn)設(shè)計(jì)方案,采用暗通道先驗(yàn)算法實(shí)現(xiàn),并利用verilog并行執(zhí)行的特點(diǎn)對(duì)算法進(jìn)行了加速;

2023-06-05 17:01:45 862

862

動(dòng)作捕捉系統(tǒng)的一般性結(jié)構(gòu)主要分為三個(gè)部分:數(shù)據(jù)采集設(shè)備、數(shù)據(jù)傳輸設(shè)備、數(shù)據(jù)處理單元,慣性式動(dòng)作捕捉系統(tǒng)即是將慣性傳感器應(yīng)用到數(shù)據(jù)采集端,數(shù)據(jù)處理單元通過(guò)慣性導(dǎo)航原理對(duì)采集到的數(shù)據(jù)進(jìn)行處理,從而完成運(yùn)動(dòng)目標(biāo)的姿態(tài)角度測(cè)量。

2023-06-26 10:17:46 694

694

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論