DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統有充足的時序裕量。要保證系統的時序,線長匹配又是一個重要的環節。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制

2017-09-01 14:03:41 4392

4392

DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統有充足的時序裕量。要保證系統的時序,

2017-09-26 11:39:47 6363

6363

多年前,無線時代(Beamsky)發布了一篇文章關于DDR布線指導的一篇文章,當時在網絡上很受歡迎,有很多同

2017-10-16 09:22:08 36277

36277

星形拓補就是地址線走到兩片DDR中間再向兩片DDR分別走線,菊花鏈就是用地址線把兩片DDR“串起來”,就像羊肉串,每個DDR都是羊肉串上的一塊肉,哈哈,開個玩笑。

2018-03-12 08:36:07 14664

14664

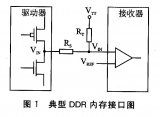

嵌入式DDR(Double Data Rate,雙數據速率)設計是含DDR的嵌入式硬件設計中最重要和最核心的部分。隨著嵌入式系統的處理能力越來越強大,實現的功能越來越多,系統的工作頻率越來越高,DDR的工作頻率也逐漸從最低的133 MHz提高到200 MHz,從而實現了更大的系統帶寬和更好的性能。

2018-04-14 07:38:01 3947

3947

本文首先列出了DDR2布線中面臨的困難,接著系統的講述了DDR2電路板設計的具體方法,最后給出個人對本次電路設計的一些思考。

2020-11-20 10:28:35 6386

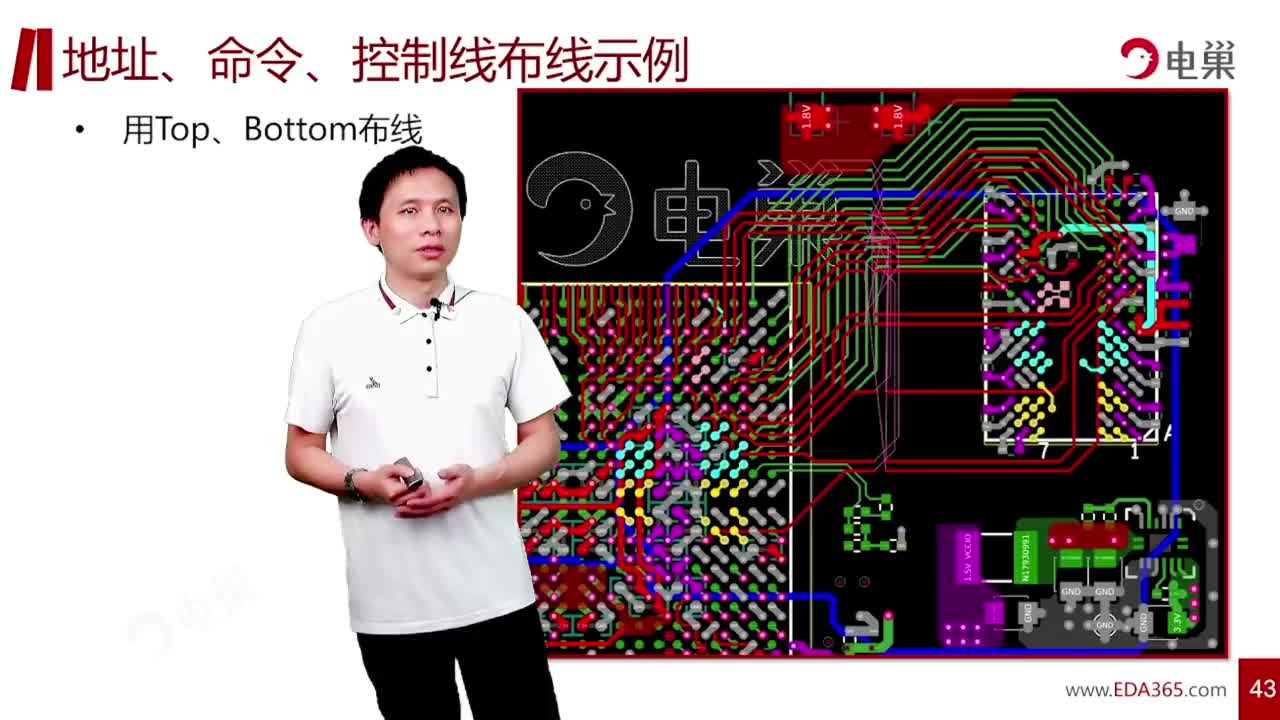

6386 上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。

2023-08-16 15:20:58 1379

1379

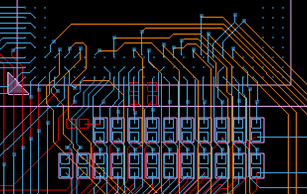

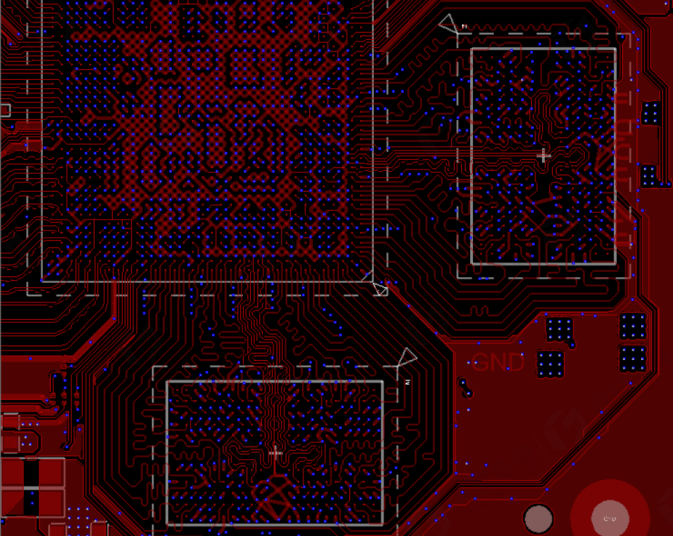

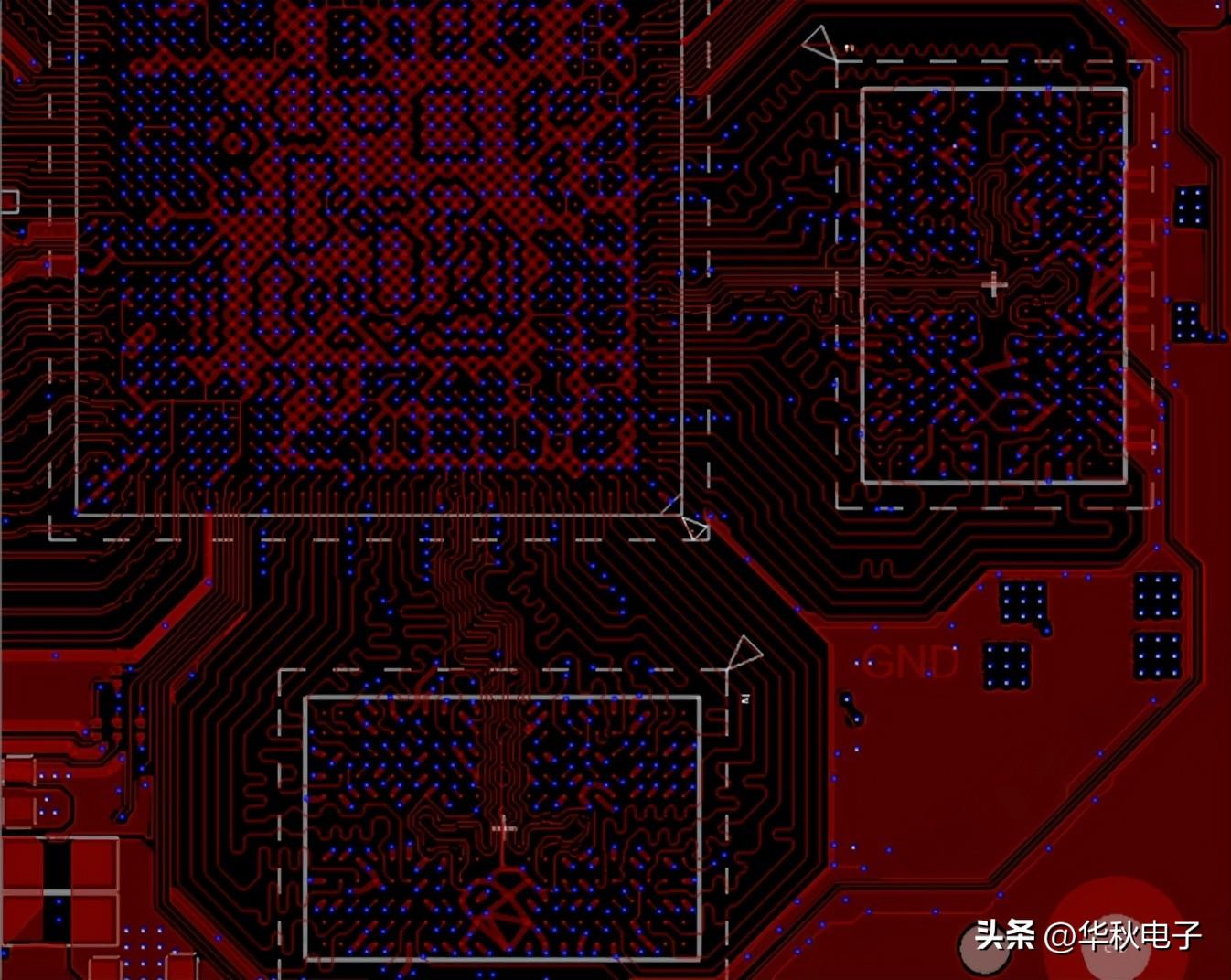

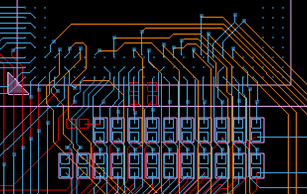

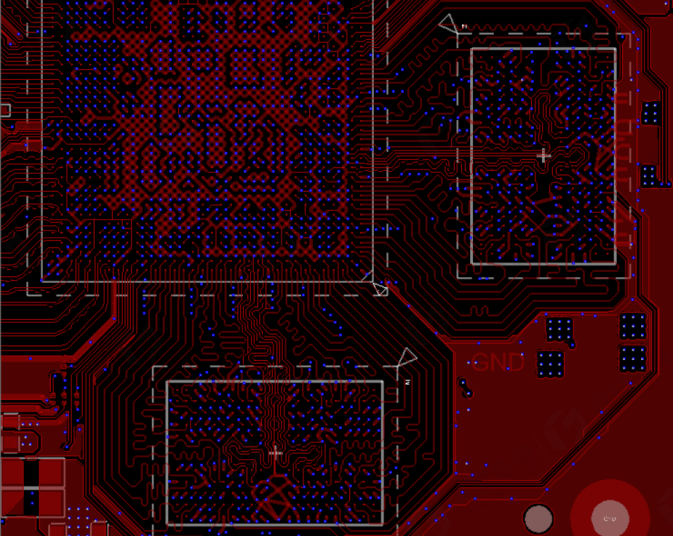

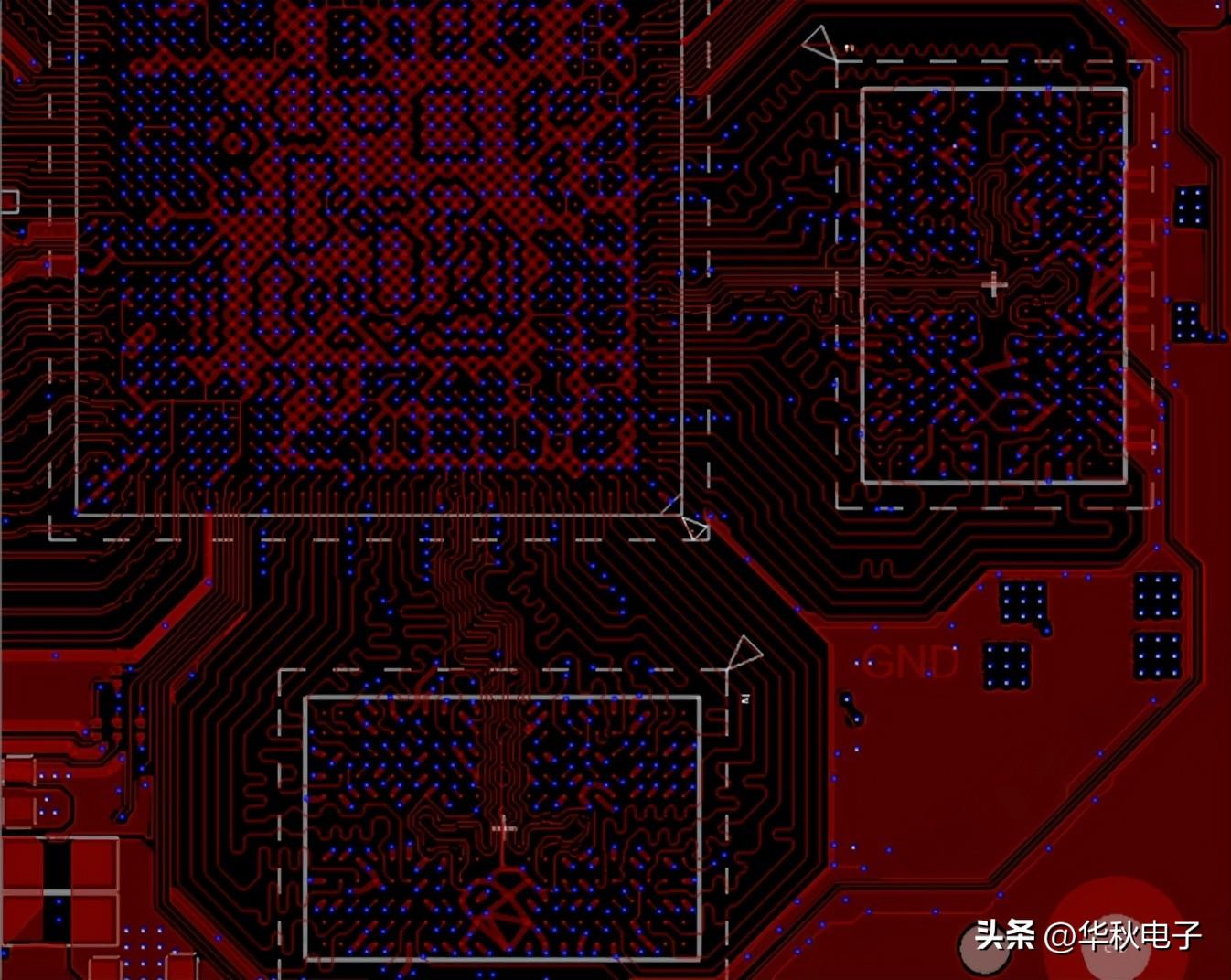

PCB設計空間足夠的情況下,優先考慮留出DDR電路模塊所需要的布局布線空間,拷貝瑞芯微原廠提供的DDR模板,包含芯片與DDR顆粒相對位置、電源濾波電容位置、鋪銅間距等完全保持一致。 如下8張圖(從左至右),分別為:L1-L8層DDR電路走線示意圖。 如果自己設計PCB,請參考以下PCB設計建

2023-08-18 10:55:43 556

556

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。 由于

2023-08-21 17:16:50 563

563

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。 由于

2023-08-24 08:40:05 899

899

大家好,為了能夠leveling成功,DDR3的布線約束需要規定到每一片DRAM的CLK長度與DQS長度差值不能超過一定范圍。但是根據6678或者6670開發板,其中關于DQS和CLK長度差的布線

2019-01-02 15:21:58

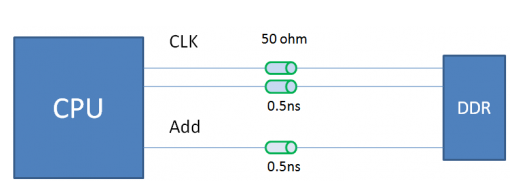

約束來進行布線。所有的DDR差分時鐘信號都必須在關鍵平面上走線,盡量避免層到層的轉換。線寬和差分間距需要參考DDR控制器的實施細則,信號線的單線阻抗應控制在50~60 Ω,差分阻抗控制在100~120

2015-01-15 10:39:37

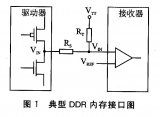

、鎖相環等硬件資源。使用這些特性,可以更加容易地設計性能可靠的高速DDRSDRAM存儲器控制器。 1 DDR SDRAM 在嵌入式系統中的應用 圖1是DDR SDRAM在高速信號源系統中的應用實例

2018-12-18 10:17:15

主要是針對DDR2 667內存的設計。信號分組:DDR2的布線中習慣把信號分成若干組來進行設計,分成同組的信號具有相關或者相似的信號特性。時鐘組:差分時鐘信號,每一對信號都是同頻同相的。ckp0

2011-10-27 14:53:32

共享交流一下,DDR3布線技巧

2016-01-08 08:17:53

這篇帖子跟大家一起來討論下DDR3布線的那些事:DDR3的設計有著嚴格等長要求,歸結起來分為兩類(以64位的DDR3為例): 數據 (DQ,DQS,DQM):組內等長,誤差控制在20MIL以內,組間

2016-10-28 10:25:21

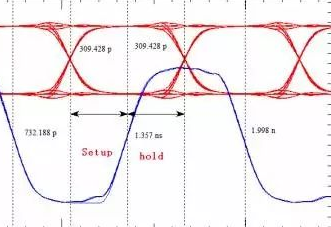

了極大的挑戰。 本文主要使用了Cadence公司的時域分析工具對DDR3設計進行量化分析,介紹了影響信號完整性的主要因素對DDR3進行時序分析,通過分析結果進行改進及優化設計,提升信號質量使其可靠性

2014-12-15 14:17:46

還未接觸過DDR4,在LAYOUT顆粒設計中,布局布線上DDR3與DDR4有沒有區別?有哪些區別?

2019-03-07 10:11:39

DDR2,DDR3等 因頻率不同,可以會有不同的要求,就一般而言,DDR布線時,要將DDR的網絡分成幾個組:地址線,控制線,數據線,時鐘等差分線。我的疑問是,在6層板中,需不需要將地址線與數據線分別

2015-11-04 13:40:02

DDR布線參考Hardware and Layout Design Considerations for DDR Memory InterfacesEmbedded systems

2009-11-19 10:08:48

DDR-Topology DDR布線通常是一款硬件產品設計中的一個重要的環節,也正是因為其重要性,網絡上也有大把的人在探討DDR布線規則,有很多同行故弄玄虛,把DDR布線說得很難,我在這里要

2019-05-31 07:52:36

的Layout也就成為了一個十分關鍵的問題,很多時候,DDR的布線直接影響著信號完整性。下面本文針對DDR的Layout問題進行討論。(Micron觀點)[/url]信號引腳說明VSS為數字地,VSSQ為信號

2012-12-29 19:20:36

低于125MHz),根本上還是要從布線上改善。最好用IBIS模型做一下信號完整性分析。 http://processors.wiki.ti.com/index.php/Main_PageThink

2020-08-14 08:59:56

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。

由于

2023-08-16 15:15:53

嵌入式Linux驅動開發(一)DDR內存DDRUARTI2CSPIDDR內存RAM: 隨機存儲器,可以隨時進行讀寫操作,速度很快,掉電以后數據會丟失。比如內存條、 SRAM、 SDRAM、 DDR

2021-12-16 07:10:10

的[A13-A0],還是用AM3892的DDR_A[13:0]接到兩片DDR3芯片的[A13-A0]?

(2)此外能講述一下DDR3的布線規則嗎?? AM3892 能否 將 開發板的8片小容量 DDR3換成

2018-06-21 11:19:34

摘要本文檔旨在介紹如何讓所有設計人員都能簡單方便地實現 AM64x\\\\AM243x DDR 系統,并將要求提煉為一組布局和布線規則,使設計人員能夠針對 TI 支持的拓撲成功實現穩健的設計。內容1

2023-04-14 17:03:27

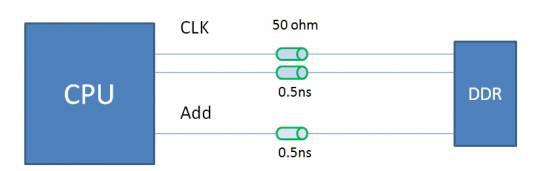

請問 在TI 給出的 ?EVM 參考設計中 DDR 的走線都串入一個22歐姆的電阻,按照SI 的理論這個電阻是保證匹配減少過沖的,在POWER PC 及MIPS 架構的CPU ?DDR布線中不需要增加這個電阻 ,請問這個電阻在TI ?ARM 的CPU 中一定需要嗎?

2018-05-15 09:35:28

,從DDR一代到DDR四代,全面的去告訴大家應該如何去處理DDR的設計。直播大綱:1、DDR原理信號分析2、DDR布局思路解析(1/2/4片)3、DDR布線思路解析(1/2/4片)4、DDR信號時序

2018-10-10 11:49:20

做嵌入式開發的工程師肯定都接觸過DDR,DDR就是我們常說的內存的大小,現在DDR已經發展到DDR5系列了,存儲容量和存儲速度都得到了極大的提高。但嵌入式項目中目前用到最多的還是DDR3和DDR

2020-09-16 15:30:27

最近要自己畫DM6437的板子,以前師兄畫的第一版DDR2的部分有問題,沒有找出來中間哪里有問題,所以在這里請教一下DDR2布線有什么要求,如果自己檢查哪里有問題一般從哪幾方面開始?

2018-05-25 02:49:17

,DDR5 CAC信號的ODT閃亮登場!我猜最激動還是Layout攻城獅:DDR5的CAC信號有了ODT功能,PCB布線約束可以放寬松了嗎?畢竟,哪里信號質量差就可以端接哪里,So easy。帶著這個

2022-12-28 14:47:13

多年前,無線時代(Beamsky)發布了一篇文章關于DDR布線指導的一篇文章,當時在網絡上很受歡迎,有很多同行參與了轉載。如今看來,那篇文章寫得不夠好,邏輯性不強,可操作性也不強。在近幾年的硬件產品

2022-08-11 09:07:02

本期講解的是高速PCB設計中DDR布線要求及繞等長要求。布線要求數據信號組:以地平面為參考,給信號回路提供完整的地平面。特征阻抗控制在50~60 Ω。線寬要求參考實施細則。與其他非DDR信號間距至少

2017-10-16 15:30:56

RVS — 嵌入式軟件分析套件

2021-01-15 06:28:25

使用公式分析和理論分析兩種方法,以實例證明公式的局限性和兩種方法的利弊。本文最后還基于這些實例分析,給出了SDRAM和DDR SDRAM等布線的一般性原則。

2021-05-19 06:52:58

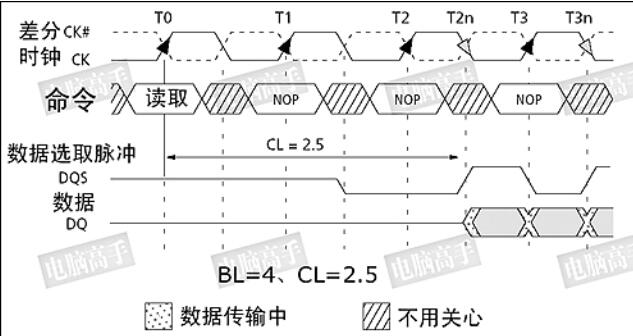

保持時間,同頻同相,采樣正確。等長只不過可以最簡單地實現這個目的罷了。要定量分析線長,必須按照時鐘模型公式計算。時鐘同步電路的類型在后面有簡單介紹,這里只要知道SDRAM是公共時鐘同步,DDR是源同步

2010-03-18 15:33:07

1、Zynq MPSoC支持的DDR介紹自己做自己的嵌入式產品一般要選擇合適的DDR,而這里開發板給的是4GB的UIMM的DDR4,也就是電腦上用的,所以用不了,只能自己掛載Component,這里

2022-04-19 17:56:03

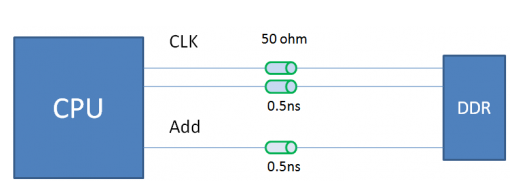

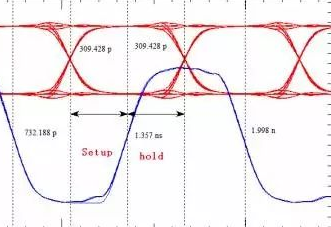

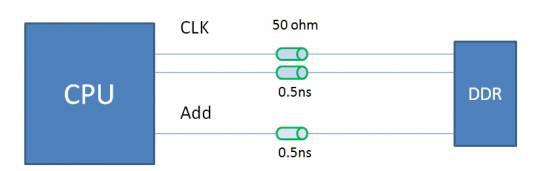

一下具體波形。 建立如下通道,分別模擬3的地址信號與時鐘信號。 圖1 地址/時鐘仿真示意圖 為方便計算,我們假設DDR的時鐘頻率為500MHz,這樣對應的地址信號的速率就應該是500Mbps

2018-09-19 16:21:47

相關的基礎知識和設計及仿真技巧,本系列的大致安排如下圖所示。 本系列共分四大部分,分別是基礎理論介紹,布局布線規劃介紹,設計及仿真分析以及后期的測試及調試上的一些案例介紹。這個是目前的一個規劃,其中

2016-08-16 15:57:07

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。

由于

2023-08-17 17:23:30

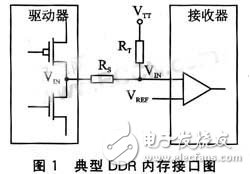

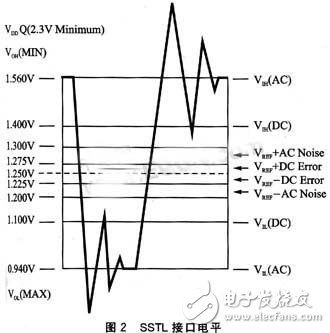

2.5V 的SSTL2 標準B. 關于DDR SDRAMDDR 存儲芯片有多種形式,其封裝有SOP/BGA/SLOT(插槽);但原理基本是相同的。1. 信號定義說明信號名功能備注CK/CK# 系統時鐘

2012-09-17 21:15:33

DDR總線結構是什么嵌入式DDR總線的布線分析

2021-04-25 07:36:29

在DDR的PCB布線中提到,數據線可以分組等長,各組之間可以不等長,那怎樣保證32位數據的時序呢?

2023-04-10 16:49:54

在DDR的PCB布線中提到,數據線可以分組等長,各組之間可以不等長,那怎樣保證32位數據的時序呢?

2023-04-11 17:36:23

hello,各位大俠,請問如何測試嵌入式系統linux下的CPU及DDR性能,或者類似跑分軟件。

2016-07-11 17:11:46

帶有DDR的嵌入式系統主板中,設計PCB最難的部分莫過于DDR的走線設計。好的走線就等于有了好的信號完整性和好的時序匹配,總線在高速輸入/輸出數據過程中就不會出錯,甚至能夠有更好的抗串擾和EMC能力

2015-10-21 10:37:10

PCB布線設計的好壞直接影響到硬件電路能否正常工作或運行多快的速度。而在高速數字PCB設計中,DDR2是非常常見的高速緩存器件,且其工作頻率很高本文將針對DDR2的PCB布線進行討論。DDR

2016-12-26 16:56:05

DDR SDRAM在嵌入式系統中有哪些應用?DDR SDRAM的工作方式有哪幾種?怎樣去設計DDR SDRAM控制器?

2021-04-30 07:04:04

DDR3布線時CPU到DDR3的地址線長2037mil ,數據線長1613mil,這樣會不會有問題

2019-06-05 03:34:28

本帖最后由 gk320830 于 2015-3-5 12:38 編輯

飛思卡爾的關于DDR內存布線設計資料,主要涉及了內存高頻控制線的等長,阻抗匹配的等設計

2013-08-26 13:31:20

本期講解的是高速PCB設計中,關于DDR布線知識。一.DDR信號功能與網絡名了解DDR的各個信號功能與網絡名。與DDR相比,DDR2/3最大差別多了功能OTD與OCD。重要信號線1.DQS信號

2017-10-27 10:48:26

嵌入式DDR接口原理及設計

有助于SoC設計取得成功的十條建議

DDR3等DRAM標準是由JEDEC開發的。這個組織已經為許多半導體器件制定過標準,而大多數DR

2010-03-13 11:36:47 88

88 SDRAM與DDR布線指南:ecos應用是與硬件平臺無關的,雖然開發板沒有涉及到SDRAM和DDR,不過,在某些高端平臺上使用ecos可能會遇到內存布線問題,為了完整敘述,這里一并給出說明。 很

2010-03-18 15:29:08 0

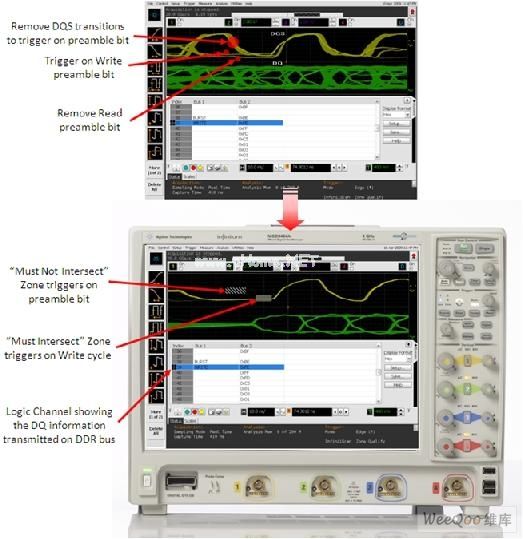

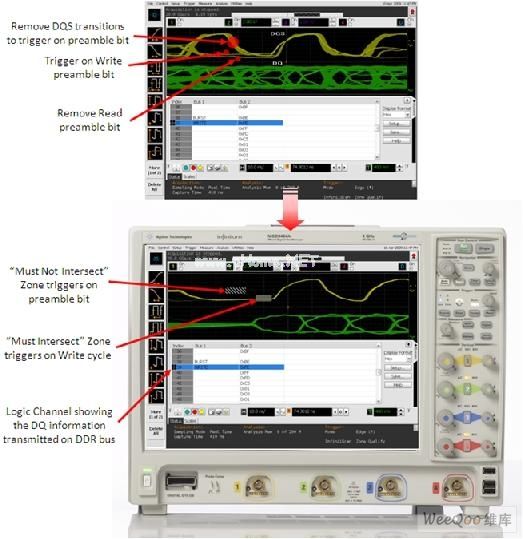

0 不只計算機存儲器系統一直需要更大、更快、功率更低、物理尺寸更小的存儲器,嵌入式系統應用也有類似的要求。本應用指南介紹了邏輯分析儀在檢驗DDR, DDR2 和DDR3 SDRAM 命令和

2010-08-06 08:29:49 79

79 用高帶寬混合信號示波器進行DDR驗證和調試的技巧

?? DDR存儲器,也稱雙倍數據率同步動態隨機存儲器,常用于高級嵌入式電路系統的設計,包括計算機、交通運

2010-03-02 11:08:48 582

582

研究了MPC8379E處理器的相關資料和DDR2的特性,以及它們之間PCB布線的規則和仿真設計。由于MPC8379E和DDR2都具有相當高的工作頻率,所以他們之間的走線必須滿足高速PCB布線規則,還要結

2013-03-12 15:22:26 80

80 PCB的DDR布局布線規則與實例教程說明

2015-11-13 16:13:47 0

0 針對DDR2-800和DDR3的PCB信號完整性設計

2016-02-23 11:37:23 0

0 介紹DDR的起源和發展歷史,發展趨勢,DDR的布局,參數含義。

2016-05-13 11:28:05 5

5 針對DDR2-800和DDR3的PCB信號完整性設計,要認證看

2016-12-16 21:23:41 0

0 DDR2_DDR3_SDRAM,PCB布線規則指導

2017-10-31 10:06:48 78

78 在DDR的PCB設計中,一般需要考慮等長和拓撲結構。等長比較好處理,給出一定的等長精度通常是PCB設計師是能夠完成的。但對于不同的速率的DDR,選擇合適的拓撲結構非常關鍵,在DDR布線中經常使用的T型拓撲結構和菊花鏈拓撲結構,下面主要介紹這兩種拓撲結構的區別和注意要點。

2017-11-08 13:00:47 24311

24311

DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統有充足的時序裕量。要保證系統的時序,線長匹配又是一個重要的環節。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制

2017-11-28 11:34:58 0

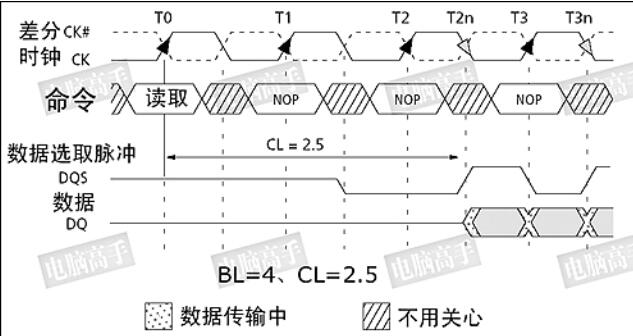

0 Random Access Memory的縮寫,即同步動態隨機存取存儲器。本文首先介紹了DDR工作原理及結構圖,其次闡述了DDR DQS信號的處理,具體的跟隨小編一起來了解一下。

2018-05-23 16:07:19 50490

50490

DDR布線在PCB設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統有充足的時序裕量。要保證系統的時序,線長匹配又是一個重要的環節。我們來回顧一下,DDR布線,線長匹配的基本原則是:地址,控制/命令信號與時鐘做等長。

2018-09-27 09:56:00 6659

6659

DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM

2018-12-19 08:00:00 76

76 在普通印制電路板的布線中由于信號是低速信號,所以在3W原則的基本布線規則下按照信號的流向將其連接起來,一般都不會出現問題。但是如果信號是100M以上的速度時,布線就很有講究了。由于最近布過速度高達300M的DDR信號,所以仔細說明一下DDR信號的布線原則和技巧。

2019-03-24 10:00:06 6906

6906

在現代高速數字電路的設計過程中,工程師總是不可避免的會與DDR或者DDR2,SDRAM打交道。DDR的工作頻率很高,因此,DDR的布線(或者Layout)也就成為了一個十分關鍵的問題,很多時候,DDR的布線直接影響著信號完整性。下面本文針對DDR的布線問題(Layout)進行討論。

2019-06-08 14:35:00 4347

4347 Intel已經從服務器到消費級、從高端到低端徹底完成了DDR4內存的轉換,AMD這邊則直到今天才真正進入DDR4的時代,但首款產品卻是面向嵌入式領域的R系列APU/CPU,開發代號“Merlin Falcon”。

2019-06-26 17:07:04 723

723 2014年,推出了第四代DDR內存(DDR4),降低了功耗,提高了數據傳輸速度和更高的芯片密度。 DDR4內存還具有改進的數據完整性,增加了對寫入數據的循環冗余檢查和片上奇偶校驗檢測。

2019-07-26 14:34:01 45989

45989 第一步,確定拓補結構(僅在多片DDR芯片時有用) 首先要確定DDR的拓補結構,一句話,DDR1/2采用星形結

2019-08-20 10:02:14 7258

7258 DDR布線在pcb設計中占有舉足輕重的地位,設計成功的關鍵就是要保證系統有充足的裕量。要保證系統的時序,線長又是一個重要的環節。

2020-01-14 14:46:10 1187

1187 本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 由于FPGA芯片是有關于DDR的設計指導文檔,我司的PCB工程師和客戶在投板前也反復確認了該DDR模塊的設計是完全按照文檔上面每一條細致的指導去布線的。

2021-03-17 15:00:27 2686

2686 采用蛇形設計、差分信號走線等長、等距設計,來盡可能減少電磁輻射(EMI)對主板其余部件和外界的影響。今天,編者就具體以某車機產品的高速 DDR 時鐘信號設計為例,跟大家講解 PCB 布線設計 EMC 整改的具體分析思路、方案設計。

2020-12-08 16:12:00 13

13 本篇主要針對Zynq UltraScale + MPSoC的DDR接口,從硬件設計的角度進行詳細介紹,最后展示一下小編之前自己設計的基于ZU+的外掛8顆DDR4的設計。

2020-12-28 08:00:00 0

0 一些設計方法在以前已經成熟的使用過。 1 介紹 目前,比較普遍使用中的DDR2的速度已經高達800 Mbps,甚至更高的速度,如1066 Mbps,而DDR3的速度已經高達1600 Mbps。 對于如此高的速度,從PCB的設計角度來幫大家分析,要做到嚴格的時序匹配,以滿足信號的完整性,

2021-03-25 14:26:01 3864

3864

DDR4布線之allegro約束規則設置綜述

2021-09-08 10:34:29 0

0 在PCB設計時我們在處理DDR部分的時候都會進行一個拓撲的選擇,一般DDR有T點和Fly-by兩種拓撲結構,那么這兩種拓撲結構的應用場景和區別有哪些呢? T點拓撲結構: CPU出來的信號線經過

2022-11-27 07:40:01 999

999 上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。 由于

2023-08-17 18:15:02 325

325

上期和大家聊的電源PCB設計的重要性,那本篇內容小編則給大家講講存儲器的PCB設計建議,同樣還是以大家最為熟悉的RK3588為例,詳細介紹一下DDR模塊電路的PCB設計要如何布局布線。由于

2023-08-18 08:09:43 384

384

PCB布線對模擬信號傳輸的影響如何分析,如何區分信號傳輸過程中引入的噪聲是布線導致還是運放器件導致? PCB布線對模擬信號傳輸的影響是一項非常復雜的任務,需要考慮諸如電容、電感、阻抗、信號完整性

2023-10-31 14:34:18 439

439 SDRAM與DDR布線指南

2022-12-30 09:20:50 10

10 再談DDR內存布線

2022-12-30 09:21:08 2

2 PCB的DDR4布線指南和PCB的架構改進

2023-12-07 15:15:58 760

760

正在加载...

電子發燒友App

電子發燒友App

評論