1 引言

近年來隨著網(wǎng)絡(luò)的快速發(fā)展,以太網(wǎng)因其寬帶、擴(kuò)展性強(qiáng)、組網(wǎng)靈活而成為應(yīng)用最廣泛的數(shù)據(jù)接入網(wǎng)絡(luò)。以太網(wǎng)的網(wǎng)絡(luò)終端設(shè)備是網(wǎng)絡(luò)的重要組成部分,是網(wǎng)絡(luò)與網(wǎng)外互訪信息的協(xié)議界面和工作平臺。嵌入式以太網(wǎng)網(wǎng)絡(luò)終端設(shè)備采用嵌入式處理器技術(shù),使用嵌入式操作系統(tǒng),內(nèi)嵌網(wǎng)絡(luò)接口和網(wǎng)絡(luò)通信協(xié),可直接接入以太網(wǎng)。由于嵌入式網(wǎng)絡(luò)終端設(shè)備具有成本低、體積小、高可靠、微功耗、環(huán)境適應(yīng)能力強(qiáng)等諸多優(yōu)勢,在通信和工業(yè)控制等領(lǐng)域正得到日益廣泛的應(yīng)用。本文主要介紹用SOPC技術(shù)構(gòu)建嵌入式以太網(wǎng)網(wǎng)絡(luò)終端的設(shè)計(jì)和實(shí)踐。基于SOPC技術(shù)的嵌入式以太網(wǎng)網(wǎng)絡(luò)終端能夠?yàn)槎喾N聯(lián)網(wǎng)應(yīng)用提供基本的工作平臺。

與當(dāng)前較為流行的嵌入式處理器如基于ARM內(nèi)核的處理器、系列處理器等不同,SOPC技術(shù)的是把處理器作為“內(nèi)核”嵌入到芯片中,在可編程芯片上實(shí)現(xiàn)系統(tǒng)功能。可嵌入的處理器內(nèi)核有兩種:硬核或軟核。其中軟核因?yàn)槌杀镜汀⒖芍貥?gòu)性強(qiáng)、功能靈活、適用的芯片范圍廣等特點(diǎn)更適合于應(yīng)用在中小批量生產(chǎn)的差異化產(chǎn)品中。

采用硬件技術(shù)處理信號,又可以通過軟件反復(fù)編程使用,能兼顧速度和靈活性,實(shí)時(shí)性能可以精確預(yù)測和仿真。FPGA芯片的一個(gè)顯著優(yōu)勢是具有強(qiáng)大的硬件并行處理能力,這種能力不受處理器架構(gòu)的限制而只取決于芯片的物理資源。隨著深亞微米半導(dǎo)體技術(shù)的進(jìn)步,目前FPGA單片所含的邏輯門和片上存儲器的容量發(fā)展很快,百萬門級的可編程邏輯芯片已成為尋常產(chǎn)品。因此在一般算法復(fù)雜度的多路信號處理(通常語音通信和工業(yè)控制均可歸入該范圍)中,F(xiàn)PGA比DSP更能勝任工作,而且并行處理的路數(shù)越多,這個(gè)優(yōu)勢越突出。是公司開發(fā)的一種軟核處理器。應(yīng)用SOPC技術(shù)把配置進(jìn)FPGA芯片后,網(wǎng)絡(luò)終端備不再需要外部處理器,用單一FPGA芯片就可以實(shí)現(xiàn)以前需要FPGA+CPU才能完成的功能。

2 網(wǎng)絡(luò)終端的總體設(shè)計(jì)

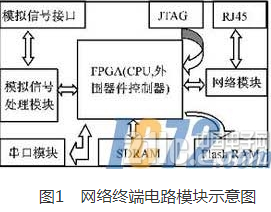

基于SOPC技術(shù)的嵌入式以太網(wǎng)網(wǎng)絡(luò)終端的硬件和固件部分由帶軟核CPU的FPGA芯片、外部數(shù)據(jù)存儲器FlashRAM和、帶AD和DA變換電路的模擬信號處理模塊、串行、以太網(wǎng)網(wǎng)絡(luò)模塊及接口、JTAG等組成,見圖1。此外還有及配置電路等,從略。

在圖1中,F(xiàn)PGA芯片選用公司的Cyclone系列芯片,該芯片采用0.13μm的全銅1.5V 工藝制作,具有5980個(gè)邏輯單元(LE),92160個(gè)RAM比特,兩個(gè)數(shù)字鎖相環(huán)(PLL),240引腳封裝。

程序存儲器選用AMD公司的FlashRAM芯片,存儲容量2MByte,擦寫次數(shù)可達(dá)100萬次。數(shù)據(jù)存儲器選用公司的芯片MT48LC4M32B2,存儲容量16MByte,訪問速度5.5ns。使用較大容量的數(shù)據(jù)存儲器主要是為今后試驗(yàn)運(yùn)行各種不同的嵌入式操作系統(tǒng)預(yù)留空間。

以太網(wǎng)接口芯片采用。該芯片是 公司生產(chǎn)的一種局域網(wǎng)信號處理芯片,內(nèi)部集成了片上RAM,其模擬前端包括了曼切斯特編解碼器、時(shí)鐘恢復(fù)電路、10BASE-T收發(fā)器和及一個(gè)AUI口。的MAC(媒體訪問控制)引擎負(fù)責(zé)以太網(wǎng)數(shù)據(jù)幀的發(fā)送和接收,檢測和處理沖突,生成和檢測幀引導(dǎo)頭(Preamble),自動生成和校驗(yàn)CRC(循環(huán)冗余校驗(yàn))碼。芯片在網(wǎng)絡(luò)物理層符合IEEE802.3以太網(wǎng)標(biāo)準(zhǔn),支持全雙工操作。

A/D和D/A變換器采用ADI公司的芯片。具有一個(gè)16bit的AD轉(zhuǎn)換通道和一個(gè)16bit的D/A轉(zhuǎn)換通道,A/D和D/A轉(zhuǎn)換通道的增益可分別在38dB和21dB范圍內(nèi)編程控制,每一個(gè)通道都在聲音頻帶范圍內(nèi)提供70dB的信噪比。采樣頻率為8kHz~64kHz,可編程控制,采樣字長為16位。選用是因?yàn)樵撔酒坏蓱?yīng)用于一般模擬信號的A/D和D/A變換,而且能夠滿足語音信號的前端處理要求,便于今后試驗(yàn)功能。

JTAG接口用于從PC機(jī)向FPGA芯片下載配置文件以及調(diào)試系統(tǒng),串口用于連接PC機(jī)進(jìn)行系統(tǒng)的軟件調(diào)試及在聯(lián)網(wǎng)應(yīng)用中傳送信息到外部設(shè)備。

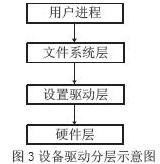

終端的軟件部分主要由嵌入式操作系統(tǒng)μC/OSⅡ、網(wǎng)絡(luò)協(xié)議LWIP及應(yīng)用軟件組成。嵌入式操作系統(tǒng)是一種實(shí)時(shí)的、支持嵌入式應(yīng)用的操作系統(tǒng),通常包括與硬件相關(guān)的底層驅(qū)動軟件、系統(tǒng)內(nèi)核、設(shè)備驅(qū)動接口、通信協(xié)議等。與PC操作系統(tǒng)相比較,嵌入式操作系統(tǒng)在系統(tǒng)的實(shí)時(shí)高效性、硬件的相關(guān)依賴性、軟件固態(tài)化以及應(yīng)用的專用性等方面具有較為突出的特點(diǎn)。

當(dāng)前各種主要的嵌入式操作系統(tǒng)(如、VxWorks、μC-、μC/OSII等)均在不同程度上支持多種類型的外圍硬件設(shè)備和多種通信協(xié)議,可以有較多的手段實(shí)現(xiàn)外圍硬件的驅(qū)動。完備的操作系統(tǒng)支持很多通信協(xié)議,采用操作系統(tǒng)后,可直接調(diào)用這些協(xié)議實(shí)現(xiàn)通信,避免過多的底層編程耗費(fèi)時(shí)間精力,減少出錯(cuò)。

在本網(wǎng)絡(luò)終端中選擇μC/OSⅡ作為嵌入式操作系統(tǒng)。μC/OSⅡ是一個(gè)相對成熟而且是免費(fèi)的嵌入式操作系統(tǒng),適合小型控制系統(tǒng),具有執(zhí)行效率高、占用空間小、實(shí)時(shí)性能優(yōu)良等特點(diǎn)。其缺點(diǎn)是對于文件系統(tǒng)及網(wǎng)絡(luò)的復(fù)雜應(yīng)用等方面的支持遜于商業(yè)性的嵌入式操作系統(tǒng)。

在網(wǎng)絡(luò)通信軟件方面,選擇了LWIP來實(shí)現(xiàn)TCP/IP通信。LWIP是瑞士計(jì)算機(jī)科學(xué)院的Adam Dunkels等學(xué)者開發(fā)的源代碼開放的免費(fèi)TCP/IP協(xié)議棧。LWIP既可運(yùn)行于操作系統(tǒng)上,也可以獨(dú)立運(yùn)行。LWIP可以提供類似于Berkeley 套接字的應(yīng)用程序接口,使用它編寫出來的代碼兼容性很好,只要稍微修改就可以移植到別的常用操作系統(tǒng)上。因?yàn)棣藽/OSⅡ操作系統(tǒng)沒有自帶的TCP/IP協(xié)議棧,本網(wǎng)絡(luò)終端把lwIP移植到μC/OSⅡ操作系統(tǒng)上,使其成為操作系統(tǒng)的網(wǎng)絡(luò)模塊,這樣網(wǎng)絡(luò)通信就可以置于μC/OSⅡ的控制之下。

3 SOPC的開發(fā)流程

使用軟核處理器開發(fā)系統(tǒng)有其獨(dú)特的開發(fā)流程。本文所述工作以采用美國公司的軟核處理器Nios CPU為例來進(jìn)行開發(fā),使用的工具主要是Altera公司的設(shè)計(jì)軟件。這些軟件工具包括QuartusⅡ、SOuilder、GNUProToolkit等。

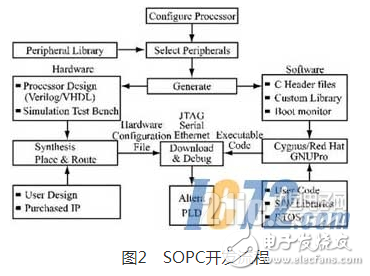

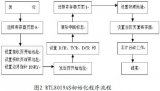

QuartusⅡ是Altera公司的FPGA設(shè)計(jì)軟件,具有設(shè)計(jì)輸入、、仿真、延時(shí)分析、編譯、下載文件以及配置器件等功能。SOPC Builder用于在QuartusⅡ設(shè)計(jì)平臺上進(jìn)行系統(tǒng)模塊的邏輯設(shè)計(jì)。用SOPC Builder可以進(jìn)行系統(tǒng)模塊硬件設(shè)計(jì)和底層軟件生成。進(jìn)行硬件模塊設(shè)計(jì)時(shí),SOPC Builder提供圖形化配置界面,備有一些常用外設(shè)的IP模塊,如、FlashRAM、、 、Intervaltimer、ParallelI/O等。這些已開發(fā)好并已經(jīng)引入到SOPC Builder環(huán)境中的功能模塊被稱為部件,打開SOPC Builder的圖形界面時(shí)可以在左邊看到這些功能部件。用戶還可以用“to ”加入自己的外設(shè)設(shè)計(jì)文件,或直接加外設(shè)接口。可以采用的外設(shè)設(shè)計(jì)文件是用或Verilog HDL等描述語言寫的.vhd或.v文件、由MAX+plusII生成的EDIF文件、或用QuartusⅡ輸入的電原理圖。SOPC Builder可以進(jìn)行系統(tǒng)配置以及生成,系統(tǒng)配置除了對外設(shè)設(shè)置外還包括啟動程序、中斷向量表、系統(tǒng)啟動地址等的設(shè)置。應(yīng)用軟件的設(shè)計(jì)在Cygwin環(huán)境中使用GNUPro工具包進(jìn)行,該工具包含有編譯、下載軟件、以及常用文件的操作命令等,熟悉Cygwin和的開發(fā)者很容易使用。SOPC開發(fā)的整個(gè)流程如圖2所示。

進(jìn)行系統(tǒng)設(shè)計(jì)時(shí),先在QuartusⅡ中新建一個(gè)工程,然后按圖2流程進(jìn)行設(shè)計(jì)。圖中,第一步是確定CPU,設(shè)置CPU是16位還是32位、要不要加硬件乘法指令等,這一步在“Configure Processor”中進(jìn)行。第二步是選擇外圍設(shè)備比如、SDRAM、FlashRAM、以及通用I/O等,加入用戶電路模塊到系統(tǒng)中也是在這一步。

第三步是生成,即生成用HDL語言描述的硬件組件以及用于軟件開發(fā)的SDK。至此的三步都在SOPC Builder中進(jìn)行。接下來分為硬件設(shè)計(jì)和軟件設(shè)計(jì)兩路。在硬件設(shè)計(jì)方面,按圖2左邊所示流程進(jìn)行片上系統(tǒng)設(shè)計(jì)、添加用戶電路,包括電路聯(lián)線、芯片選型、管腳設(shè)置等,通過系統(tǒng)后編譯生成.sof文件,并可根據(jù)需要對系統(tǒng)硬件進(jìn)行功能模擬和時(shí)序仿真分析。在軟件設(shè)計(jì)方面,按圖2右邊所示流程進(jìn)行軟件設(shè)計(jì)、編譯、鏈接,這一步的工作環(huán)境主要為SOPC Builder的軟件開發(fā)環(huán)境,也被稱為Cygnus。編譯軟件代碼用nios-build,簡寫為nb,用srec-flash來產(chǎn)生從FlashRAM啟動的代碼,下載軟件到系統(tǒng)中用nios-run,簡寫為nr。軟硬件的設(shè)計(jì)流程在最后又匯總在一起,將設(shè)計(jì)好的電路配置文件.sof通過JTAG下載到Altera FPGA中進(jìn)行調(diào)試。

4 嵌入式網(wǎng)絡(luò)終端的設(shè)計(jì)要點(diǎn)

4.1 Nios處理器的

本網(wǎng)絡(luò)終端使用32位處理器,通過QuartusII設(shè)計(jì)平臺上的SOPC Builder軟件把Nios軟核處理器配置到FPGA芯片中。Nios軟核能夠按照需求配置成16位或者32位的處理器,指令位數(shù)是16位。一般來說,16位處理器做成的系統(tǒng)反應(yīng)要比32位的快,但32位處理器可管理的資源要比16位多。數(shù)據(jù)總線、地址總線、寄存器以及算術(shù)邏輯單元的位數(shù)可根據(jù)需要配置成16或32位。寄存器個(gè)數(shù)也是可以配置的。

Nios CPU的體系結(jié)構(gòu)有1個(gè)通用寄存器組,10個(gè)控制寄存器,1個(gè)程序寄存器,1個(gè)K寄存器。在32位Nios CPU中每個(gè)通用寄存器的位寬為32。通用寄存器組中寄存器的數(shù)目可以根據(jù)需要設(shè)置成128、256或512個(gè)。某一時(shí)刻,Nios可以直接訪問(不改變CWP)的通用寄存器共有32個(gè),稱為寄存器窗口。組中寄存器的個(gè)數(shù)被稱為窗口的長度,又被稱為寄存器窗口的大小,值為32。寄存器窗口有四部分,處于最底端的8個(gè)寄存器被稱為全局寄存器,分別是%r0~%r7,也稱為%g0~%g7;全局寄存器不隨寄存器窗口位置的改變而改變,CPU對其隨時(shí)可以存取。剩下的24個(gè)寄存器通過當(dāng)前寄存器窗口來存取。最上端的8個(gè)被稱為輸入寄存器,緊接著輸入寄存器之后的被稱為局部寄存器,在局部寄存器和全局寄存器之間的8個(gè)寄存器為輸出寄存器。

4.2 FPGA片上系統(tǒng)

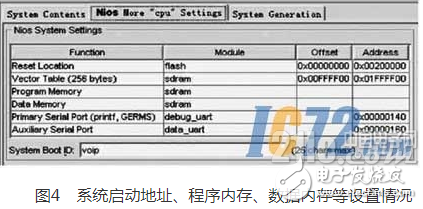

片上系統(tǒng)包括CPU以及和CPU緊密相連的總線系統(tǒng)和外圍硬件等。通過SOPC Builder可以選擇和設(shè)置片上系統(tǒng)模塊的部件,分配和修改系統(tǒng)對各部件的地址以及中斷號。

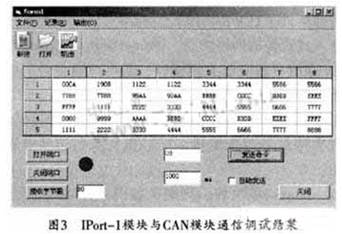

SOPC Builder為Nios設(shè)計(jì)了一種特別的總線———Avalon總線。Avalon是一種簡單的總線結(jié)構(gòu),規(guī)定了主部件和從部件之間的接口以及部件間通信的時(shí)序。Avalon總線由有源邏輯單元構(gòu)成,用于代替?zhèn)鹘y(tǒng)板子上的金屬線。SOPC Builder根據(jù)系統(tǒng)配置生成Avalon總線的.vhd文件,最后由QuartusⅡ根據(jù).vhd文件成片上總線結(jié)構(gòu)。本網(wǎng)絡(luò)終端片上系統(tǒng)的設(shè)置情況可以見圖3,該圖是SOPC Builder軟件的部件設(shè)置界面。可以直接在該界面把起始地址和中斷號修改成合適的值。

除了設(shè)置具體的部件外,還需要再設(shè)置系統(tǒng)的啟動地址、中斷向量表、程序內(nèi)存、數(shù)據(jù)內(nèi)存、主串口以及輔助串口,見圖4。這些設(shè)置和軟件目標(biāo)文件的鏈接過程緊密相關(guān)。SOPC Builder將根據(jù)這些設(shè)置來生成cpu-sdk目錄中子目錄lib、inc的相關(guān)文件。

4.3 網(wǎng)絡(luò)接口控制

設(shè)置以太網(wǎng)接口芯片工作于I/O模式。通過對芯片各寄存器的操作可設(shè)置網(wǎng)絡(luò)終端的功能和讀取狀態(tài)信息。CS8900A的主要寄存器有:

LineCTL:決定CS8900A的基本配置和物理接口,設(shè)置初始值為00D3H,選擇物理接口為10BASE-T。

RxCTL:控制CS8900A接收特定數(shù)據(jù)報(bào),設(shè)置RxTCL的初始值為0D05H,接收網(wǎng)絡(luò)上的廣播或目標(biāo)地址同本地物理地址相同的正確數(shù)據(jù)報(bào)。

RxCFG:控制CS8900A接收到特定數(shù)據(jù)報(bào)后會引發(fā)接收中斷,RxCFG可設(shè)置為0103H,收到正確數(shù)據(jù)報(bào)時(shí)產(chǎn)生接收中斷。

BusCTL:控制芯片的I/O接口操作,設(shè)置初始值為8017H,打開CS8900A的中斷總控制位。

ISQ:中斷狀態(tài)寄存器,內(nèi)部映射接收狀態(tài)寄存器和發(fā)送中斷寄存器內(nèi)容。

Port0:發(fā)送和接收數(shù)據(jù)時(shí),CPU通過Port0傳輸數(shù)據(jù)。

TxCMD:發(fā)送控制寄存器,如果寫入數(shù)據(jù)00C0H,那么網(wǎng)卡芯片在全部數(shù)據(jù)寫入后開始發(fā)送數(shù)據(jù)。

TxLength:發(fā)送數(shù)據(jù)長度寄存器,發(fā)送數(shù)據(jù)時(shí),首先寫入發(fā)送數(shù)據(jù)長度,然后將數(shù)據(jù)通過Port0寫入芯片。

系統(tǒng)上電時(shí),首先對CS8900A進(jìn)行初始化,寫寄存器LineCTL、RxCTL、RxCFG、BusCTL。發(fā)送數(shù)據(jù)時(shí), 寫控制寄存器TxCMD,并將發(fā)送數(shù)據(jù)長度寫入TxLength,然后將數(shù)據(jù)依次寫入Port0口,數(shù)據(jù)就可以發(fā)送出去了。接收到數(shù)據(jù)時(shí)CS8900A將觸發(fā)中斷,在其中斷處理程序中可以接收數(shù)據(jù)并處理。

4.4 AD/DA電路

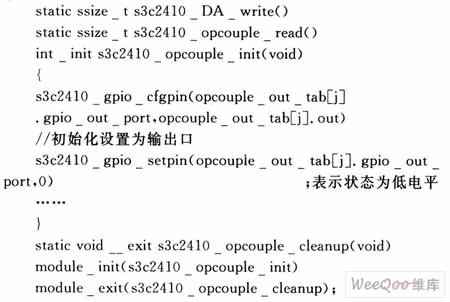

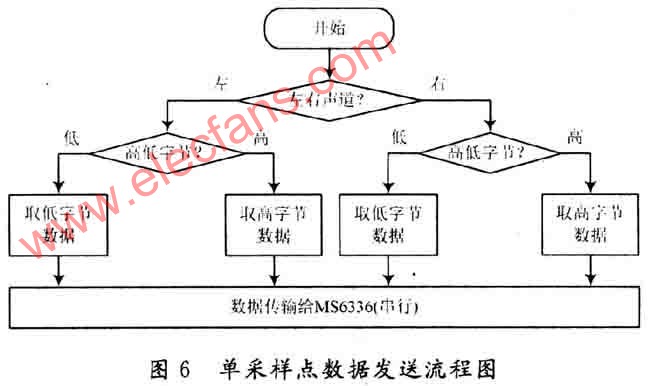

網(wǎng)絡(luò)終端能夠采集數(shù)字信號和模擬信號,數(shù)字信號可直接送入FPGA處理,模擬信號則需通過AD73311L芯片轉(zhuǎn)換為數(shù)字信號后送入FPGA處理。AD73311L工作時(shí)先進(jìn)行初始化,設(shè)定采樣率、輸入輸出增益等,再讓其工作在數(shù)據(jù)傳輸模式下就可正常工作。

AD73311L的數(shù)據(jù)采用串行方式與FPGA芯片通信,可以減少芯片間的連線。在FPGA內(nèi)部,要做串行/并行和并行/串行的變換。為了使AD73311L受CPU的控制,在SOPC Builder中通過使用“to ”功能添加了專門用于AD73311L的組件ad/da,并設(shè)置相應(yīng)的管腳與外電路相連。

4.5 軟件組成

和Nios CPU配套的軟件開發(fā)工具可在cygwin中使用。cygwin是RedHat公司開發(fā)的運(yùn)行于windows平臺下的仿linux環(huán)境。因此為Nios編寫程序并編譯鏈接的過程和通用linux下面的過程很類似。

軟件組成從邏輯上可以分為5部分,其中啟動程序Germ Monitor自成一部分,由Altera公司提供。其余4部分由設(shè)計(jì)者組織并編寫修改。基于SOPC技術(shù)的結(jié)構(gòu)如圖5所示。

由源代碼得到最終可運(yùn)行文件的過程由一種特殊的文本文件Makefile控制。Makefile文件用于指導(dǎo)源程序文件到目標(biāo)文件的編譯過程以及目標(biāo)文件鏈接成可執(zhí)行文件的過程,因此可以看成是整個(gè)軟件程序的管理文件。Makefile文件采用文本文件格式,配合Make程序創(chuàng)建最終的應(yīng)用程序。Makefile文件定義了目標(biāo)文件(target)和依靠文件之間的依賴關(guān)系,以及由依靠文件產(chǎn)生目標(biāo)文件應(yīng)該執(zhí)行的命令。

整個(gè)軟件包共有4個(gè)Makefile文件。μC/OSⅡ操作系統(tǒng)的Makefile文件位于目錄librtos32中,負(fù)責(zé)編譯操作系統(tǒng)代碼,最終產(chǎn)生操作系統(tǒng)支持庫文件librtos32.a。網(wǎng)絡(luò)通信協(xié)議lwIP部分的Makefile文件位于src目錄,負(fù)責(zé)編譯網(wǎng)絡(luò)支持部分代碼,最終生成庫文件liblwip.a。網(wǎng)絡(luò)終端應(yīng)用軟件的Makefile文件位于頂層目錄UCOSII-lwip中,它將指導(dǎo)編譯器生成庫文件liblwipapp.a。主Makefile文件也位于頂層目錄中,用于生成最終下載到電路板的可執(zhí)行程序。

4.6 系統(tǒng)的啟動

網(wǎng)絡(luò)終端采用的啟動程序?yàn)镹ios開發(fā)工具包中自帶的監(jiān)控程序Germ Monitor,略做修改。它的代碼短小,是一個(gè)小型的shell程序,配置在FPGA的片上ROM內(nèi),可以在操作系統(tǒng)運(yùn)行之前啟動系統(tǒng)。在配置硬件的時(shí)候,設(shè)置Nios的啟動地址為片上ROM的地址,系統(tǒng)上電復(fù)位時(shí)將從該地址運(yùn)行。也可以采用別的啟動方式,比如可以直接從Flash RAM驅(qū)動。對硬件的初始化檢測、硬件外圍設(shè)備工作狀態(tài)的設(shè)定都可以在啟動程序中進(jìn)行。執(zhí)行初始化之后,Germ Monitor把放置在Flash RAM中的應(yīng)用程序加載到SDRAM中,然后跳轉(zhuǎn)到應(yīng)用程序,即可按設(shè)計(jì)要求運(yùn)行以太網(wǎng)網(wǎng)絡(luò)終端的各項(xiàng)功能。

5 結(jié)語

經(jīng)過以上設(shè)計(jì),調(diào)試除錯(cuò)后,嵌入式以太網(wǎng)終端就能夠正常工作了。把兩塊這樣的終端電路板用網(wǎng)線連接到局域網(wǎng)上,分別設(shè)定其IP地址,運(yùn)行應(yīng)用軟件即可實(shí)現(xiàn)多種功能。把PC機(jī)的串口和網(wǎng)絡(luò)終端的串口互連,能夠從PC機(jī)監(jiān)視終端的工作狀態(tài)。

經(jīng)試驗(yàn),在這兩個(gè)終端間成功地實(shí)現(xiàn)了語音通信和Telnet數(shù)據(jù)通信。限于篇幅,這方面的將另文介紹。

以上的研究試驗(yàn)表明,采用SOPC技術(shù),能夠?yàn)樵O(shè)計(jì)嵌入式以太網(wǎng)網(wǎng)絡(luò)終端設(shè)備提供一種高效、靈活、低成本的解決方法,SOPC技術(shù)的多項(xiàng)特點(diǎn)使其成為嵌入式系統(tǒng)的一種富有競爭力的。

電子發(fā)燒友App

電子發(fā)燒友App

評論