在實現(xiàn)多級CIC濾波器前我們先來了解滑動平均濾波器、微分器、積分器以及梳狀濾波器原理。CIC濾波器在通信信號處理中有著重要的應(yīng)用。

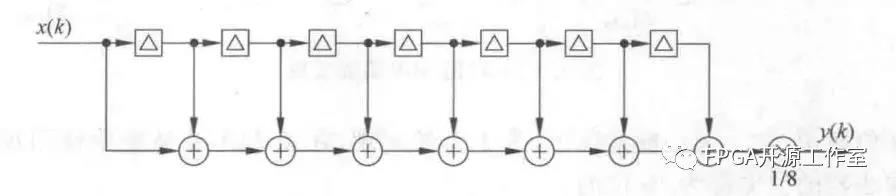

1、滑動平均濾波器

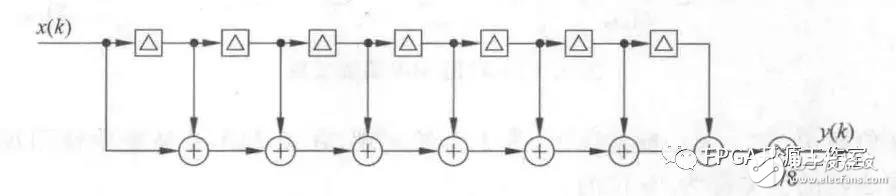

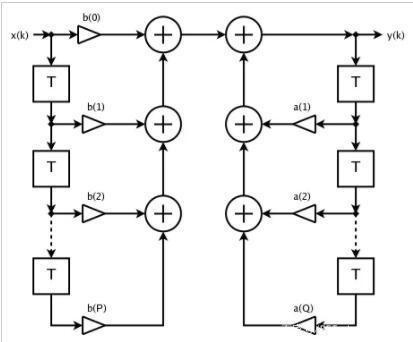

圖1 8權(quán)值滑動平均濾波器結(jié)構(gòu)

滑動平均濾波器(Moving Average Filter)的所有權(quán)值系數(shù)均為1,實現(xiàn)對信號的平滑作用,具有低通特性。

Matlab :

close all

clear all

clc

%set system parameter

fs = 1000; %The frequency of the local oscillator signal

Fs = 44100; %sampling frequency

N = 24; %Quantitative bits

L = 8192;

%Generating an input signal

t =0:1/Fs:(1/Fs)*(L-1); %Generating the time series of sampling frequencies

sc =sin(2*pi*fs*t); %a sinusoidal input signal that produces a random starting phase

%滑動平均濾波器

b =[1,1,1,1,1,1,1,1];

a =1;

sf=filter(b,a,sc).*(1/8);

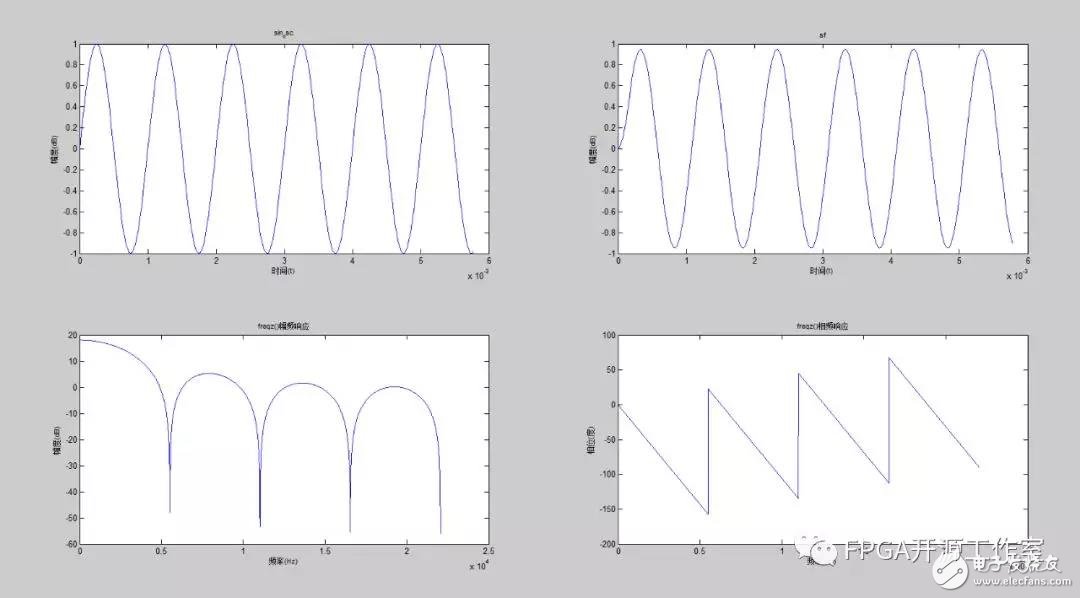

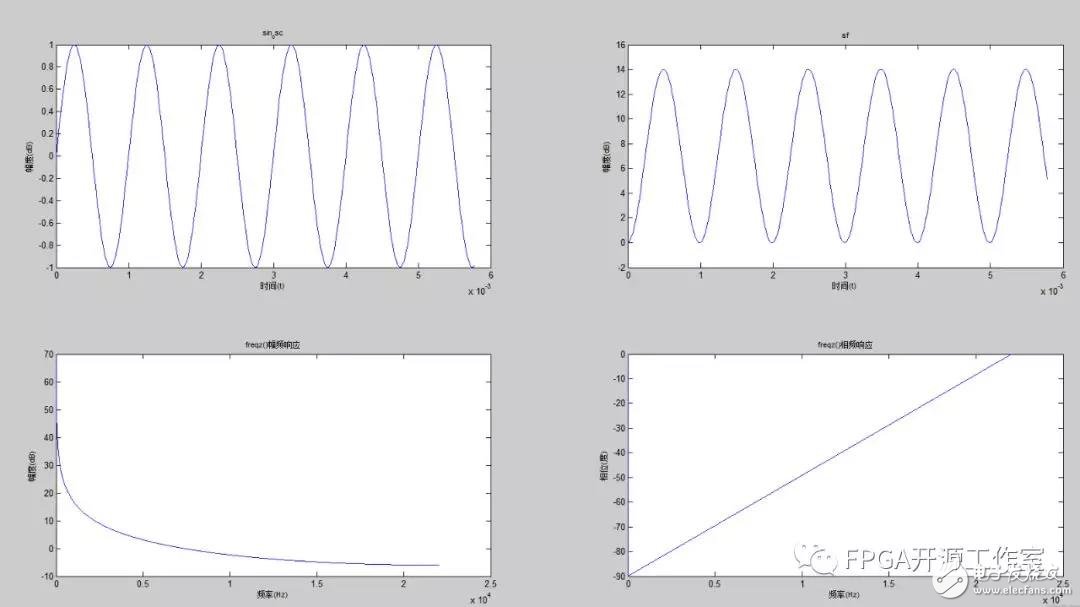

圖2 滑動平均濾波器的幅頻特征

2、微分器

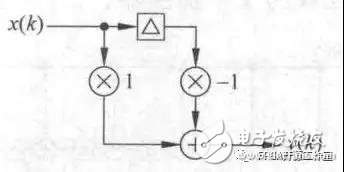

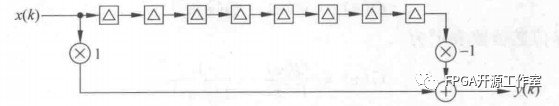

圖3 微分器結(jié)構(gòu)

微分器有1和-1兩個權(quán)值系數(shù)的濾波器,該濾波器具有簡單的高通幅頻響應(yīng)特性。

y( k ) = x( k ) - x( k - 1 )

Matlab :

close all

clear all

clc

%set system parameter

fs = 1000; %The frequency of the local oscillator signal

Fs = 44100; %sampling frequency

N = 24; %Quantitative bits

L = 8192;

%Generating an input signal

t =0:1/Fs:(1/Fs)*(L-1); %Generating the time series of sampling frequencies

sc =sin(2*pi*fs*t); %a sinusoidal input signal that produces a random starting phase

%微分濾波器

b =[1,-1];

a =1;

sf=filter(b,a,sc);

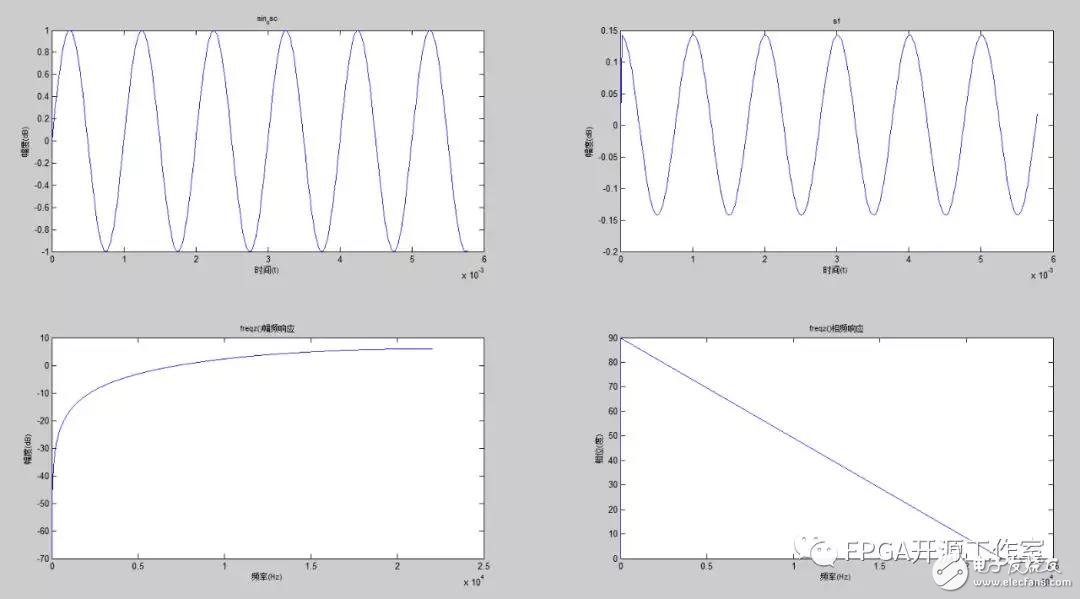

圖4 微分器幅頻響應(yīng)特征

3、積分器

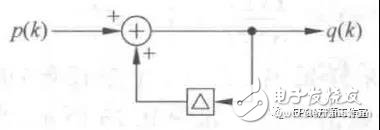

圖5 數(shù)字積分器結(jié)構(gòu)

數(shù)字積分器是只有一個系數(shù)的IIR濾波器該濾波器具有低通的濾波器的幅頻響應(yīng)特性。

q( k ) = p (k) + q( k - 1)

Matlab :

close all

clear all

clc

%set system parameter

fs = 1000; %The frequency of the local oscillator signal

Fs = 44100; %sampling frequency

N = 24; %Quantitative bits

L = 8192;

%Generating an input signal

t =0:1/Fs:(1/Fs)*(L-1); %Generating the time series of sampling frequencies

sc =sin(2*pi*fs*t); %a sinusoidal input signal that produces a random starting phase

%積分濾波器

b =1;

a =[1,-1];

sf=filter(b,a,sc);

圖6 積分器幅頻響應(yīng)特征

由圖3,圖4,和圖5分析,1khz基本未發(fā)生改變,44.1khz相對于352.8khz采樣率1khz點變得疏松。

電子發(fā)燒友App

電子發(fā)燒友App

評論