在目前我們生活當中,充滿著數量不斷增長的微型電池供電設備及系統。這些嵌入式系統必須長期使用相同的電源供電,才能降低反復出現的維護成本或避免最終用戶頻繁更換電源。及早規劃可以在優化系統實現低功耗的同時,減少對返工和/或代碼重新編寫的需求。這些考量包括:

1. 應用層面的低功耗設計;

2. 了解功耗與性能之間的利弊權衡;

3. 使用可優化功耗的軟硬件技巧。

嵌入式應用中的功耗因素

任何給定系統中的功耗都可分為兩大類:

i. 靜態功耗:靜態功耗指器件在未運行代碼、等待特定事件觸發系統喚醒至工作模式時所消耗的電源。靜態功耗的主要包括系統中流過的漏電流、模擬偏差、不能關閉的模塊以及運行RTC、看門狗定時器和中斷控制器等獨立代碼的模塊。該電流與器件的工作電壓成正比。工作電壓越高,漏電流就越大;

ii. 動態功耗:系統處于工作狀態,CPU執行程序代碼時所消耗的電源稱為動態功耗。系統的動態電流取決于工作頻率、電壓以及有關總線與電路設計的寄生電容。計算方法為:

P = V2 * f * C

V為電壓、f為工作頻率、C為輸出端的寄生電容

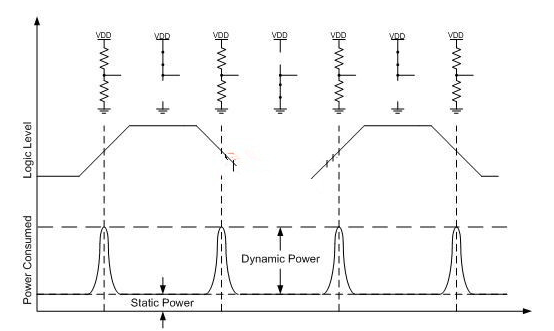

靜態與動態功耗的圖形表達:

對于任何給定的晶體管,其靜態功耗在給定電源電壓下基本上是恒定的。靜態功耗源于漏電流(CMOS電路)或偏置電流(工作模擬電路),主要取決于系統類型。

晶體管中的動態功耗發生在電壓轉換過程中。在這些轉換過程中,CMOS對會進入某個狀態,在該狀態下CMOS對的器件均部分開啟,充當電阻器,從而可形成一種分壓器電路。這種虛擬分壓器電路消耗的電源要比所定義邏輯電平下的漏電流高很多。這就是為什么動態功耗與電路中的開關頻率成正比的原因所在。因此在定義低功耗嵌入式系統時,它是最根本的注意事項之一,即要盡量減少系統的開關事件。

1. 硬件考量:

a. 電池類型:

在嵌入式應用中主要有以下類型的電池:

i. )標準堿性電池

iii. )可充電電池: 可充電堿性電池,鋰離子電池

iii. )鈕扣電池

對于各種廣泛低功耗嵌入式應用而言,為系統充電不是合理的使用案例模型。這里無需為這些應用使用可充電電池。我們來比較一下另外兩種在低功耗應用中有用的電池以及在為設計選擇電池時需考慮的因素。

標準堿性電池:標準AA電池的典型容量大約為1500mAh,不僅可輕松提供數百mA的峰值電流,而且還能夠以50mA的恒定速率放盡電流。

堿性電池能為應用提供高峰值電流,因此系統能夠在并列使用其全部專用外設(定時器與通信模塊等)的同時,在其最高時鐘頻率下運行,從而可在盡快完成各項任務后,快速進入低功耗工作模式。

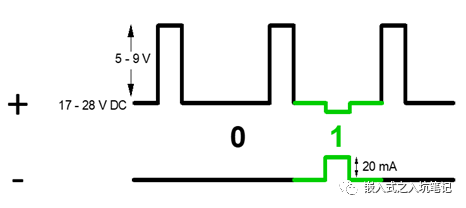

鈕扣電池:鈕扣電池具有極高的內部電阻,因此不能承受高峰值電流。在應用超過20mA的峰值電流時,即便持續時間很短,其有效電壓也會大幅下降。因此對于使用鈕扣電池供電的設計而言,強烈建議設計使用能在2V或以下電壓下工作的組件。微控制器的掉電電壓應低至能避免在鈕扣電池提供高峰值電流時系統出現意外復位的水平。

此外,我們還需要采取預防措施來降低系統所需的峰值電流。降低峰值電流的途徑包括:

● 降低CPU時鐘頻率

● 通過隨時分配負載,避免一次性啟用所有內部模塊

● 在外部組件及內部模塊未使用時,減少對它們的供電

b. 設置正確的微控制器:

要讓低功耗應用中的靜態功耗和動態功耗保持最低,最重要的是選擇具有所需外設集的微控制器,其可在所需電源模式下工作。根據需要,系統設計人員可選擇合適的微控制器,該微控制器支持低功耗模式下其應用所需的外設集。

以需要LCD較長時間工作的應用為例。通過選擇可在低功耗模式下運行該LCD的微控制器,開發人員可最大限度降低功耗。這類微控制器的典型實例就是賽普拉斯的PSoC 4,其可讓LCD顯示器以僅3uA的流耗進入深度睡眠模式。復雜應用的情況類似,我們需要進行利弊權衡,確定能以最低平均功耗完成每項任務的適當微控制器。

c. 選擇合適的無源組件:

上拉電阻器和下拉電阻器是支持接口開關及I2C器件等的常用組件。有時在低功耗設計中,這些上拉及下拉電阻器消耗的電源比系統其它部分還大。要降低其功耗,需要使用更大的電阻值。這樣可降低流經它們的電流量。但它同時會增大RC時間常數,因此會降低系統對高頻率信號的響應能力。

例如,為I2C線路使用高阻值上拉電阻器會降低I2C通信的速度,因為增大了I2C線路的壓擺率。因此這些電阻器值可決定影響最終設計的各種因素之間的權衡取舍。

同樣,在為設計選擇電容器時,應避免電解電容器,因為它們具有極高的漏電流。薄膜電容器和陶瓷電容器能以合理的成本提供超低的漏電流,可考慮用于低功耗系統設計。

d. 審慎使用I/O:

避免在系統中隨機分配控制器I/O引腳。如果引腳隨機分布在不同端口,則需要對每個端口單獨處理,這樣會增加控制它們所需的寄存器寫入數。為解決這一問題,可以按最小端口數對輸入引腳和輸出引腳進行分組,從而實現以最小的寄存器寫入數完成讀取與寫入。

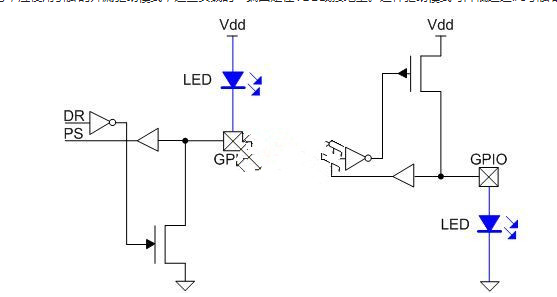

在引腳用于驅動LED和其它類似負載的地方,應使用引腳的開漏驅動模式,這些負載的一端固定在VDD或接地上。這種驅動模式可降低通過I/O引腳的漏電流,因此可降低功耗。

e. 選擇正確的外設:

在系統設計中應使用支持低功耗模式、在工作模式下支持低功耗的外設組件,以降低設計的總體功耗。

f. 審慎使用系統時鐘:

定義系統時鐘的行為有助于降低系統功耗。遵循通用系統時鐘相關設計實踐可幫助在幾乎每個系統中實現低功耗。

● 在系統中使用低頻率時鐘降低動態功耗。

● 在執行計算密集型任務時提升系統時鐘,可通過縮短完成任務的時間,降低平均功耗。

● 優先使用系統時鐘,而非外部時鐘。

● 在CPU等待通信傳輸完成時,應關閉CPU,只開啟通信模塊的時鐘。在完成該任務后,它可獲得一個中斷信號,恢復代碼執行。

g. 電流門控:

一般情況下,熱敏電阻等無源傳感器工作在分壓器模式下,因此一直都在消耗系統電流。為降低這種情況下的功耗,我們可以在通過采樣傳感器網絡獲得相關數據之前為其提供電源,并在數據采樣完成后切斷電源。這在傳感器需要定期讀取的情況下才有用。

但當傳感器必須保持工作狀態才能檢測環境中的異常現象時,CPU可在整個傳感過程中保持低功耗模式。CPU一旦收到傳感器的中斷/數據信息,就會恢復工作模式。類似邏輯可用于讀取開關狀態,以判斷它是處于開啟還是關閉狀態。

2. 固件考量:

a. 減少函數調用:

每次函數調用都將涉及多重冗余運算,比如堆棧上的添加與取出運算(用于重新加載程序的計數器和寄存器)。這些運算的每一次工作都會耗用多個時鐘周期,應盡量避免。對于簡短函數而言,函數調用可采用能夠布置內聯代碼的宏命令替換。這有助于減少CPU加載,進而降低相同運算所需的功耗。然而,每種方法都有其自身的優缺點。宏命令需要更大的存儲器,這對寫入高密度固件來說是一個問題,因為它可能會增大系統成本。

b. 為頻繁重復的輸入值使用查找表:

通常會有一部分輸入值的使用頻率大于其它輸入值。通過創建與這些輸入值對應的查找表,在遇到這些輸入其中之一時,可縮短計算時間,進而可降低功耗。

這種方法在當完成計算后需要查找值的應用中比較容易看到,比如電機應用中角度正弦與余弦的計算。在這類應用中,會有一系列頻繁遇到的值(相比之下,其它值遇到的頻率較低)。正弦值或余弦值的計算需要較長的時間,因此對于該頻繁重復的角度而言,其正弦及余弦的預計算值可存儲在查找表中。每次遇到這些角度中的一種時,處理器便可查找該表,用在此找到的值進行替代,不必計算。

c. 使用中斷,無需輪詢:

在復雜的嵌入式系統中,CPU會花大部分時間來等待某項工作的完成,然后再進入下一個步驟。當前提供的大多數SoC都提供能在無需CPU干預的情況下完成大多數任務的硬件模塊。在需要CPU干預時,它們會以中斷的方式發出信號,喚醒CPU。例如一般在采樣數據完成后,ADC會發出中斷信號。這樣就無需輪詢來自ADC的數據。因此CPU可以進入低功耗模式,只在數據準備處理時喚醒。

d. 自適應時鐘門控和電源門控

一個典型的系統會使用微控制器的多個模塊,但在任何給定時間點上,不會同時使用所有的模塊。因此可以對這些模塊的時鐘進行門控,降低這些模塊的動態功耗,從而節省電源。此外,這也有助于降低峰值電流需求,這是鈕扣電池供電設計的重要考慮因素。PSoC系列器件允許單獨禁用未使用的模塊。

來源:中國電子網

電子發燒友App

電子發燒友App

評論