手機數(shù)字基帶處理芯片中的靜態(tài)時序分析

1.引言

隨著深亞微米技術(shù)的發(fā)展,數(shù)字電路的規(guī)模已經(jīng)發(fā)展到上百萬門甚至上千萬門。工藝也從幾十μm提高到65nm甚

2010-01-23 16:36:26 813

813

靜態(tài)時序分析是檢查IC系統(tǒng)時序是否滿足要求的主要手段。以往時序的驗證依賴于仿真,采用仿真的方法,覆蓋率跟所施加的激勵有關(guān),有些時序違例會被忽略。此外,仿真方法效率非常的低,會大大延長產(chǎn)品的開發(fā)周期

2020-11-25 11:03:09 8918

8918

在fpga工程中加入時序約束的目的: 1、給quartusii 提出時序要求; 2、quartusii 在布局布線時會盡量優(yōu)先去滿足給出的時序要求; 3、STA靜態(tài)時序分析工具根據(jù)你提出的約束去判斷

2020-11-25 11:39:35 5320

5320

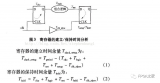

靜態(tài)時序分析包括建立時間分析和保持時間分析。建立時間設(shè)置不正確可以通過降低芯片工作頻率解決,保持時間設(shè)置不正確芯片無法正常工作。

2022-08-22 10:38:24 3289

3289 同步電路設(shè)計中,時序是一個主要的考慮因素,它影響了電路的性能和功能。為了驗證電路是否能在最壞情況下滿足時序要求,我們需要進(jìn)行靜態(tài)時序分析,即不依賴于測試向量和動態(tài)仿真,而只根據(jù)每個邏輯門的最大延遲來檢查所有可能的時序違規(guī)路徑。

2023-06-28 09:35:37 490

490

(path groups):時序路徑可以根據(jù)與路徑終點相關(guān)的時鐘進(jìn)行分類,因此每個時鐘都有一組與之相關(guān)的 時序路徑 。靜態(tài)時序分析和報告通常分別在每個時序路徑組中單獨執(zhí)行。注意: 除了上述與時鐘相關(guān)的時序

2023-04-20 16:17:54

靜態(tài)時序分析STA是什么?靜態(tài)時序分析STA的優(yōu)點以及缺點分別有哪些呢?

2021-11-02 07:51:00

靜態(tài)時序分析與邏輯設(shè)計

2017-12-08 14:49:57

本文提出新的Π模型方法,結(jié)合了門的等效電容來計算門的延時,我們的方法結(jié)合門的互連線負(fù)載的拓?fù)浣Y(jié)構(gòu)和門負(fù)載三階矩求解的方法,采用中提出的等效電容的求解公式,求出門延時計算模型,相比上述兩種方法,在靜態(tài)時序分析中更為合理。

2021-04-23 07:04:07

不能保證100%的覆蓋率。如果到了門級的仿真將非常消耗時間。 靜態(tài)時序分析靜態(tài)時序分析只能分析時序要求而不能進(jìn)行功能驗證。不需要測試向量,能比動態(tài)時序分析快地多的完成分析。靜態(tài)時序分析只能對同步電路

2021-09-04 14:26:52

三極管放大電路中的基本分析:直流靜態(tài)工作點分析。

2012-08-03 11:12:24

1. 適用范圍 本文檔理論適用于Actel FPGA并且采用Libero軟件進(jìn)行靜態(tài)時序分析(寄存器到寄存器)。2. 應(yīng)用背景 靜態(tài)時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設(shè)計

2012-01-11 11:43:06

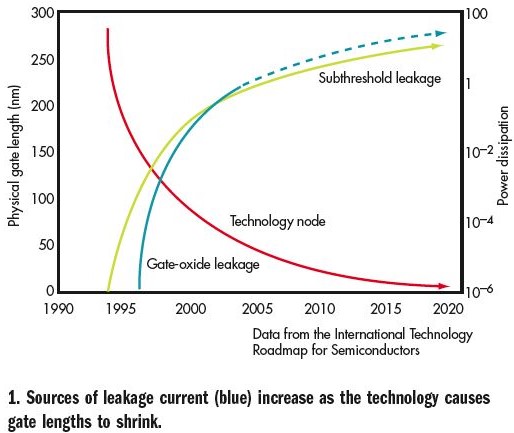

結(jié)構(gòu)中基本單元漏電流的模型并進(jìn)行了分析,最后提出降低靜態(tài)功耗的解決措施。2 FPGA的結(jié)構(gòu)和靜態(tài)功耗分布2.1 FPGA的結(jié)構(gòu)和基本組成單元一個FPGA的結(jié)構(gòu)如圖1所示。FPGA中含有規(guī)則靈活的可編程

2020-04-28 08:00:00

4個I/O Bank。在多電壓應(yīng)用環(huán)境中比較有利,并且支持熱插拔和施密特觸發(fā)器。Actel在IGLOO系列產(chǎn)品的開發(fā)過程中,對靜態(tài)功耗的主要物理來源——漏電流方面做了改進(jìn)。同時在生產(chǎn)過程中對產(chǎn)率、速度

2019-07-05 07:19:19

IAR靜態(tài)分析工具的主要特點有哪些?IAR靜態(tài)分析工具有何作用?

2022-01-27 06:54:28

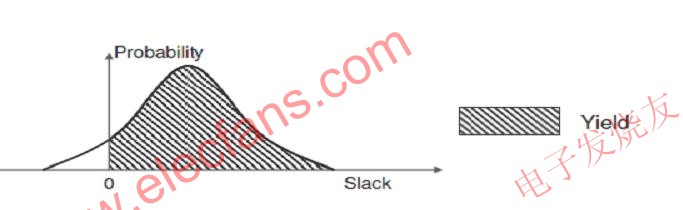

自己做了一個工程,靜態(tài)時序分析的結(jié)果CLK信號的SLACK是負(fù)值(-7.399ns),書上說該值是負(fù)值時說明時序不對,但是我感覺時序仿真的結(jié)果是對的。是不是時序仿真波形正確就不用管靜態(tài)時序分析的結(jié)果了?請高手指點

2010-03-03 23:22:24

在低功耗用電的情況下,輸出同等的電壓電流,RC降壓電源、小功率變壓器、小功率開關(guān)電源這三種電源,靜態(tài)功耗(近乎靜態(tài))最少的是哪一種?我意思是:像搖控接收器、光控器,不考慮體積、成本的情況下,用那一

2009-03-06 12:16:36

這篇博客記錄一下virtuoso中進(jìn)行CMOS反相器和靜態(tài)寄存器的電路設(shè)計以及功能仿真,適合入門。還做了版圖設(shè)計,但是自己對原理不是不清楚,在此就不記錄了。virtuoso電路設(shè)計環(huán)境基本教學(xué)一

2021-11-12 06:28:47

靜態(tài)時序分析與邏輯設(shè)計

2015-05-27 12:28:46

為什么靜態(tài)時序分析受組件(符號)名稱的影響?我在示意圖中有一個ISR,當(dāng)我把它稱為“CuttIsIr”時,靜態(tài)時序分析返回一個警告“設(shè)置時間違反”,但是當(dāng)我稱之為“UTHISISR”時,一切都

2019-07-30 10:42:26

各位好,初次使用pt對fpga進(jìn)行靜態(tài)時序分析,想請教下需要哪些文件。是不是需要:1、在ise或qutartus生成的網(wǎng)表2、SDC文件3、.db文件.db文件必須且只能從dc生成嗎,要是從.lib轉(zhuǎn)化而來,這個lib文件在fpga設(shè)計時又從哪里得到問題貌似比較多,謝謝回答

2014-12-18 16:15:12

請問動態(tài)子VI和靜態(tài)子VI的區(qū)別,通過引用調(diào)用VI和調(diào)用子VI函數(shù)的區(qū)別,謝謝。

2014-01-02 16:04:26

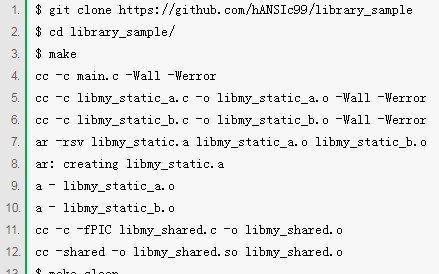

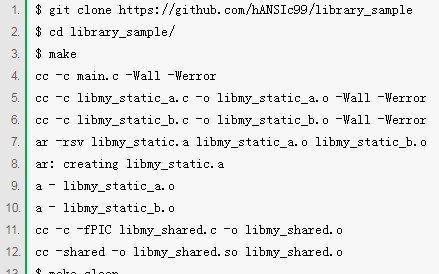

.so區(qū)分一個概念:庫是包含前綴lib以及后綴.a或者.so的一個整體庫名是去掉前綴和后綴剩下的部分四、動態(tài)庫和靜態(tài)庫的特點靜態(tài)庫的特點:1、使用靜態(tài)庫的時候,會將靜態(tài)庫的信息直接編譯到可執(zhí)行文件中2

2016-05-26 17:22:37

華為靜態(tài)時序分析與邏輯設(shè)計

2014-05-20 22:55:09

基于動、靜態(tài)電感特性的開關(guān)磁阻電機非線性磁參數(shù)模型蔣濤(北京航空航天大學(xué),北京100191)摘要:基于Matlab/Simulink.利用動態(tài)和靜態(tài)電感等磁參數(shù)建立了一種開關(guān)磁阻電機的非線性磁參數(shù)

2021-09-16 07:10:55

如何實現(xiàn)動態(tài)數(shù)碼管和靜態(tài)數(shù)碼管?

2021-09-27 07:45:17

如何采用創(chuàng)新降耗技術(shù)應(yīng)對FPGA靜態(tài)和動態(tài)功耗的挑戰(zhàn)?

2021-04-30 07:00:17

微功率LDO具有最低噪聲和靜態(tài)電流,適用于新型低噪聲,低壓差,微功率穩(wěn)壓器

2019-06-12 09:19:12

想知道28nm制程下,例如乘法器加法器的動態(tài)功耗和靜態(tài)功耗應(yīng)該去查什么資料,感覺在網(wǎng)上搜不到相關(guān)的參考資料。

2023-01-03 09:59:04

12mW。使用LTspice進(jìn)行瞬態(tài)分析之后,計算ADA4077靜態(tài)功率如圖2.181。圖2.181ADA4077靜態(tài)功耗仿真電路功率計算結(jié)果如圖2.182,ADA4077靜態(tài)功耗的平均值為10.84mW

2021-03-11 09:29:39

先大概對問題進(jìn)行一下描述,共發(fā)射極基本交流放大電路如下圖。然后可以得到上面這幅圖的直流和交流通路如下面兩幅圖。下面是問題:靜態(tài)分析就是先根據(jù)左圖確定靜態(tài)工作點,然后用右圖在確定靜態(tài)工作點的前提

2017-01-13 15:27:50

電源芯片的靜態(tài)電流是低功耗產(chǎn)品必須考慮的因素嗎

2021-10-13 08:13:15

在進(jìn)行LDO選型時,經(jīng)常會看到腳電流(GROUND CURRENT)和靜態(tài)電流(QUIESCENT CURRENT)兩個參數(shù),兩個有什么區(qū)別,在選型時應(yīng)該怎么進(jìn)行考慮啊?

2019-07-08 08:24:25

Python中的類方法、實例方法和靜態(tài)方法

2020-11-09 07:13:51

動態(tài)數(shù)碼管和靜態(tài)數(shù)碼管是怎樣區(qū)分的,求解

2019-05-06 05:21:42

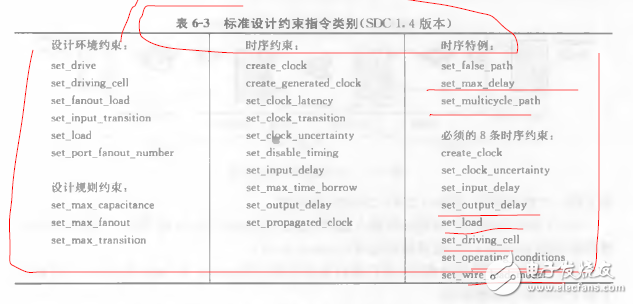

靜態(tài)時序分析(Static Timing Analysis,STA)是流程成功的關(guān)鍵環(huán)節(jié),驗證設(shè)計在時序上的正確性。STA過程中設(shè)計環(huán)境和時序約束的設(shè)定、時序結(jié)果的分析和問題解決都需要設(shè)計工程師具有

2020-09-01 16:51:01

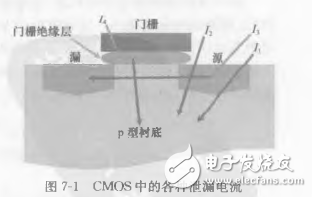

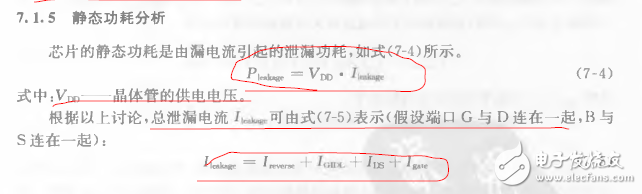

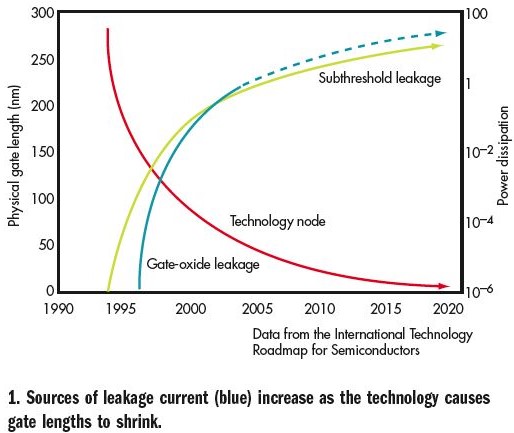

隨著工藝的發(fā)展,器件閾值電壓的降低,導(dǎo)致靜態(tài)功耗呈指數(shù)形式增長。進(jìn)入深亞微

米工藝后,靜態(tài)功耗開始和動態(tài)功耗相抗衡,已成為低功耗設(shè)計一個不可忽視的因素

2009-09-15 10:18:10 18

18 隨著工藝的發(fā)展,器件閾值電壓的降低,導(dǎo)致靜態(tài)功耗呈指數(shù)形式增長。進(jìn)入深亞微米工藝后,靜態(tài)功耗開始和動態(tài)功耗相抗衡,已成為低功耗設(shè)計一個不可忽視的因素。針對近

2009-09-15 10:18:10 26

26 靜態(tài)時序概念,目的

靜態(tài)時序分析路徑,方法

靜態(tài)時序分析工具及邏輯設(shè)計優(yōu)化

2010-07-09 18:28:18 129

129 本文首先以Synopsys公司的工具Prime Time SI為基礎(chǔ),介紹了ASIC設(shè)計中主流的時序分析方法:靜態(tài)時序分析及其基本原理和操作流程;接著分析了它與門級仿真之間的關(guān)系,提出了幾個在T

2010-08-02 16:44:16 10

10

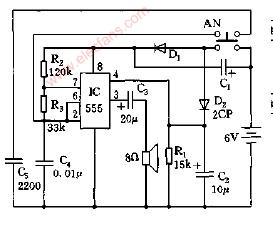

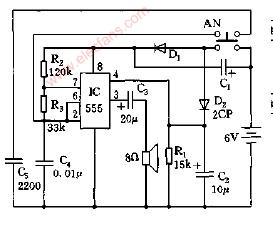

靜態(tài)微功耗雙音門笛電路圖

2009-05-21 13:33:37 595

595

靜態(tài)功耗是指一個電路維持在一個或另一個邏輯狀態(tài)時所需的功率。可以通過觀察電路中每個電阻元件的電流I和壓降V來計算每個元件的功率VI,并求和得到總功率,

2010-05-31 16:28:30 13869

13869 摘要

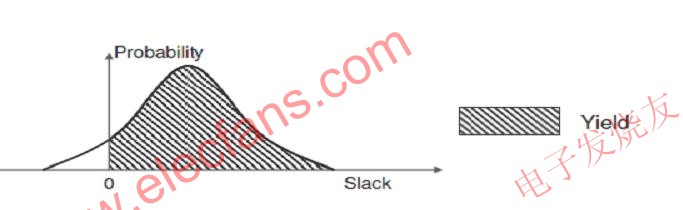

是否曾想過為什么一個設(shè)計能夠以高于設(shè)計團(tuán)隊承諾的頻率工作?為何該設(shè)計團(tuán)隊不能將這個更高的頻率當(dāng)作要實現(xiàn)的目標(biāo)?

過去,靜態(tài)時序分

2010-09-25 09:37:15 4313

4313

在制程進(jìn)入深次微米世代之后,芯片(IC)設(shè)計的高復(fù)雜度及系統(tǒng)單芯片(SOC)設(shè)計方式興起。此一趨勢使得如何確保IC質(zhì)量成為今日所有設(shè)計從業(yè)人員不得不面臨之重大課題。靜態(tài)時序

2011-05-11 16:53:43 0

0 插件板或系統(tǒng)的總功耗十分重要;系統(tǒng)內(nèi)的每一個FPGA或ASIC開始被迫達(dá)到功耗預(yù)算。出于該擔(dān)憂以及應(yīng)用高性能90納米FPGA增加靜態(tài)功耗的趨勢,Xilinx投入了大量的精力來降低Virtex-4 FPGA的

2011-05-14 18:15:53 24

24 介紹了采用STA (靜態(tài)時序分析)對FPGA (現(xiàn)場可編程門陣列)設(shè)計進(jìn)行時序驗證的基本原理,并介紹了幾種與STA相關(guān)聯(lián)的時序約束。針對時序不滿足的情況,提出了幾種常用的促進(jìn) 時序收斂的方

2011-05-27 08:58:50 70

70 在制程進(jìn)入深次微米世代之后,芯片(IC)設(shè)計的高復(fù)雜度及系統(tǒng)單芯片(SOC)設(shè)計方式興起。此一趨勢使得如何確保IC質(zhì)量成為今日所有設(shè)計從業(yè)人員不得不面臨之重大課題。靜態(tài)時序

2011-05-27 09:02:19 90

90 多態(tài)是 C++ 中面向?qū)ο蠹夹g(shù)的核心機制之一包含靜態(tài)多態(tài)和動態(tài)多態(tài)它們之間有一定的相似性但是應(yīng)用范圍不同該文論述了這種相似性并重點論述了以模板實現(xiàn)的靜態(tài)多態(tài)的應(yīng)用范圍

2011-06-29 15:41:27 41

41 討論了靜態(tài)時序分析算法及其在IC 設(shè)計中的應(yīng)用。首先,文章討論了靜態(tài)時序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時的因素。最后通過一個完整的IC 設(shè)計

2011-12-20 11:03:16 95

95 基本共射極放大電路的組成和靜態(tài)分析基本共射極放大電路的組成和靜態(tài)分析

2015-11-13 17:00:21 0

0 _靜態(tài)時序分析(Static_Timing_Analysis)基礎(chǔ)及應(yīng)用[1]。

2016-05-09 10:59:26 31

31 華為靜態(tài)時序分析與邏輯設(shè)計,基礎(chǔ)的資料,快來下載吧

2016-09-01 15:44:10 56

56 靜態(tài)時序分析基礎(chǔ)及應(yīng)用

2017-01-24 16:54:24 7

7 動態(tài)IP和靜態(tài)IP的區(qū)別在于:動態(tài)IP需要在連接網(wǎng)絡(luò)時自動獲取IP地址以供用戶正常上網(wǎng),而靜態(tài)IP是ISP在裝機時分配給用戶的IP地址,可以直接連接上網(wǎng),不需要獲取IP地址。

2017-12-27 11:14:37 70790

70790

STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設(shè)計者給定的時序限制(Timing Constraint)。以分析的方式區(qū)分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

10 功耗由靜態(tài)功耗和動態(tài)功耗組成。靜態(tài)功耗是FPGA在被編程目標(biāo)文件(.pof)編程時、但時鐘不工作的狀態(tài)下所需的功耗。數(shù)字和模擬邏輯都消耗靜態(tài)功耗。在模擬系統(tǒng)中,靜態(tài)功耗主要包括由其接口模擬電路的靜態(tài)電流決定的功耗(圖2和表)。

2019-05-16 08:04:00 7724

7724

全局區(qū)(靜態(tài)區(qū))(static)—,全局變量和靜態(tài)變量的存儲是放在一塊的,初始化的全局變量和靜態(tài)變量在一塊區(qū)域, 未初始化的全局變量、未初始化的靜態(tài)變量在相鄰的另一塊區(qū)域。 - 程序結(jié)束后有系統(tǒng)釋放

2019-05-03 14:12:00 2382

2382 靜態(tài)時序分析中的“靜態(tài)”一詞,暗示了這種時序分析是一種與輸入激勵無關(guān)的方式進(jìn)行的,并且其目的是通過遍歷所有傳輸路徑,尋找所有輸入組合下電路的最壞延遲情況。這種方法的計算效率使得它有著廣泛的應(yīng)用,盡管它也存在一些限制。

2019-11-22 07:11:00 2088

2088 靜態(tài)時序或稱靜態(tài)時序驗證,是電子工程中,對數(shù)字電路的時序進(jìn)行計算、預(yù)計的工作流程,該流程不需要通過輸入激勵的方式進(jìn)行仿真。

2019-11-22 07:09:00 2103

2103 靜態(tài)時序分析是一種驗證方法,其基本前提是同步邏輯設(shè)計(異步邏輯設(shè)計需要制定時鐘相對關(guān)系和最大路徑延時等,這個后面會說)。靜態(tài)時序分析僅關(guān)注時序間的相對關(guān)系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 靜態(tài)時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設(shè)計的要求,根據(jù)電路網(wǎng)表的拓?fù)浣Y(jié)構(gòu),計算并檢查電路中每一個DFF(觸發(fā)器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。

2019-09-01 10:45:27 2942

2942

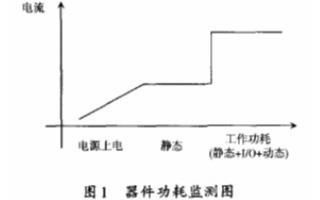

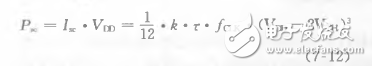

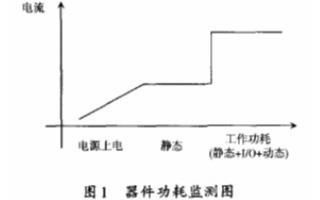

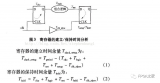

功耗一般由兩部分組成:靜態(tài)功耗和動態(tài)功耗。靜態(tài)功耗也稱為待機功耗,是指邏輯門沒有開關(guān)活動時的功率消耗,主要是由晶體管的漏電流引起,由源極到漏極的漏電流以及柵極到襯底的漏電流組成,圖1中靜態(tài)部分顯示

2020-01-16 09:46:00 7871

7871

靜態(tài)時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態(tài)時序分析,靜態(tài)時序分析不需要測試矢量,而是直接對芯片的時序進(jìn)行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 本文檔的主要內(nèi)容詳細(xì)介紹的是華為FPGA硬件的靜態(tài)時序分析與邏輯設(shè)計包括了:靜態(tài)時序分析一概念與流程,靜態(tài)時序分析一時序路徑,靜態(tài)時序分析一分析工具

2020-12-21 17:10:54 18

18 任何學(xué)FPGA的人都跑不掉的一個問題就是進(jìn)行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質(zhì),而且不需要再記復(fù)雜的公式了。

2021-01-12 17:48:08 19

19 靜態(tài)時序分析的前提就是設(shè)計者先提出要求,然后時序分析工具才會根據(jù)特定的時序模型進(jìn)行分析,給出正確是時序報告。

進(jìn)行靜態(tài)時序分析,主要目的就是為了提高系統(tǒng)工作主頻以及增加系統(tǒng)的穩(wěn)定性。對很多

2021-01-12 17:48:07 15

15 口靜態(tài)時序工具可識別的時廳敵障數(shù)要比仿真多得多,包括:建立/保持和恢復(fù)移除檢査(包括反向建立保持):最小和最大跳變:時鐘脈泩寬度和時鐘畸變;門級時鐘的瞬旴脒沙檢測;總線競爭與總線懸浮錯誤;不受

2021-01-14 16:04:03 9

9 在制程進(jìn)入深次微米世代之后,晶片(IC)設(shè)計的高復(fù)雜度及系統(tǒng)單晶片(SOC)設(shè)計方式興起。此一趨勢使得如何確保IC品質(zhì)成為今日所有設(shè)計從業(yè)人員不得不面臨之重大課題。靜態(tài)時序分析(Static

2021-01-14 16:04:02 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是時序分析的靜態(tài)分析基礎(chǔ)教程。

2021-01-14 16:04:00 14

14 了解 Linux 如何使用庫,包括靜態(tài)庫和動態(tài)庫的差別,有助于你解決依賴問題。

2021-05-06 17:05:00 1852

1852

一、前言 無論是FPGA應(yīng)用開發(fā)還是數(shù)字IC設(shè)計,時序約束和靜態(tài)時序分析(STA)都是十分重要的設(shè)計環(huán)節(jié)。在FPGA設(shè)計中,可以在綜合后和實現(xiàn)后進(jìn)行STA來查看設(shè)計是否能滿足時序上的要求。

2021-08-10 09:33:10 4767

4767

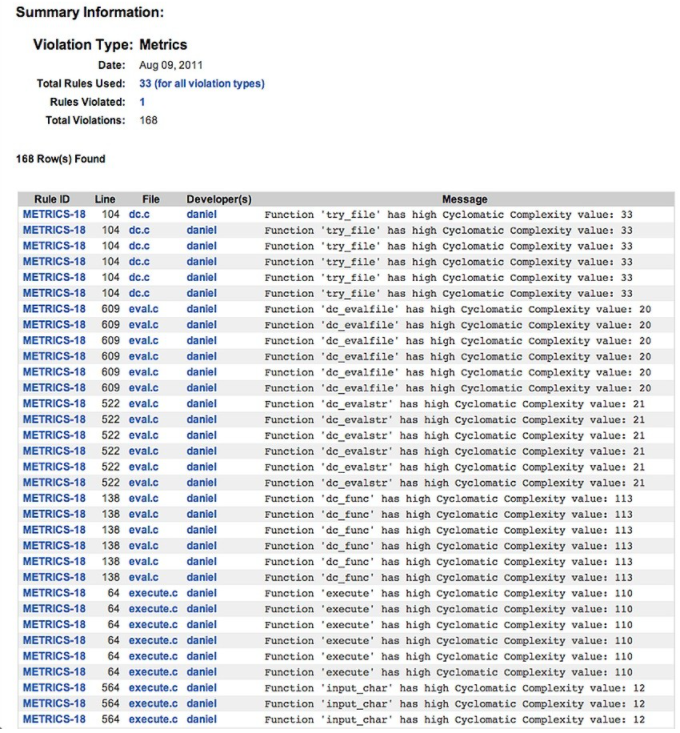

一些靜態(tài)分析模式可以在運行時檢測缺陷。如果嵌入式目標(biāo)可以容納開銷,則組織應(yīng)執(zhí)行運行時靜態(tài)分析以完善其預(yù)防策略。運行時靜態(tài)分析在代碼實際運行時檢測錯誤,這使軟件工程師能夠使用真實數(shù)據(jù)測試真實路徑。

2022-06-19 07:23:00 733

733

另一種是手動的方式,在大型設(shè)計中,設(shè)計人員一般會采用手動方式進(jìn)行靜態(tài)時序分析。手動分析方式既可以通過菜單操作(個人理解:通過鼠標(biāo)點擊和鍵盤輸入)進(jìn)行分析,也可以采用Tcl腳本(工具控制語言,個人理解運用代碼控制)進(jìn)行約束和分析。

2022-08-19 17:10:25 1354

1354 靜態(tài)時序分析簡稱STA,它是一種窮盡的分析方法,它按照同步電路設(shè)計的要求,根據(jù)電路網(wǎng)表的拓?fù)浣Y(jié)構(gòu),計算并檢查電路中每一個DFF(觸發(fā)器)的建立和保持時間以及其他基于路徑的時延要求是否滿足。STA作為

2022-09-27 14:45:13 1808

1808 簡單來說,靜態(tài)分析是在不執(zhí)行代碼的情況下檢查源代碼和二進(jìn)制代碼的過程,通常用于查找bug的前期準(zhǔn)備或評估代碼質(zhì)量。與需要運行程序的動態(tài)分析(例如Parasoft Insure ++)不同,靜態(tài)分析可以直接分析源代碼而不需要執(zhí)行源代碼。

2022-11-01 11:35:09 2510

2510 所謂靜態(tài)鏈接,就是把庫實現(xiàn)的代碼整合到最終的二進(jìn)制文件中,這樣的二進(jìn)制文件會比較大,因為里面既包含了自己寫的代碼,又包含了調(diào)用的庫的代碼。

2023-02-08 14:17:12 612

612 共射極放大電路的靜態(tài)分析是指對該電路在直流偏置下的電性能進(jìn)行分析。靜態(tài)分析的目的是確定晶體管的靜態(tài)工作點,即晶體管在偏置電路下的電流和電壓值,從而保證電路在穩(wěn)定工作的狀態(tài)下能夠有效放大輸入信號。

2023-02-27 11:10:31 7327

7327 任何學(xué)FPGA的人都跑不掉的一個問題就是進(jìn)行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,終于找到了一種很簡單的解讀辦法,可以看透

2023-03-14 19:10:03 443

443 任何學(xué)FPGA的人都跑不掉的一個問題就是進(jìn)行靜態(tài)時序分析。靜態(tài)時序分析的公式,老實說很晦澀,而且總能看到不同的版本,內(nèi)容又不那么一致,為了徹底解決這個問題,我研究了一天,終于找到了一種很簡單的解讀辦法,可以看透它的本質(zhì),而且不需要再記復(fù)雜的公式了。

2023-05-29 10:24:29 348

348

在開發(fā)安全、可靠和合規(guī)的軟件時,完備靜態(tài)分析是一種有益的實踐。本篇文章中,我們將討論完備分析與靜態(tài)分析的不同之處,為什么它很重要,以及完備靜態(tài)代碼分析的工作原理。

2022-11-11 10:16:26 369

369

靜態(tài)時序分析(Static Timing Analysis, 以下統(tǒng)一簡稱 **STA** )是驗證數(shù)字集成電路時序是否合格的一種方法,其中需要進(jìn)行大量的數(shù)字計算,需要依靠工具進(jìn)行,但是我們必須了解其中的原理。

2023-06-27 11:43:22 523

523

引言 在同步電路設(shè)計中,時序是一個非常重要的因素,它決定了電路能否以預(yù)期的時鐘速率運行。為了驗證電路的時序性能,我們需要進(jìn)行 靜態(tài)時序分析 ,即 在最壞情況下檢查所有可能的時序違規(guī)路徑,而不需要測試

2023-06-28 09:38:57 714

714

??本文主要介紹了靜態(tài)時序分析 STA。

2023-07-04 14:40:06 528

528

靜態(tài)分析可幫助面臨壓力的開發(fā)團(tuán)隊。高質(zhì)量的版本需要按時交付。需要滿足編碼和合規(guī)性標(biāo)準(zhǔn)。錯誤不是一種選擇。

這就是開發(fā)團(tuán)隊使用靜態(tài)分析工具/源代碼分析工具的原因。在這里,我們將討論靜態(tài)分析和使用靜態(tài)代碼分析器的好處,以及靜態(tài)分析的局限性。

2023-07-19 12:09:38 845

845

CMOS靜態(tài)功耗是指在CMOS電路中,當(dāng)輸入信號不變時,電路中的電流仍然存在,這種電流被稱為靜態(tài)電流,也被稱為漏電流。CMOS靜態(tài)功耗是指在這種情況下,電路中的功率消耗。

2023-07-21 15:47:03 1523

1523

庫是一種可執(zhí)行的二進(jìn)制文件,是編譯好的代碼。使用庫可以提高開發(fā)效率。在 Linux 下有靜態(tài)庫和動態(tài)庫。 靜態(tài)庫在程序編譯的時候會被鏈接到目標(biāo)代碼里面。所以程序在運行的時候不再需要靜態(tài)庫了。因此編譯

2023-07-27 11:00:10 526

526 基本放大電路中靜態(tài)值和靜態(tài)工作點一樣嗎?? 基本放大電路是指通常用于信號放大和增強的電路,它是電子工程中最基本的電路之一。在基本放大電路中,靜態(tài)值和靜態(tài)工作點都是非常重要的概念,但它們并不是完全相同

2023-09-13 14:17:50 1054

1054 類型。靜態(tài)電路主要指的是電子設(shè)備中沒有時序要求的電路,例如門電路、反相器電路、仲裁電路等;而動態(tài)電路指的是需要時序控制的電路,其主要包括計數(shù)器、觸發(fā)器、存儲器等。動態(tài)電路的主要特點是速度快、功耗低、產(chǎn)生噪聲和抖動

2023-09-17 10:47:32 2795

2795 有源負(fù)載和靜態(tài)負(fù)載的區(qū)別是什么?? 有源負(fù)載和靜態(tài)負(fù)載是電子領(lǐng)域中兩種常見的負(fù)載。在電路中,負(fù)載是指電路輸出能力的消耗者。在這篇文章中,我們將介紹有源負(fù)載和靜態(tài)負(fù)載之間的區(qū)別。 1. 有源負(fù)載

2023-09-18 18:20:23 819

819 靜態(tài)功耗也叫靜態(tài)電流,是指芯片在靜止?fàn)顟B(tài)下的電流或者是指芯片在不受外界因素影響下自身所消耗的電流。靜態(tài)功耗是衡量芯片功耗與效率地重要指標(biāo)。

2023-09-22 16:31:45 319

319

為什么需要芯片靜態(tài)功耗測試?如何使用芯片測試工具測試芯片靜態(tài)功耗? 芯片靜態(tài)功耗測試是評估芯片功耗性能和優(yōu)化芯片設(shè)計的重要步驟。在集成電路設(shè)計中,靜態(tài)功耗通常是指芯片在不進(jìn)行任何操作時消耗的功率

2023-11-10 15:36:27 1117

1117

電子發(fā)燒友App

電子發(fā)燒友App

評論