語音識別技術(shù)的發(fā)展 與機器

進行語音交流,讓它聽明白你在說什么。語音識別技術(shù)將人類這一曾經(jīng)的夢想變成了現(xiàn)實。語音識別就好比機器的聽覺系統(tǒng),該技術(shù)讓機器通過識別和理解,把語音信號轉(zhuǎn)變?yōu)橄鄳奈谋净蛎?/div>

2018-01-06 07:48:00 20997

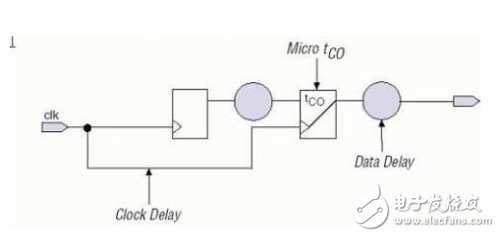

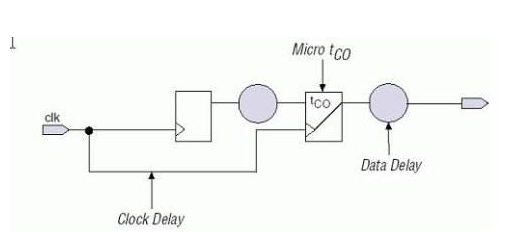

20997 時序約束的目的就是告訴工具當前的時序狀態(tài),以讓工具盡量優(yōu)化時序并給出詳細的分析報告。一般在行為仿真后、綜合前即創(chuàng)建基本的時序約束。Vivado使用SDC基礎(chǔ)上的XDC腳本以文本形式約束。以下討論如何進行最基本時序約束相關(guān)腳本。

2022-03-11 14:39:10 8731

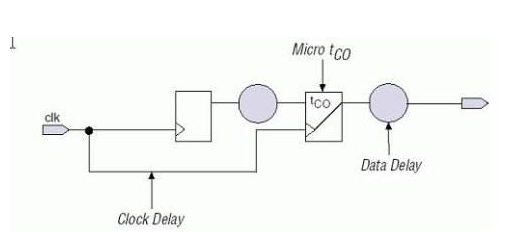

8731 在高速系統(tǒng)中FPGA時序約束不止包括內(nèi)部時鐘約束,還應包括完整的IO時序約束和時序例外約束才能實現(xiàn)PCB板級的時序收斂。因此,F(xiàn)PGA時序約束中IO口時序約束也是一個重點。只有約束正確才能在高速情況下保證FPGA和外部器件通信正確。

2022-09-27 09:56:09 1382

1382 在FPGA設(shè)計中,時序約束的設(shè)置對于電路性能和可靠性都至關(guān)重要。在上一篇的文章中,已經(jīng)詳細介紹了FPGA時序約束的基礎(chǔ)知識。

2023-06-06 18:27:13 6212

6212

在FPGA設(shè)計中,時序約束對于電路性能和可靠性非常重要。在上一篇的文章中,已經(jīng)詳細介紹了FPGA時序約束的主時鐘約束。

2023-06-12 17:29:21 1229

1229 FPGA中時序約束是設(shè)計的關(guān)鍵點之一,準確的時鐘約束有利于代碼功能的完整呈現(xiàn)。進行時序約束,讓軟件布局布線后的電路能夠滿足使用的要求。

2023-08-14 17:49:55 711

711

前面講解了時序約束的理論知識FPGA時序約束理論篇,本章講解時序約束實際使用。

2023-08-14 18:22:14 842

842

此版只討論時序約束約束理論約束方法約束結(jié)果時鐘約束(Clock Specification): 約束所有時鐘(包括你的設(shè)計中特有的時鐘)對準確的時序分析結(jié)果而言是必不可少的。Quartus II

2013-05-16 18:51:50

當邏輯行為以默認的方式不能正確的定時邏輯行為,想以不同的方式處理時序時,必須使用時序例外命令。1. 多周期路徑約束指明將數(shù)據(jù)從路徑開始傳播到路徑結(jié)束時,所需要的時鐘周期

2018-09-21 12:55:34

vivado默認計算所有時鐘之間的路徑,通過set_clock_groups命令可禁止在所標識的時鐘組之間以及一個時鐘組內(nèi)的時鐘進行時序分析。 1.異步時鐘組約束聲明兩時鐘組之間為異步關(guān)系,之間不進行時序

2018-09-21 12:40:56

在進行數(shù)字電路系統(tǒng)的設(shè)計時,時序是否能夠滿足要求直接影響著電路的功能和性能。本文首先講解了時序分析中重要的概念,并將這些概念同數(shù)字系統(tǒng)的性能聯(lián)系起來,最后結(jié)合FPGA的設(shè)計指出時序約束的內(nèi)容和時序

2020-08-16 07:25:02

好的時序是設(shè)計出來的,不是約束出來的時序就是一種關(guān)系,這種關(guān)系的基本概念有哪些?這種關(guān)系需要約束嗎?各自的詳細情況有哪些?約束的方法有哪些?這些約束可分為幾大類?這種關(guān)系僅僅通過約束來維持嗎?1

2018-08-01 16:45:40

爆款資料推薦ADI《模擬對話》技術(shù)期刊,第1期至第50期都在這里了https://ezchina.analog.com/thread/14417ADI系統(tǒng)方案精選合集(2016)https

2016-10-28 18:04:57

DAYU200資料需求集中討論貼,有需要什么資料都在這里提~我們會統(tǒng)計,并整理輸出給到大家~

2022-03-04 12:32:03

電子發(fā)燒友網(wǎng)ETD第14期SDR源同步接口時序約束方法-會前交流電子發(fā)燒友網(wǎng)ETD第14期SDR源同步接口時序約束方法-演講電子發(fā)燒友網(wǎng)ETD第14期SDR源同步接口時序約束方法-提問

2015-01-17 16:27:32

Incremental Compilation。這是造成上述兩種方法容易混淆的原因。5. 核心頻率約束+時序例外約束+I/O約束+寄存器布局約束 寄存器布局約束是精確到寄存器或LE一級的細粒度布局約束。設(shè)計者

2017-12-27 09:15:17

控。從最近一段時間工作和學習的成果中,我總結(jié)了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括

2016-06-02 15:54:04

的方法一般有四個步驟:時序分析→時序約束→時序報告→時序收斂。

為什么要進行時序分析?

信號在系統(tǒng)中傳輸時由于經(jīng)過一些邏輯器件和PCB上的走線會造成一定的邏輯延時和路徑延時,如果系統(tǒng)要求信號

2011-09-23 10:26:01

,F(xiàn)PGA產(chǎn)生的數(shù)據(jù)data_out和時鐘clk_out的理想波形是時鐘上升沿鎖存到穩(wěn)定可靠的數(shù)據(jù)。(特權(quán)同學,版權(quán)所有)圖8.26 源同步接口寄存器和時序波形關(guān)系下面我們來探討如何對這個設(shè)計進行約束。首先

2015-07-30 22:07:42

的工程師朋友們...在互動環(huán)節(jié)工程師們積極提問并獲得電子發(fā)燒友贈送的技術(shù)書籍最后來一張全家福大合照,在這里沒有新老工程師之分,大家都是FPGA的愛好者,也都是愛學習愛充電的人士,最后祝賀我們本次沙龍圓滿結(jié)束

2014-12-31 14:25:41

在進行FPGA的設(shè)計時,經(jīng)常會需要在綜合、實現(xiàn)的階段添加約束,以便能夠控制綜合、實現(xiàn)過程,使設(shè)計滿足我們需要的運行速度、引腳位置等要求。通常的做法是設(shè)計編寫約束文件并導入到綜合實現(xiàn)工具,在進行

2023-09-21 07:45:57

,因此,為了避免這種情況,必須對fpga資源布局布線進行時序約束以滿足設(shè)計要求。因為時鐘周期是預先知道的,而觸發(fā)器之間的延時是未知的(兩個觸發(fā)器之間的延時等于一個時鐘周期),所以得通過約束來控制觸發(fā)器之間的延時。當延時小于一個時鐘周期的時候,設(shè)計的邏輯才能穩(wěn)定工作,反之,代碼會跑飛。

2018-08-29 09:34:47

有沒有哪位大神對ISE的時序約束比較熟悉,尤其是多周期約束這一塊。在Quartus中使用比較簡單,而且相關(guān)資料也比較多,但是ISE中的資料好像不是那么多,而且也沒有針對具體例子進行分析。官網(wǎng)上給出

2015-04-30 09:52:05

正在進行著一種經(jīng)營,一種為合作伙伴創(chuàng)造利益的經(jīng)營。因為在這里,您得到的是第一手信息,也許您此刻正在結(jié)合這些信息,運籌您的宏圖偉業(yè)。那就請您登陸我們的網(wǎng)站,我們會以最快的速度,在最短的時間內(nèi)把您所需要的無限商機送給您。

2009-06-14 22:37:08

請教大牛,在用quartus II 9.1時進行時序約束時一按鬧鐘按鈕打開time quest界面時程序就卡死了,不知道哪里出問題了,請教大牛應該怎莫辦才好

2019-03-06 06:35:15

進行時序分析,例如:1.如何檢查輸入或輸出的時間?2.如何檢查源時鐘和目標時鐘的某些路徑是否為特定時鐘?如果有人可以在這里發(fā)布你總是使用的常用命令,或者推薦一些教程,那就太棒了。提前致謝。以上

2019-03-11 13:41:27

轉(zhuǎn)自:VIVADO時序分析練習時序分析在FPGA設(shè)計中是分析工程很重要的手段,時序分析的原理和相關(guān)的公式小編在這里不再介紹,這篇文章是小編在練習VIVADO軟件時序分析的筆記,小編這里

2018-08-22 11:45:54

大部分的時序分析和約束都寫在這里了。 一、基本時序路徑1、clock-to-setup周期約束跨時鐘域約束: (1)當源觸發(fā)器和目標觸發(fā)器的驅(qū)動時鐘不同,且時鐘的占空比不是50

2017-03-09 14:43:24

控。 下文總結(jié)了幾種進行時序約束的方法。按照從易到難的順序排列如下: 0. 核心頻率約束 這是最基本的,所以標號為0。1. 核心頻率約束+時序例外約束 時序例外約束包括FalsePath

2017-10-20 13:26:35

求助啊!!!我在這里下的好的文件都有損壞的現(xiàn)象,無論是zip還是pdf,都打不開,而且一般都顯示文件很小,只有1M多?這是為什么?

2012-03-30 22:39:23

求助啊!!!我在這里下的好的文件都有損壞的現(xiàn)象,無論是zip還是pdf,都打不開,而且一般都顯示文件很小,只有1M多?這是為什么?

2012-03-30 22:42:23

你們想要的全景影像系統(tǒng)開發(fā)資料,都在這里啦![hide][/hide]

2017-03-17 14:08:17

`你要的自供電技術(shù)都在這里掃一掃吧[qq]1098104553[/qq]`

2016-12-08 17:52:15

最高頻露。下面說一下在ise環(huán)境下進行時序約束的方法。 通過約束編輯器的文本編輯窗口,可以采用以下兩種方式的UCF語句來做時鐘約束。 (1)period_item PERIOD=period{HIGH

2015-02-03 14:13:04

系統(tǒng)設(shè)計教程》(第三版)。在這一階段,你要做到的是:給你一個指標要求或者時序圖,你能用HDL設(shè)計電路去實現(xiàn)它。這里你需要一塊開發(fā)板,可以選Altera的cyclone IV系列,或者Xilinx

2020-10-21 15:07:39

關(guān)于電容的一些基礎(chǔ)知識都在這里

2021-04-23 07:12:10

關(guān)于高速ADC的選擇與應用你想要的都在這里

2021-05-25 06:57:38

邏輯。而對其進行時序分析時,一般都以時鐘為參考的,因此一般主要分析上半部分。在進行時序分析之前,需要了解時序分析的一些基本概念,如時鐘抖動、時鐘偏斜(Tskew)、建立時間(Tsu)、保持時間(Th)等

2018-04-03 11:19:08

學習中遇到問題可以在這里發(fā)帖請教嗎?會不會有及時準確的答案?因為有的問題還比較難描述,不方便用百度搜索。大家遇到問題怎么處理?

2014-09-25 20:57:47

問一下啊,在寫時序約束的時候,如何根據(jù)設(shè)計的要求進行時序上的約束啊,看了好多網(wǎng)上的資料,說的都是有關(guān)約束的一些原理。有沒有那位大俠給個設(shè)計實例啊!

2023-04-23 11:42:16

本帖最后由 億道集團 于 2019-4-24 12:54 編輯

小伙伴,教你如何合并License,趕緊收藏哦!

2016-12-28 15:56:21

本帖最后由 儀商城客服 于 2017-12-6 11:07 編輯

儀商導讀:諧波干擾是電源運行過程中常見的現(xiàn)象,工程師往往需要不斷的升級PFC電路來改進自家的電源產(chǎn)品,那么,怎樣定位電源運行時

2017-12-06 11:04:03

清華出品:最易懂的AI芯片報告!人才技術(shù)趨勢都在這里 https://mp.weixin.qq.com/s/kDZFtvYYLLqJSED_0V1RZA 2010 年以來, 由于大數(shù)據(jù)產(chǎn)業(yè)的發(fā)展

2021-07-23 09:19:56

我是一個FPGA初學者,關(guān)于時序約束一直不是很明白,時序約束有什么用呢?我只會全局時鐘的時序約束,如何進行其他時序約束呢?時序約束分為哪幾類呢?不同時序約束的目的?

2012-07-04 09:45:37

大家好,這個電感在這里是濾波嗎?如果是,那么可以放在7805后面濾波嗎

2019-03-05 20:13:46

難得看到一篇好的PCB布局文章,趕緊收藏

2015-04-03 18:27:39

時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎(chǔ)常用時序概念QuartusII中的時序分析報告

設(shè)置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 時序約束用戶指南包含以下章節(jié): ?第一章“時序約束用戶指南引言” ?第2章“時序約束的方法” ?第3章“時間約束原則” ?第4章“XST中指定的時序約束” ?第5章“Synplify中指定的時

2010-11-02 10:20:56 0

0 FPGA時序約束方法很好地資料,兩大主流的時序約束都講了!

2015-12-14 14:21:25 19

19 Xilinx時序約束設(shè)計,有需要的下來看看

2016-05-10 11:24:33 18

18 每次iOS系統(tǒng)更新前都會有一大推發(fā)燒友爆料新系統(tǒng)的特點,在這里將 iOS 10.3可能出現(xiàn)的新功能進行了匯總:

2017-02-06 14:04:47 2441

2441 偏移約束。 這里先說一下周期約束:周期約束是為了達到同步組件的時序要求。如果相鄰同步原件相位相反,那么延遲就會是時鐘約束值的一半,一般不要同時使用上升沿和下降沿。注意:在實際工程中,附加的約束時間為期望值的

2017-02-09 02:56:06 605

605 三星Galaxy S8/S8+國行版將于今晚8點整在北京正式發(fā)布,三星S8發(fā)布會直播進行時,現(xiàn)在有二十萬人在看同步直播。你想知道的配置、價格、真機,都在這里!

2017-05-18 20:29:18 907

907 關(guān)于新能源汽車與自動駕駛,你想知道的都在這里。

2017-08-02 09:57:33 2444

2444 作時序和布局約束是實現(xiàn)設(shè)計要求的關(guān)鍵因素。本文是介紹其使用方法的入門讀物。 完成 RTL 設(shè)計只是 FPGA 設(shè)計量產(chǎn)準備工作中的一部分。接下來的挑戰(zhàn)是確保設(shè)計滿足芯片內(nèi)的時序和性能要求。為此

2017-11-17 05:23:01 2416

2416

一個好的FPGA設(shè)計一定是包含兩個層面:良好的代碼風格和合理的約束。時序約束作為FPGA設(shè)計中不可或缺的一部分,已發(fā)揮著越來越重要的作用。毋庸置疑,時序約束的最終目的是實現(xiàn)時序收斂。時序收斂作為

2017-11-17 07:54:36 2326

2326

作為賽靈思用戶論壇的定期訪客(見 ),我注意到新用戶往往對時序收斂以及如何使用時序約束來達到時序收斂感到困惑。為幫助 FPGA設(shè)計新手實現(xiàn)時序收斂,讓我們來深入了解時序約束以及如何利用時序約束實現(xiàn)

2017-11-24 19:37:55 4903

4903

詳細講解了xilinx的時序約束實現(xiàn)方法和意義。包括:初級時鐘,衍生時鐘,異步時終域,多時終周期的講解

2018-01-25 09:53:12 6

6 最詳細的電氣基礎(chǔ)知識都在這里。

2018-03-28 16:03:20 27344

27344

在簡單電路中,當頻率較低時,數(shù)字信號的邊沿時間可以忽略時,無需考慮時序約束。但在復雜電路中,為了減少系統(tǒng)中各部分延時,使系統(tǒng)協(xié)同工作,提高運行頻率,需要進行時序約束。通常當頻率高于50MHz時,需要考慮時序約束。

2018-03-30 13:42:59 14208

14208

好的時序是設(shè)計出來的,不是約束出來的 時序就是一種關(guān)系,這種關(guān)系的基本概念有哪些? 這種關(guān)系需要約束嗎? 各自的詳細情況有哪些? 約束的方法有哪些? 這些約束可分為幾大類? 這種關(guān)系僅僅通過約束

2018-08-06 15:08:02 400

400 從最近一段時間工作和學習的成果中,我總結(jié)了如下幾種進行時序約束的方法。按照從易到難的順序排列如下:

2018-08-07 14:14:00 13907

13907

了解時序約束向?qū)绾斡糜凇巴耆?b class="flag-6" style="color: red">約束您的設(shè)計。

該向?qū)ё裱璘ltraFast設(shè)計方法,定義您的時鐘,時鐘交互,最后是您的輸入和輸出約束。

2018-11-29 06:47:00 2698

2698

,這讓我真真感覺是撿到寶了!獨樂樂不如眾樂樂,我覺得有必要和大家推廣一下,讓大家也享受一下能躺在家里賺錢的快感!今天的主角:聚游公社!顧名思義,這是一個匯集了很多游戲的一站式體驗社區(qū)!在這里,你能玩到你能想象

2018-12-20 17:58:00 228

228 MLCC缺貨,能用鉭電容替代嗎?最靠譜兒的回答在這里~

2019-07-02 11:40:48 3698

3698 浦東新區(qū)將建成一批新一代人工智能產(chǎn)業(yè)創(chuàng)新應用“試驗場”,更多人工智能創(chuàng)新產(chǎn)品、平臺和服務將在這里先行先試。

2019-07-18 16:39:54 415

415 關(guān)于5G手機,你想知道的都在這里了,快收藏

2019-08-27 16:25:46 2315

2315 首先來看什么是時序約束,泛泛來說,就是我們告訴軟件(Vivado、ISE等)從哪個pin輸入信號,輸入信號要延遲多長時間,時鐘周期是多少,讓軟件PAR(Place and Route)后的電路能夠

2020-01-28 17:34:00 3077

3077

上面我們講的都是xdc文件的方式進行時序約束,Vivado中還提供了兩種圖形界面的方式,幫我們進行時序約束:時序約束編輯器(Edit Timing Constraints )和時序約束向?qū)В–onstraints Wizard)。兩者都可以在綜合或?qū)崿F(xiàn)后的Design中打開。

2020-03-08 17:17:00 19067

19067

靜態(tài)時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態(tài)時序分析,靜態(tài)時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 對自己的設(shè)計的實現(xiàn)方式越了解,對自己的設(shè)計的時序要求越了解,對目標器件的資源分布和結(jié)構(gòu)越了解,對EDA工具執(zhí)行約束的效果越了解,那么對設(shè)計的時序約束目標就會越清晰,相應地,設(shè)計的時序收斂過程就會更可控。

2021-01-11 17:44:44 8

8 噪聲可以是隨機信號或重復信號,內(nèi)部或外部產(chǎn)生,電壓或電流形式帶或?qū)拵В哳l或低頻。(在這里,我們將噪聲定義為任何在運放輸出端的無用信號)

噪聲通常包括器件的固有噪聲和外部噪聲,固有噪聲包括:熱噪聲

2021-02-03 07:21:35 31

31 電子發(fā)燒友網(wǎng)為你提供詳解直線電機,你要知道的都在這里資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-07 08:41:51 18

18 電子發(fā)燒友網(wǎng)為你提供一張思維導圖介紹PCB散熱,你需要了解的都在這里資料下載的電子資料下載,更有其他相關(guān)的電路圖、源代碼、課件教程、中文資料、英文資料、參考設(shè)計、用戶指南、解決方案等資料,希望可以幫助到廣大的電子工程師們。

2021-04-29 08:41:04 33

33 時序沖突的概率變大以及電路的穩(wěn)定性降低,為此必須進行時序、面積和負載等多方面的約束。

2021-06-15 11:24:05 2874

2874

7大主流單片機優(yōu)缺點分析,一文打盡趕緊收藏!

2021-11-15 13:21:03 13

13 上一篇《FPGA時序約束分享01_約束四大步驟》一文中,介紹了時序約束的四大步驟。

2022-03-18 10:29:28 1323

1323

很多讀者對于怎么進行約束,約束的步驟過程有哪些等,不是很清楚。明德?lián)P根據(jù)以往項目的經(jīng)驗,把時序約束的步驟,概括分成四大步

2022-07-02 10:56:45 4974

4974

本文章探討一下FPGA的時序input delay約束,本文章內(nèi)容,來源于明德?lián)P時序約束專題課視頻。

2022-07-25 15:37:07 2379

2379

時序約束是我們對FPGA設(shè)計的要求和期望,例如,我們希望FPGA設(shè)計可以工作在多快的時鐘頻率下等等。因此,在時序分析工具開始對我們的FPGA設(shè)計進行時序分析前,我們必須為其提供相關(guān)的時序約束信息

2022-12-28 15:18:38 1891

1891 本章節(jié)主要介紹一些簡單的時序約束的概念。

2023-03-31 16:37:57 928

928

很多人詢問關(guān)于約束、時序分析的問題,比如:如何設(shè)置setup,hold時間?如何使用全局時鐘和第二全局時鐘(長線資源)?如何進行分組約束?如何約束某部分組合邏輯?如何通過約束保證異步時鐘域之間

2023-05-29 10:06:56 372

372

前面幾篇文章已經(jīng)詳細介紹了FPGA時序約束基礎(chǔ)知識以及常用的時序約束命令,相信大家已經(jīng)基本掌握了時序約束的方法。

2023-06-23 17:44:00 1260

1260

您對于儲能連接器的生產(chǎn)流程了解多少,下面我們一同來認識一下儲能連接器生產(chǎn)流程。“儲能連接器生產(chǎn)流程都在這里了”由仁昊連接器為您整理,采購連接器,上仁昊。

2022-01-06 14:02:42 1221

1221

今天介紹一下,如何在Vivado中添加時序約束,Vivado添加約束的方法有3種:xdc文件、時序約束向?qū)В–onstraints Wizard)、時序約束編輯器(Edit Timing Constraints )

2023-06-26 15:21:11 1847

1847

很多小伙伴開始學習時序約束的時候第一個疑惑就是標題,有的人可能會疑惑很久。不明白時序約束是什么作用,更不明白怎么用。

2023-06-28 15:10:33 828

828

??本文主要介紹了時序設(shè)計和時序約束。

2023-07-04 14:43:52 692

692 本小節(jié)對時序約束做最終的總結(jié)

2023-07-11 17:18:57 351

351

本文繼續(xù)講解時序約束的第四大步驟——時序例外

2023-07-11 17:17:37 417

417

一、概述在上一篇雜談文章《[HPM雜談]你想要了解的先楫hpm_sdk開發(fā)都在這里系列(一)》,大概分析了先楫通用單片機開發(fā)與其他國產(chǎn)單片機的開發(fā)差異,以及開發(fā)優(yōu)劣勢。剛好在這個月底,先楫官方發(fā)布

2023-10-12 08:18:09 826

826

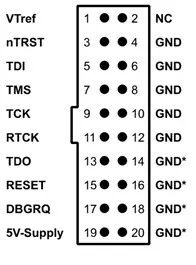

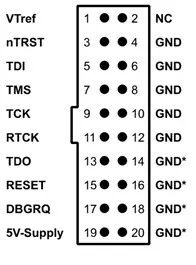

J-Link 中的JTAG 接口:正確使用需要了解的注意事項,在這里!

2023-12-01 16:01:57 560

560

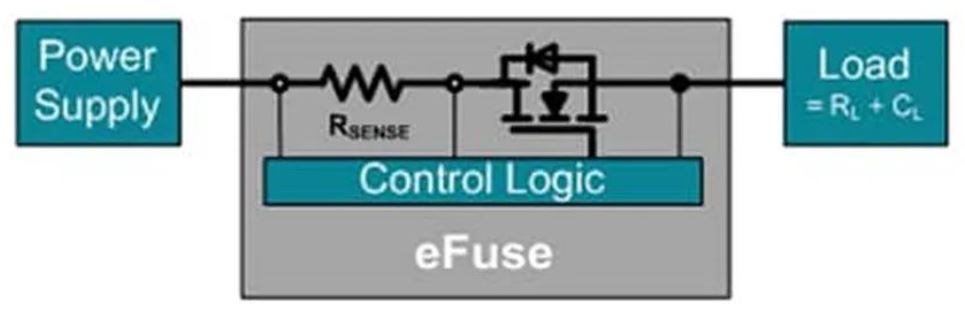

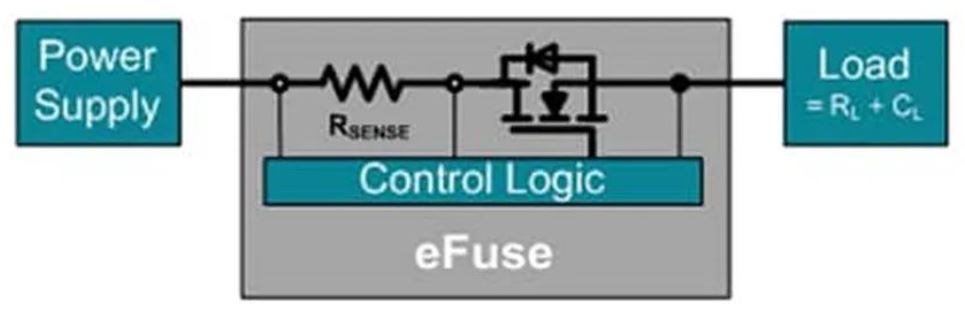

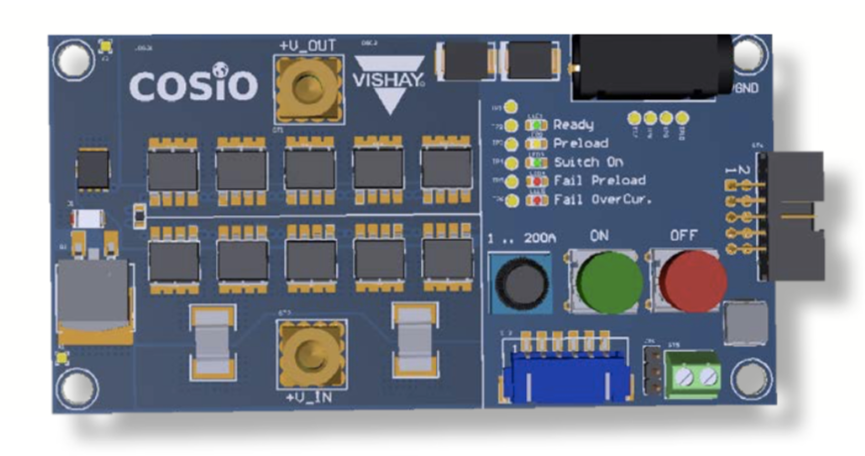

有關(guān)eFuse電子保險絲,你應該了解的技術(shù)干貨,都在這里!

2023-12-04 10:20:13 639

639

48V電源系統(tǒng)可恢復eFuse的設(shè)計秘訣,在這里!

2023-12-05 10:09:25 317

317

電子發(fā)燒友App

電子發(fā)燒友App

評論