本篇文章將介紹:①RISC-V 指令集的起源和發展歷史,②討論各種RISC-V CPU核、SoC設計平臺和芯片產品的技術特點及選型要點,③重點闡述RISC-V 給嵌入式系統帶來了益處,④RISC-V指令擴展的特點與安全應用。 本期第二篇推文還將介紹:⑤支持RISC-V開源和商業軟件開發工具和操作系統的現況,最后⑥展望RISC-V 在教育和產業應用的發展趨勢。

引言

過去二十年ARM在移動和嵌入式領域成果豐碩,IOT 領域正逐漸確定其市場地位,其他商用架構(如MIPS)逐漸消亡。ARM在進軍Intel所在的x86市場,已經對傳統PC和服務器領域造成一定壓力。RISC-V 開源指令集的出現,引起了產業界的廣泛關注,科技巨頭很看重指令集架構(CPU ISA)的開放性,各大公司正在積極尋找ARM之外的第二選擇,RISC-V成為必然選擇。RISC-V 被全球范圍內的大學陸續采納為教材替代以前的MIPS和X86架構,政府和企業采納RISC-V為標準指令集,開源的CPU核和SoC芯片不斷涌現,生態環境逐漸豐富,開發者社區愈來愈活躍。

什么是RISC-V ?

一個CPU支持的指令和指令的字節級編碼就是這個CPU的指令集(ISA),指令集在計算機軟件和硬件之間搭起了一個橋梁。不同的CPU家族:X86、PowerPC和ARM,都有不同的ISA,RISC-V 是其中唯一的開源ISA。

RISC-V 是一種開源的指令集架構,它不是一款CPU芯片,甚至不是一個完整的指令集,它是指令集規范和標準。RISC-V 起源于加州大學伯克利分校,在2010年夏季Krste Asanovic教授帶領他的兩個學生Andrew Waterman , Yunsup Lee啟動了3個月項目 ,針對X86和ARM 架構復雜和IP授權的原因,希望開發簡化和開放的指令集架構。

RISC-V基金會創建于2015年,是一家非盈利組織。基金會董事會由Bluespec、Google、Microsemi、NVIDIA、NXP、UC Berkeley、Western Digital 7家單位代表組成,主席目前是Krste Asanovi 教授,基金會為核心芯片架構制定標準和建立生態,標準是公開免費下載。基金會旗下有400余家以上的付費成員,包括高通、NXP、阿里巴巴和華為等,RISC-V 基金會成員可以使用RISC-V商標,RISC-V 采用開源BSD 授權 ,任何企業、高校和個人都可以遵循RISC-V架構指南設計自己的CPU。RISC-V基金會總部從美國遷往瑞士,并于2020年3月完成在瑞士的注冊,基金會更名為RISC-V國際基金會(RISC-V International Association)2。

十年來RISC-V 蓬勃發展,在CPU IP核,平臺、SoC芯片和應用上都有了相當數量的發展,比如,應用上有西部數據設計的SSD和HDD控制器,內核是SweRV Core,中科藍芯開發的藍牙耳機芯片,嘉楠科技的K210 AIOT 芯片 ,南京沁恒電子的藍牙MCU、32位通用MCU和高速接口的MCU,它們的內核都是RISC-V。

2021年9月1-3日,ELEXCON深圳國際電子展暨嵌入式系統展將專門打造『 RISC-V技術專區 』,匯聚行業內領先企業,全面展示RISC-V軟硬件開發、RISC-V開發工具、RISC-V處理器應用、開源技術等新技術、新產品和新方案,迎接芯片行業發展的歷史性機遇!

▼2021部分參展商

RISC-V指令集介紹

RISC-V的指令集使用模塊化的方式進行組織,每個模塊使用一個英文字母來表示。RISC-V最基本、也是唯一強制要求實現的指令集是由 I 字母表示的整數指令子集。使用該整數指令子集,便能夠實現完整的軟件編譯器。其他的指令子集部分均為可選的模塊,其代表性的模塊包括M/A/F/D/C,比如 某款RISC-V 處理器內核是RV32IMAC,即代表實現了I/M/A/C 指令集,。RISC-V 指令集發展變化中,32I和64I 已經凍結,MAFDQC指令擴展是凍結了,指令集如32E,128I,LBJTPV和ZAM原子訪問擴展還在開發中,指令集擴展是RISC-V的技術特色,廣泛征求會員單位和產業界的意見是RISC-V發展合理的路徑 3 。

表1 RISC-V 部分指令集描述

RISC-V 處理器核、SoC 平臺 和SoC芯片

3.1 RISC-V 處理器核

在詳細闡述RISC-V 處理器嵌入式開發之前,我們首先梳理一下幾個概念:RISC-V 處理器核心(Core ,簡稱核),SoC 平臺 和SoC芯片,以及開發者如何選擇它們。自RISC V 架構誕生以來出,市場上已有數十個版本的 RISC -V 核和SoC芯片,它們中一部分是開源免費,某些是商業公司開發用于內部項目的 ,還有商業公司開發的 處理器核和平臺。西部數據的SweRV架構(RV32IMC)是一個32bit順序執行指令架構,具有雙向超標量設計和9級流水線,采用28nm工藝技術實現,運行頻率高達1.8GHz,可提供4.9 CoreMark/MHz的性能,略高于Arm的Cortex A15,已經用在西部數據的SSD和HDD 控制器上使用,SweRV項目是開源的項目。

典型的開源的RISC-V 核有Rocket Core,它是美國加州大學伯克利分校開發一個經典的RV64 設計,伯克利分校還開發一個BOOM Core,它與Rocket Core不同的是面向更高的性能。蘇黎世理工大學(ETH Zurich)開發的Zero-riscy,它是經典的RV32 設計,蘇黎世理工大學另外一款R15CY Core,可配置成RV32E,面向的是超低功耗、超小芯片面積的應該場景。由Clifford Wolf開發RISC-V Core PicoRV32,重點在于追求面積和CPU頻率的優化。

開源的核用于研究和教學很合適,但是用于商業芯片設計還有許多工作要做。SiFive(賽昉科技)由Yunsup Lee創立,他也是RISC-V的創始人之一。2017年公司發布首個RISC-V核和SoC平臺家族,以及相關支持軟件和開發板,這些芯片包括采用28納米制造技術的64位多核CPU U500,支持Linux操作系統,以及采用180納米制造技術的多外設低成本IoT處理器核 E300。開發RISC-V處理器核的廠商還包括Codasip、Syntacore、T-Head(平頭哥) Andes (晶芯科技),以及創業公司芯來科技和優矽科技。

3.2 RISC-V SoC平臺

知名的RISC-V 處理器SoC 平臺有瑞士理工大學的PULPino ,開源項目LowRISC

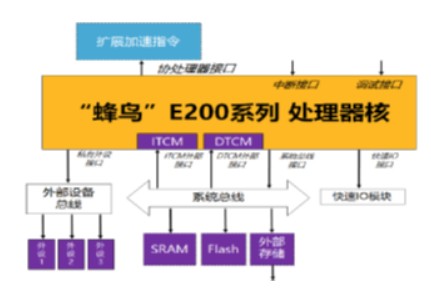

以及Rocket Chip - 伯克利分校基于Chisel開發的開源SoC生成器。芯來科技胡振波發起的蜂鳥E200開源項目4,配合他的圖書,是在國內知名度非常高的開源軟核SoC平臺之一。在64位SoC 平臺方面,平頭哥半導體發展很快,先后推出了玄鐵C906單核和玄鐵C910多核高性能64位 RISC-V 處理器。

圖1 蜂鳥E200 RISC-V 處理器

3.3 RISC-V SoC 芯片

RISC-V 處理器SoC芯片近年發展迅速,知名度較大的通用性SoC芯片有兆易創新開發的GD32VF103 MCU 芯片, 該芯片基于芯來Bumblebee 內核(RV32IMAC)。GD32VF103系列提供了108MHz的運算主頻,16KB到128KB的片上閃存和6KB到32KB的SRAM,有4個16位通用定時器,2個16位基本定時器和2個多通道DMA控制器。GD32VF103 MCU全新設計的中斷控制器(ECLIC)提供了多達68個外部中斷并可嵌套16個可編程優先級,以增強高性能控制的實時性。

GD32VF103 MCU開發板有GD32VF103V-EVAL全功能評估板以及GD32VF103-START入門級學習板。還有芯來科技開發RV-START ,以及Sipeed Longan Nano 開發板 5 和IAR 最新的 IAR RISC-V GD32 EVAL 評估套件6,見下圖。

圖2 IAR RISC-V GD32V 評估套件

嘉楠科技K210 是一個AIOT SoC 芯片,K210 包含 RISC-V 64 位雙核 CPU,采用雙RV64 GC Core,MAFD ISA 指令標準擴展。K210 包含KPU 通用神經網絡處理器,內置卷積可以對人臉或物體進行實時檢測,K210 的FFT 加速器是用硬件的方式來實現7 。

NXP RV32M1 集成了4個核: RISC-V RI5CY 核, RISC-V ZERO-RISCY 核, ARM CortexM4 核和 ARM Cortex-M0+ 核。從專業人士視角看,RV32M1 更像是工程實驗樣品,用來給開發者評估使用,為此NXP 為開發者創建https://open-isa.org/ 社區,維護工具鏈和軟件生態,通過贈送開發板和舉辦大賽為開發者學習RISC-V 嵌入式開發提供了便利,在早期市場培育期發揮重要的作用 8,見下圖。

圖3 NXP RISC-V 織女星開發板

Microchip PolarFire SoC芯片是一款低成本, 多核RISC-V SoC FPGA,包含了4個 64-bit RV64GC RISC-V 應用核,可運行Linux, 一個單核 RV64IMAC 做實時和監控任

3.4 RISC-V核、平臺和芯片究竟該如何選擇呢?

近期關注RISC-V處理器研究、開發和教學的人士開始增多,建議:

(1)。芯片設計者可選擇RISC-V 核 和SoC 平臺 構建自己的芯片。比如,使用 PULPino 平臺開發 SoC 芯片,內核使用 RI5CY和Zero-risky,國內企業和高校研究項目都有在使用。

(2)建議嵌入式和物聯網系統開發者使用 RISC-V SoC 芯片。比如,選擇GD32VF103 系列 MCU芯片做嵌入式項目開發,GD32VF103有多款開發板和開發工具鏈支持。AIOT 應用可以選擇 K210 ,K210開發軟件SDK 非常成熟,支持freertos 和裸機,最近Linux 5.8 正式將K210 RISC-V 納入主線, K210 已經成功應用在人臉識別和智能抄表等機器視覺和機器聽覺領域。

(3)高校和研究機構可以選擇開源RISC-V 核 在FPGA 平臺上進行計算機體系架構、操作系統 ,編譯技術以及嵌入式系統教學和研究工作。比如,Arty FPGA 開發板上實現一個 SiFive 開源Freeedom E310 微控制器的技術已經非常成熟,相應軟件工具鏈支持的很好 9, 見下圖。

圖4可以配置RISC-V 軟核的Arty FPGA 開發板

RISC-V 給嵌入式系統帶來的優勢

我們上一節討論了RISC-V 處理器核、平臺和芯片 。很明顯,嵌入式與物聯網以及AIOT 是RISC-V 最活躍的應用市場,RISC-V給嵌入式系統帶來許多優勢,我僅就以下三點做個闡述:

(1)開源和免費。開源是新的經濟方式,是成功的商業之道, 也學生和工程師學習最佳途徑。ISA開源意味著開發者可以針對特定應用場景,創造自己的芯片架構,免費則可以降低芯片設計門檻,讓草根開發者進入芯片設計領域。

(2)簡單和靈活。RISC-V基礎的指令集有50條,模塊化的4個基本指令集能讓設計者。開發出很簡化的RISC-V CPU,代碼密度低功耗很小的芯片,覆蓋從8051-ARM A系列 各種嵌入式處理器。

(3)高效和安全。RISC-V 通過預留編碼空間和用戶指令支持擴展的指令集,通過指令集擴展實現運算加速和物聯網安全。物聯網保護的一種通用的途徑是分層,分為信任執行環境(TEE)和非信任環境。RISC-V ISA的設計將TEE硬件要求定義為標準規范的一部分,可以在任何RISC-V 芯片上實現,包括配置物理內存保護(PMP), PMP類似 ARM處理器內存保護單元(MPU)。

HEX-FIVE 公司在RV32 Core 做了IoT 分區保護的應用案例 10,見下圖4,軟件可參考開源代碼https://github.com/hex-five/multizone-secure-iot-stack 。從圖中我們可以看到,SOC 芯片是X300 Bitstream ,采用是開源Rocket RV32IMAC 內核。Digilent ARTY A7 FPAG開發板 ,配有以太網。軟件上 MultiZone 安全可信執行環境 配置成4區:

(1) Zone 1 區,運行FreeRTOS 有三個任務,分別是CLI任務, PWM LED任務,機器人手臂控制任務。

(2) Zone 2區,移植以太網,運行 PicoTCP 軟件協議,TCP信道進行了TLS 加密。

(3) Zone 3區: 運行WolfSSL TLS 1.3 ,存儲信任根,加密密鑰,密碼以及受保護的文件等放在這個區域。

(4) Zone 4區,UART 本地終端應用。

圖5 MultiZone Security IoT Stack RISC-V 平臺應用案例

更多技術干貨

更多內容關于:⑤支持RISC-V開源和商業軟件開發工具和操作系統的現況,最后⑥展望RISC-V 在教育和產業應用的發展趨勢。請見姊妹篇推文!

? ? ? ?責任編輯:tzh

?

電子發燒友App

電子發燒友App

評論