。 Pynq降低了開發人員的門檻,但知其然也知其所以然,開發效率將會更高。因此,在進入PYNQ的python開發之前,我們先來學習ZYNQ的PL與PS開發,為接下來的學習提供良好的基礎。 本部分的學習

2020-12-25 14:11:50 6843

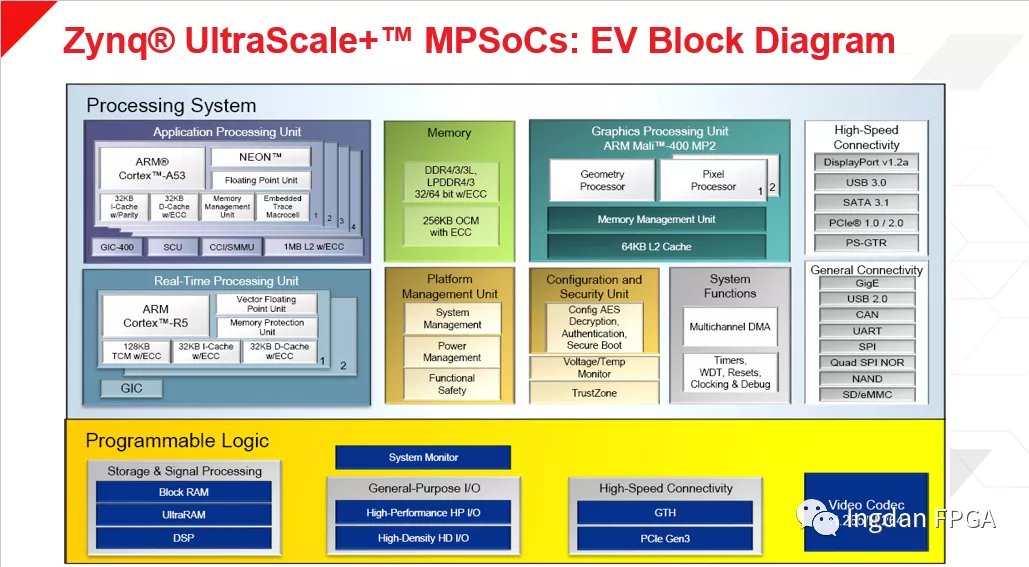

6843 本篇主要介紹ZU+系列MPSoC的外圍接口,針對每個接口進行概述性介紹,后續會針對個別接口進行詳細介紹原理圖設計和PCB設計。 ZU+系列MPSoC的外圍接口主要包括兩部分:PL部分和PS部分。PL

2020-12-26 10:04:38 4310

4310

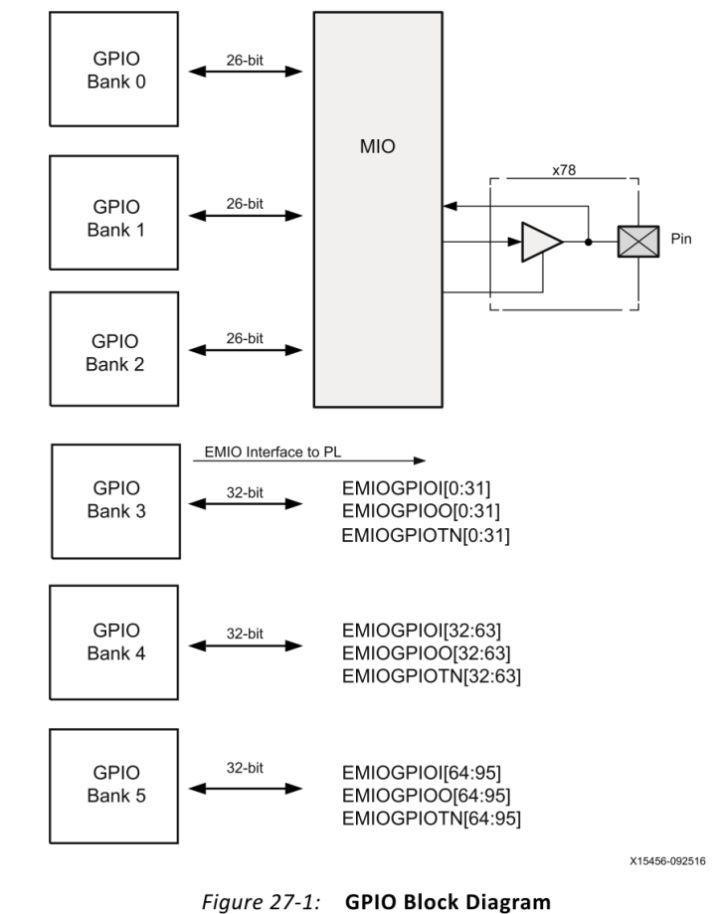

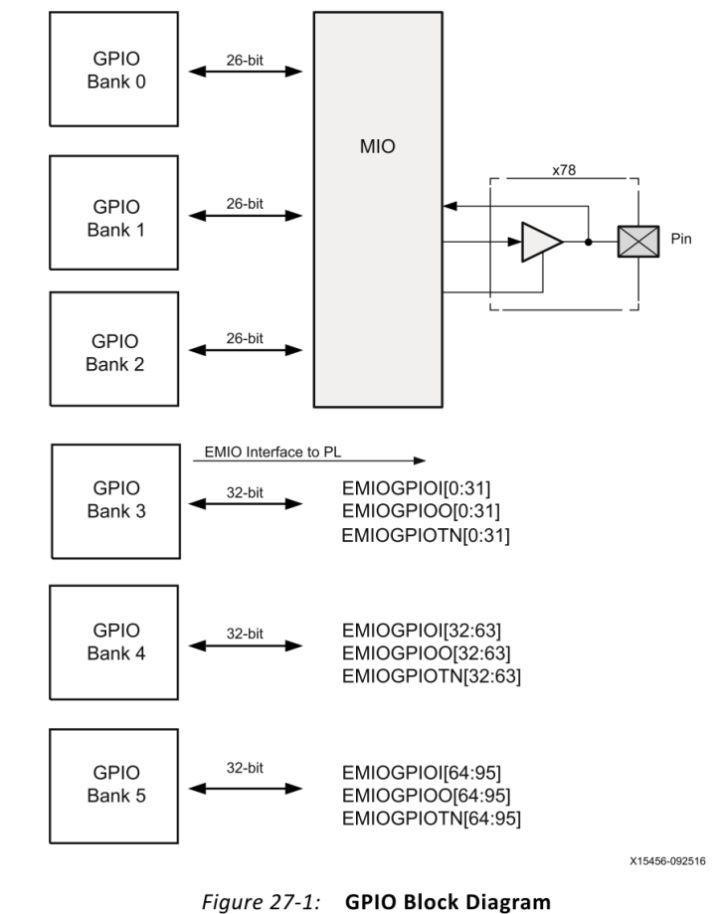

;AXI_GPIO是封裝好的IP核,PS通過M_AXI_GPIO接口控制PL部分實現IO,使用時消耗管腳資源和邏輯資源。 使用的板子是zc702。 1.MIO方式 Zynq7000 系列芯片有 54

2020-12-26 10:12:57 3306

3306

如果想用PS點亮PL的LED燈,該如何做呢?一是可以通過EMIO控制PL端LED燈,二是通過AXI GPIO的IP實現控制。本章介紹如何使用EMIO控制PL端LED燈的亮滅。同時也介紹了,利用EMIO連接PL端按鍵控制PL端LED燈。

2021-01-30 10:05:00 6730

6730

PL和PS的高效交互是zynq soc開發的重中之重,我們常常需要將PL端的大量數據實時送到PS端處理,或者將PS端處理結果實時送到PL端處理,常規我們會想到使用DMA的方式來進行,但是各種協議非常

2021-01-30 09:54:00 12917

12917

有時CPU需要與PL進行小批量的數據交換,可以通過BRAM模塊,也就是Block RAM實現此要求。本章通過Zynq的GP Master接口讀寫PL端的BRAM,實現與PL的交互。在本實驗中加入了自定義的FPGA程序,并利用AXI4總線進行配置,通知其何時讀寫BRAM。

2021-02-22 13:51:00 7359

7359

/p/005899fe6815 二、ZYNQ7020 分為PS端、PL端 PS: 處理系統 (Processing System) , 就是與 FPGA 無關的 ARM 的 SOC 的部分。 PL: 可編程邏輯

2021-05-12 10:25:31 13958

13958

本文主要介紹ZYNQ PS + PL異構多核案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx SDK 2017.4

2021-09-07 17:03:30 2880

2880

xilinx mpsoc 平臺中,PS 和 PL 進行交互時,PS 需要獲取 PL 發出的中斷信號。從 mpsoc 技術參考手冊 ug1085 TRM 中可知,PL 給到 PS 的中斷有兩組

2023-08-24 16:06:22 560

560

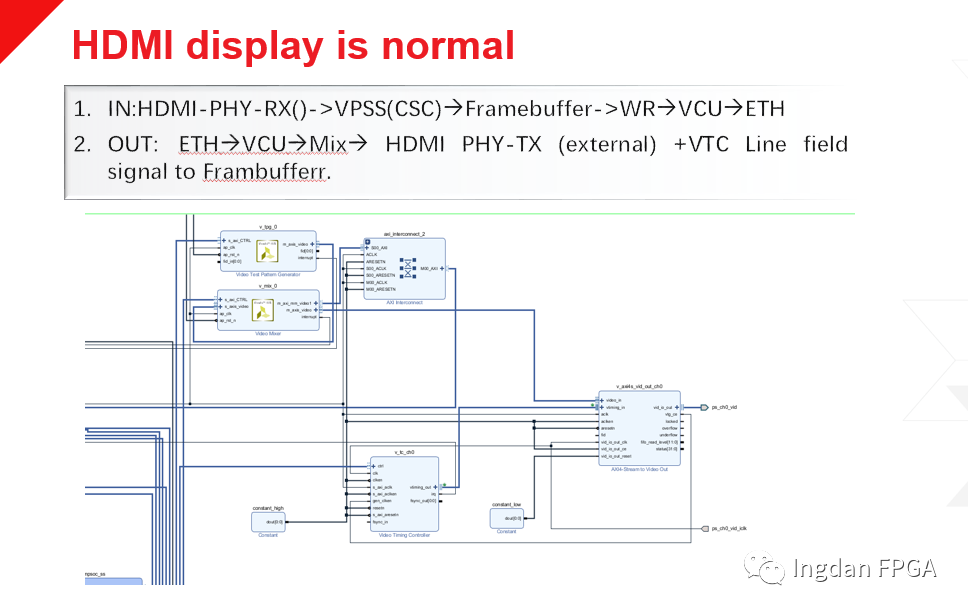

10-100-1000 Mbps Ethernet (RGMII?) 網絡接口PS端QSPI flash 存儲PS端 SD卡,Emmc存儲PL端64bit 2GB 容量DDR3 存儲PL端擴展HDMI 輸出實現視頻顯示

2021-07-09 17:14:21

PS176是一個顯示端口 (DP)至HDMI 2.0視頻接口轉換器適用于需要視頻協議轉換的電纜適配器、電視接收器、監視器和其他應用。它將接受任何顯示端口輸入格式,包括DP 1.1a、dp

2022-05-18 10:31:07

ZYNQ進階之路9--PS端實現FreeRTOS嵌入式系統導論FreeRTOS簡介實現步驟導論在之前的章節中我們我們完成了PS端、PL端和PS+PL的一些工程,本章節我們插入一個小插曲,講解

2021-12-22 08:29:20

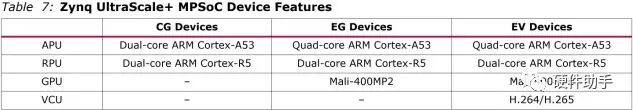

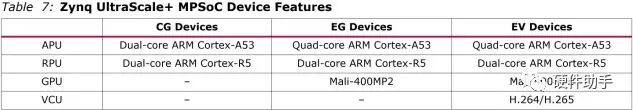

Cortex-A53 + 雙核ARM Cortex-R5) + PL端UltraScale+架構可編程邏輯資源,支持4K@60fps H.264/H.265視頻硬件編解碼,并支持SATA大容量存儲接口,評估板由

2023-06-21 15:38:10

,Video Format配置為Mono/Sensor,Pixels Per Clock配置為1,色彩數據位寬為8bit。4.2 AXI VDMA IP核本案例使用AXI VDMA IP核進行視頻數據緩存

2021-05-24 11:12:40

到寫數據通道中。當主機發送最后一個數據時,WLAST信號就變為高。當設備接收完所有數據之后他將一個寫響應發送回主機來表明寫事務完成。 PS與PL內部通信(用戶自定義IP)先要自定義一個AXI-Lite

2018-01-08 15:44:39

、Xilinx Vivado 2017.4、Xilinx SDK 2017.4。案例包含PL端Vivado工程,主要使用Xilinx提供的標準IP核配置PL端資源實現接口擴展,同時包含PS端裸機

2021-05-28 14:28:28

ZYNQ7000系列FPGA的PS自帶兩個IIC接口,接口PIN IO可擴展為EMIO形式即將IO約束到PL端符合電平標準的IO(BANK12、BANK13、BANK34、BANK35);SDK中

2020-12-23 17:06:35

ZYNQ7000系列FPGA的PS自帶兩個IIC接口,接口PIN IO可擴展為EMIO形式即將IO約束到PL端符合電平標準的IO(BANK12、BANK13、BANK34、BANK35

2021-01-08 16:44:20

;AXI-Stream 的轉換,只不過是專門針對視頻、圖像等二維數據的。AXI-CDMA:這個是由 PL 完成的將數據從內存的一個位置搬移到另一個位置,無需 CPU 來插手。涉及到DMA主要包括AXI

2022-03-31 11:39:10

的存儲器。

⑥ACP : PL端可以直接從PS的Cache中拿到CPU計算的結果,延時低

⑦DMA :DMA控制接口,用于控制高速數據傳輸的通道。

(3)AXI協議

AXI所采用的是一種READY

2023-11-03 10:51:39

使用XPS時,然后將.xmp導入planahead,生成一個比特流文件。我可以使用chipcope / impact進行配置,從PS-> PL運行獲取FCLK還是我必須導出到sdk?我正在

2019-09-05 06:03:46

嗨,我必須找出zynq 7020 PS和zynq PL如何通話,特別是我必須找到將在ARM中處理的SDK C代碼。你能用一個明確的C代碼告訴我,它解釋了數據如何從PS轉移到PL,這是ARM用來做這個的基本程序嗎?謝謝

2020-05-08 09:37:11

PS端QSPI flash 存儲PS端 SD卡,Emmc存儲PL端32bit 1GB 容量DDR3 存儲PL端擴展HDMI 輸出實現視頻顯示應用PL端擴展16路 I/O, 4個LED指示燈PL端擴展標準

2020-03-24 09:39:49

,硬件資源豐富。可通過PL端進行高速圖像數據采集,并通過PS端進行業務邏輯控制,運用十分便捷。(2)視頻接口豐富可拓展眾多目標追蹤場合常用的視頻接口,如CameraLink、SDI、HDMI、PAL等

2021-05-19 17:10:50

FFT的核心算法,以及與PS部分的數據交換。

PS部分包含了以下的組件:

ARM Core:這是一個基于ARM架構的處理器核心,它運行著我在上一章節介紹的PYNQ系統。它可以通過AXI Lite接口

2023-10-02 22:03:13

由可編程邏輯中的HDMI IP控制。在官方的PYNQ框架中,HDMI IP連接到PS DRAM,視頻數據流可以從HDMI傳輸到內存,也可以從內存流式傳輸到HDMI輸出。可以使用Python對視頻數據進行采集

2019-01-28 22:50:13

一直糾結于怎樣給PL提供時鐘,zynq開發不同于一般的FPGA開發。其中時鐘和復位問題就是相當重要的問題,有兩種方式可以為PL部分提供時鐘和復位:1、PS部分可以產生四個毫無關系的輸出時鐘和復位信號

2015-06-08 17:29:32

本帖最后由 blackroot 于 2015-6-10 17:06 編輯

一直沒搞懂PS怎樣給PL提供復位和時鐘,今天這個問題終于解決了~~~~~用一個簡單的例子來說明一下,怎樣使用PS輸出

2015-06-10 16:59:53

個邏輯膠合者被PS指揮;當然上電和初始化順序還是一樣的,必須先啟動配置完PS,才能初始化PL。首先我們在Vivado開發環境中建立RTL工程,并編寫我們需要在PL中實現的功能代碼HDL文件,把它做為

2015-06-01 11:54:12

總線的從接口,和AXI主接口實現互聯,來對BRAM進行讀寫操作。針對不同的應用場合,該IP核支持單次傳輸和突發傳輸兩種方式。14.2實驗任務本章的實驗任務是PS將串口接收到的數據寫入BRAM,然后從

2020-09-04 11:08:46

CameraLink1接口輸入的差分視頻數據轉化成并行視頻數據。lvds_n_x_1to7_sdr_rx模塊開發文檔為產品資料“6-開發參考資料\Xilinx官方參考文檔\”目錄

2021-04-19 15:26:53

道數據差分對為4組,需2個連接器。圖 114.2lvds_n_x_1to7_sdr_rx模塊本案例使用lvds_n_x_1to7_sdr_rx模塊將CameraLink1接口輸入的差分視頻數據轉化成

2021-04-22 09:14:50

道數據差分對為4組,需2個連接器。圖 114.2lvds_n_x_1to7_sdr_rx模塊本案例使用lvds_n_x_1to7_sdr_rx模塊將CameraLink1接口輸入的差分視頻數據轉化成并行

2021-04-27 09:40:41

XCZU7EV高性能處理器設計的高端異構多核SoC工業核心板,處理器集成PS端(四核ARM Cortex-A53 + 雙核ARM Cortex-R5) + PL端UltraScale+架構可編程邏輯資源,支持

2023-06-21 15:27:45

1. 硬件介紹 由于開發板上只有DP可以顯示,但卻是PS端的,PL端沒有HDMI的接口,因此我們采用AN9134的HDMI擴展模塊實現HDMI顯示。將24位RGB編碼輸出TMDS差分信

2021-01-15 16:49:10

和M_AXI_HPM0_LPD。 位于PS端的ARM直接有硬件支持AXI接口,而PL則需要使用邏輯實現相應的AXI協議。Xilinx在Vivado開發環境里提供現成IP如AXI-DMA,AXI-GPIO

2021-01-07 17:11:26

LT8911 LT7211、普瑞PS8625、昆泰CH7511等方案,DP換LVDS轉換主要是用在一些LVDS接口的液晶,將DP信號轉出至LVDS屏輸出,此時需要用DP TO LVDS這樣一個轉接板來實現屏顯示

2021-08-02 20:00:42

錯誤。然后,我在SDK中編程PS端,led閃爍正確的頻率!我的問題,當鎖定Zynq PL時鐘? PS程序之后?需要多長時間?是不是意味著,PL配置期間LED閃爍錯誤,在非易失性Flas Boot中編程PS期間(或之后)閃爍?謝謝的Berker

2020-08-27 15:09:19

我想給板子接上一個u***接口的鍵盤,不跑操作系統,只用ps部分接收鍵盤的數據然后傳遞給PL,不知道如何編寫sdk的代碼來跟u***的phy通信呢?有沒可以參考的例程或者文檔?

2015-12-16 17:12:38

(Processing System,PS)和可編程邏輯資源(Programmable Logic,PL)),提供了基于Zynq-7010/7020的多路千兆網口實現方案。1 硬件平臺TLZ7x-EasyEVM-S

2021-10-22 09:43:10

FPGA?外圍的數據傳輸帶寬以及存儲器帶寬。但是在 FPGA 內部,可編程邏輯部分隨著工藝提升而不斷進步的同時,內外部數據交換性能的提升并沒有那么明顯,所以 FPGA 內部數據的交換越來越成為數據傳輸的瓶頸

2020-09-07 15:25:33

隨著USB C接口的普及,越來越多的筆記本只保留了USB C接口來傳輸視頻信號,而顯示端依舊是HDMI的天下。因此,許多需要擴展顯示的場景必須配備一個USB C to HDMI的適配器來實現。如會議

2019-09-23 09:05:04

實例的內容及目標1.實例的主要內容本實例通過Verilog編程實現在紅色颶風II代Xilinx開發板上面實現對鍵盤、LCD、RS-232等接口或者器件進行控制,將有鍵盤輸入的數據在LCD上面

2019-06-03 05:00:03

如何實現labview跟電腦的數據交換,不用硬件

2015-11-18 13:35:46

文件的PL,然后給每個人提供刺激來測試設計,PS將從PL回讀一些輸出,在結束我將結果數據發送回用戶。換句話說,它是一種“設計測試”服務。(1)我有什么方法可以達到這個目標嗎?似乎唯一的“cat

2020-05-21 07:07:50

我的設備是zedboard702,我知道如何在使用PS和PL時使用SDK生成啟動映像和程序閃存。問題是我只是使用PL,現在如何編程flash?

2019-09-30 09:43:18

親愛的大家,我只是想知道如何找到Ultrascale +的PL和PS的地址轉換(映射方案到DRAM-我的意思是哪個等級,庫等)?

2019-10-16 08:35:37

百萬組隨機數據matlab和Verilog代碼仿真比對;FFT模塊詳解縮放因子;提供各類定點模型及源代碼;提供AD936X配置源碼。配套近2000分鐘視頻教程詳述稀疏校驗矩陣存儲及LDPC編碼實現方式

2019-07-23 10:56:41

。ACP為64位AXI從接口,它提供了一個異步緩存相關接入點,實現了PS和PL端加速器之間的低延遲路徑。AXI Timer IP核用于計數,可通過其寄存器來計算浮點矩陣乘法運算加速器IP核的運算時間。圖

2021-11-11 16:02:09

為配置PL邏輯的控制器),也可以同時配置PS和PL邏輯,可見Zynq芯片可以靈活的搭建嵌入式平臺實現不同的功能。這個通過模塊圖就可以看得更清楚了。http://www.xilinx

2016-10-05 14:05:31

大家好,我已經在PS中產生了一個100Mhz的時鐘信號,并使其在外部被PL接收。我使用了原始的ODDR但沒有成功我可以從引腳輸出100 Mhz時鐘。有什么建議么??以上來自于谷歌翻譯以下為原文

2019-02-22 09:09:05

為什么一個簡單的程序運行不了,請求幫忙看一下。做個LED流水燈,是想用PS部分生成100MHz的頻率,然后用這個頻率來實現PL部分三色led移位,但是好像PS部分有問題,不知道怎么配置了。這是PS

2016-01-02 21:35:38

對應的信號功能后,在PL的代碼里面就不需要寫任何的邏輯,甚至引腳分配都不需要(生成的PS系統會自動分配)。但是EMIO就要在PS的系統中引出,然后在PL頂層源碼中申明端口類型,做引腳分配(因為EMIO用

2019-10-12 17:35:16

變量表來表達。MCU與Gateway之間的所有交換信息都在這個變量表的表達范圍之內。超出變量表的信息,Gateway將水予受理。2.3 PS2000與MCU接口MCU應用系統一般都是以單片機為核心的一個

2018-12-05 10:39:22

請問zynq 怎么實現PS與PL數據交互,然后通過UART串口打印出來?前輩們做過的指導我一下。

2020-08-03 15:53:30

的Linux的xdevcfg設備來編程PL部件。有趣的解決方案是通過在同一芯片的PS部分運行的XVC遠程調試基于Zynq的設計。假設我將XAPP1251中描述的AXI-JTAG控制器添加到我的設計中,是否

2020-07-30 13:51:19

基于PS/2鼠標接口單片機輸入設備的實現:詳細介紹了PS/2鼠標/鍵盤接口的工作原理.提出了基于PS/2接口的三鍵鼠標作為單片機輸入設備的方法.該方案占用系統資源少,軟硬件

2009-10-27 18:30:48 81

81 什么是ps2接口 ps2接口是什么意思?

PS/2接口是目前最常見的鼠標接口,最初是IBM公司的專利,俗稱“小口”。這是一種鼠標和鍵

2009-05-03 22:07:26 24776

24776

什么是PS/2接口

很多老式的品牌機上采用PS/2口來

2010-01-22 12:21:57 2085

2085 一步一步學ZedBoard:使用PL做流水燈:目的是為了學習不使用ARM PS情況下,只對Zynq PL的編程方法,同時學習Xilinx PlanAhead工具的使用方法。(本資料是其相應的完整工程文件下載)

2012-12-05 13:52:39 185

185 本文通過實例詳細解析如何利用Zynq-7000的PL和PS進行交互。實際上,Zynq就是兩大功能塊:雙核Arm的SoC和FPGA。根據Xilinx提供的手冊,PS: 處理系統 (Processing System) , 就是與FPGA無關的A

2012-12-12 13:40:22 53204

53204

文中詳細介紹了PS/2接口協議的內容、電氣特性和標準鍵盤的第二套鍵 盤掃描碼集。給出了基于嵌入式系統的PS/2接口的軟、硬件實現方法,并介紹了工控PC外接雙鍵盤的解決方案。

2016-03-25 15:25:53 17

17 分享下PS與PL之間數據傳輸比較另類的實現方式,實現目標是: 1、傳輸時數據不能滯留在一端,無論是1個字節還是1K字節都能立即發送; 2、PL端接口為FIFO接口; PS到PL的數據傳輸流程: PS

2017-02-08 01:00:11 1431

1431

因為MicroZed是個低成本的開發套件,所以在板子上除了給PS(33.3333 MHz)、DDR、SPI FLASH、microSD卡接口和USB提供時鐘信號外,并沒有為PL部分提供單獨的晶振。

2017-02-09 14:16:11 4135

4135

了解Zynq PS / PL接口之后;到目前為止,我們已經分析了Zynq All Programmable SoC芯片中的PS (處理器系統)與PL(可編程邏輯)之間的接口。

2017-02-10 12:00:11 956

956

我們先來了解一下上節中介紹的Zynq SoC PS/PL接口,我創建一個很簡單的外設,使用的是DSP48E1的DSP邏輯片,依靠這個外設第一個寄存器內的控制字執行乘法,加法或減法。

2017-02-10 12:04:41 469

469

《一步一步學ZedBoard & Zynq》系列第二篇,目的是為了學習不使用ARM PS情況下,只對Zynq PL的編程方法,同時學習Xilinx?PlanAhead工具的使用方法?

2017-02-10 20:24:11 3749

3749 構建SoC系統,畢竟是需要實現PS和PL間的數據交互,如果PS與PL端進行數據交互,可以直接設計PL端為從機,PS端向PL端的reg寫入數據即可,本節研究如何再實現PL端對DDR3的讀寫操作。

2017-09-18 11:08:55 23

23 視頻通過HDMI接口進來,然后經Video Input模塊做格式變換,送入VDMA,該VDMA的作用是把數據送入在DDR3中所開辟的幀存中去。另一種是通過攝像頭等設備獲取視頻源,經PS/PL將數據

2017-11-17 10:05:44 7058

7058 zedboard可以將邏輯資源和軟件分別映射到PS和PL中,這樣可以實現獨一無二和差異換的系統功能,主要分為兩大部分,處理系統和可編程邏輯。以及二者之間的互聯特性。這篇筆記主要記錄zedboard的大體架構。

2018-06-26 06:24:00 6394

6394 Zynq在PS和PL之間有9個AXI接口。

2018-12-30 09:45:00 6907

6907 Zynq-7000系列基于Xilinx SoC架構。這些產品在單個設備中集成了功能豐富的雙核或單核ARM Cortex?-A9處理系統(PS)和28 nm Xilinx可編程邏輯(PL)。ARM Cortex-A9 CPU是PS的核心,還包括片上存儲器、外部存儲器接口和一組豐富的外圍連接接口。

2019-02-23 11:52:33 62

62 MPSoC是Xilinx基于16nm工藝推出的異構計算平臺,由于靈活、穩定,在業界得到了廣泛的使用。異構計算是一個比較新的領域,需要協調硬件設計、邏輯設計、軟件設計,對工程師的要求很高。實際設計過程中,很多工程師對實現PS/PL之間的數據交互感到頭疼。

2020-09-15 09:27:00 11208

11208

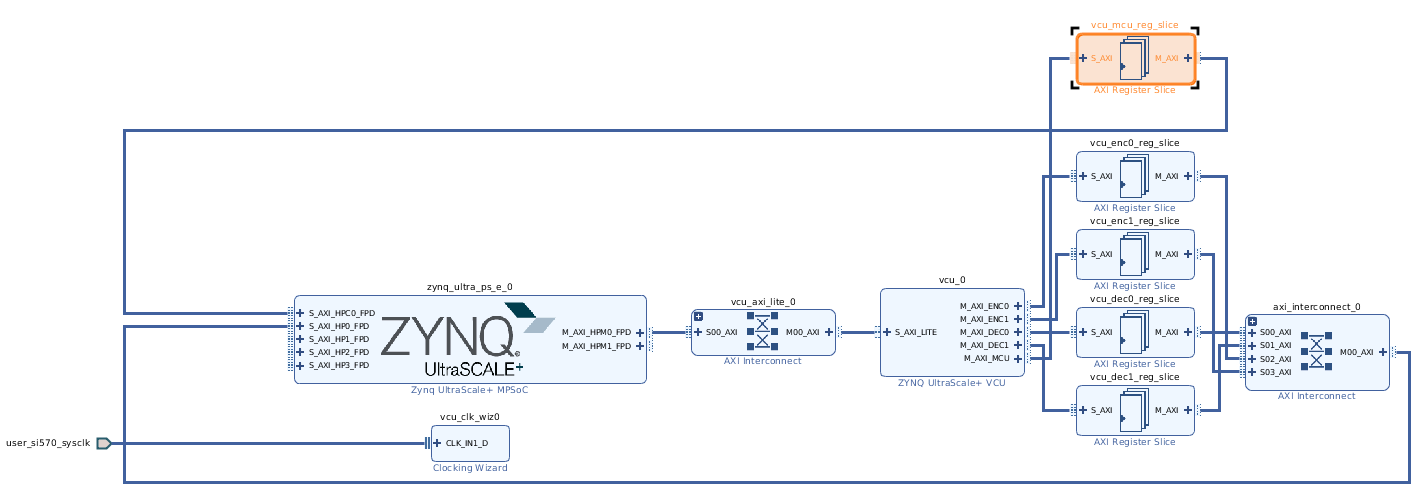

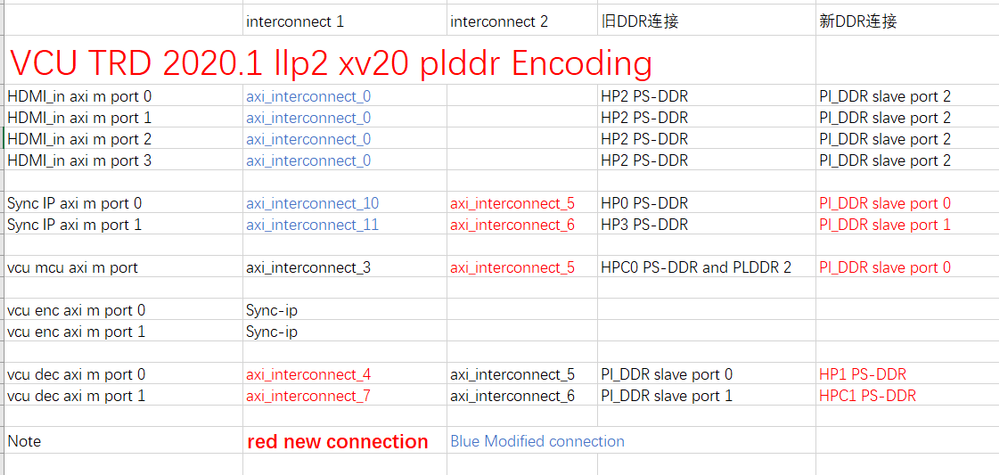

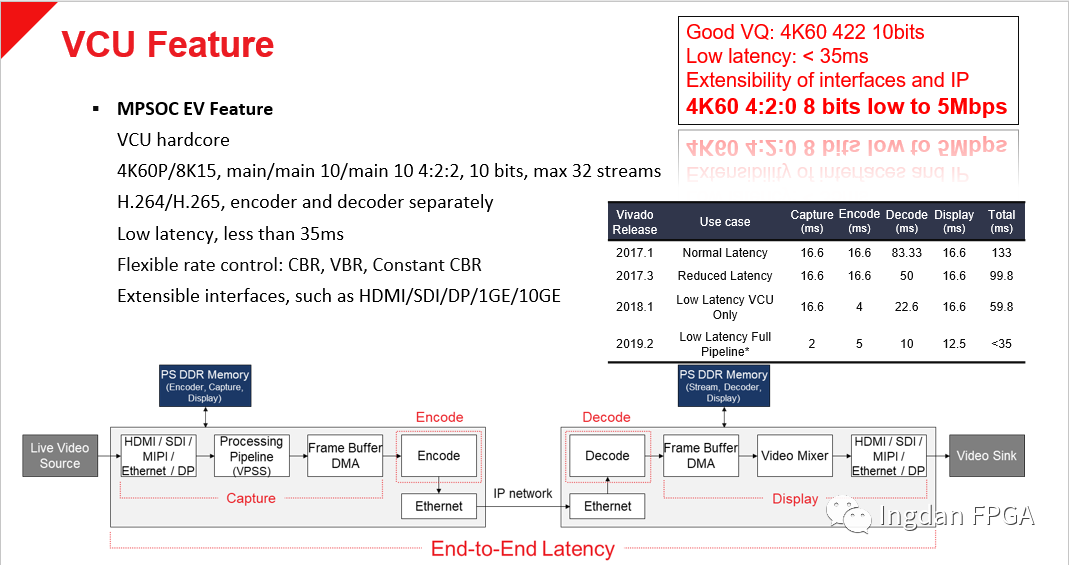

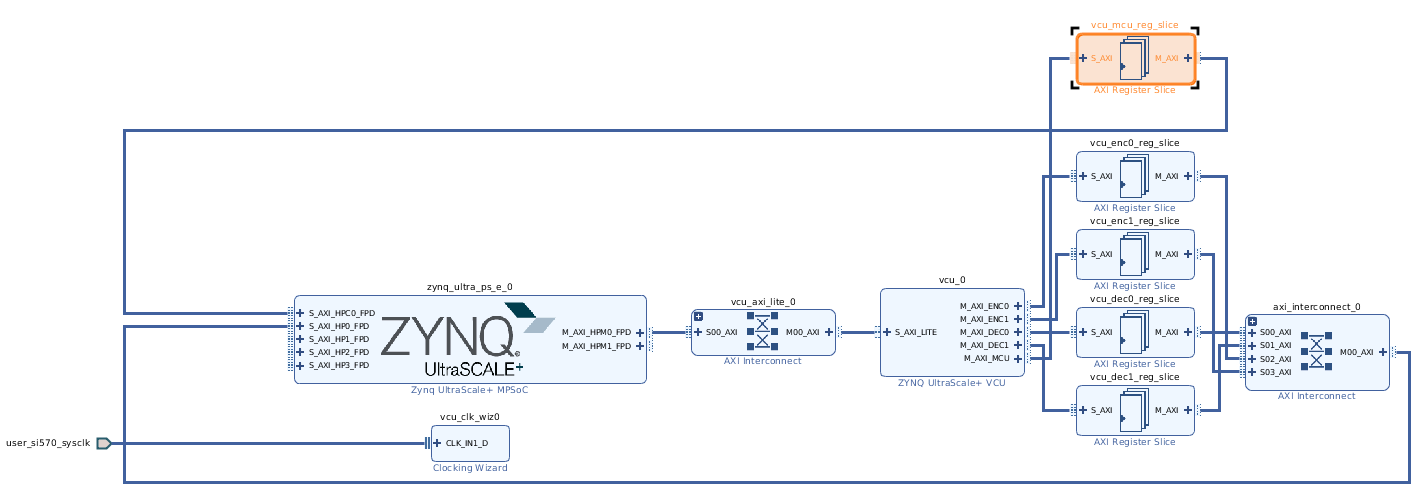

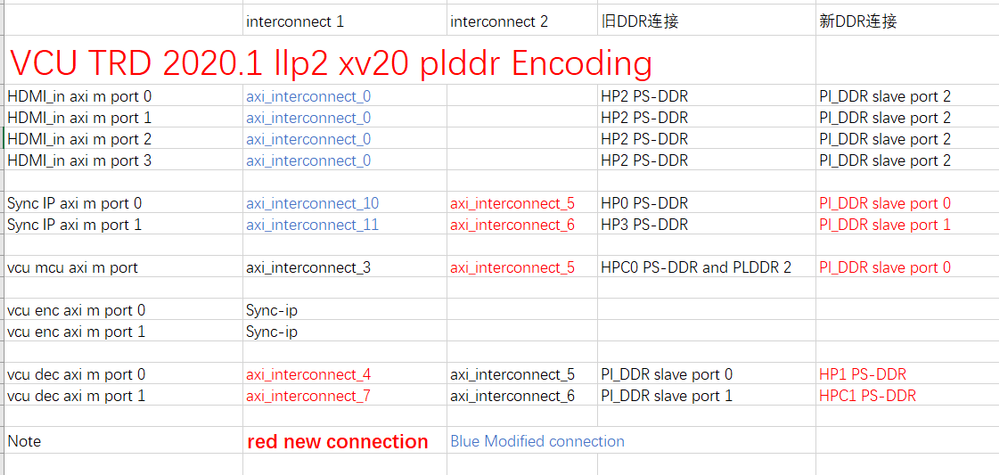

VCU 模塊在PL側,一共有五個AXI接口,它們分別是兩個 Encoder AXI,兩個 Decoder AXI, 和一個 MCU AXI。

2020-11-30 14:18:23 3835

3835

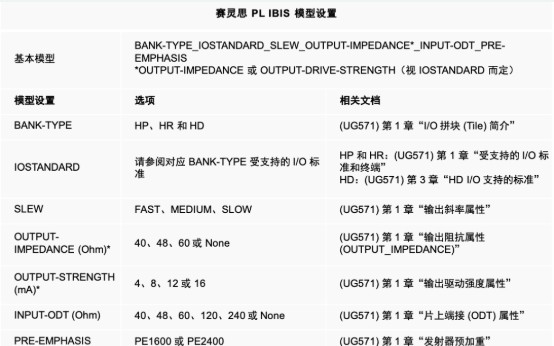

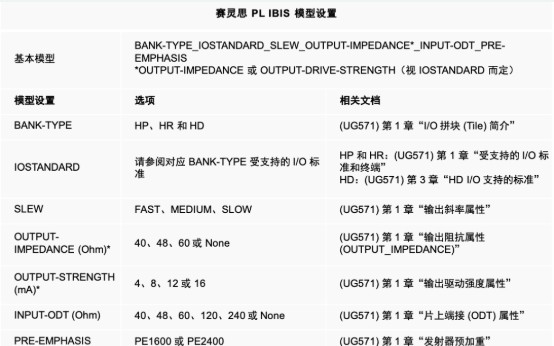

。 本篇博文旨在提供有關如何為可編程邏輯 (PL) 和處理器系統 (PS) 多用途 I/O (MIO) 進行 IBIS 模型名稱解碼的指導信息。 本文主要分 3 個部分: PL I/O 標準 PS MIO

2020-10-15 18:29:15 2147

2147

Xilinx 用兩個 96 位獨特器件標識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統 (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2021-01-23 06:32:33 10

10 Xilinx提供超低延時編解碼方案,在ZCU106單板上可以驗證。文檔MPSoC VCU TRD 2020.2 Low Latency XV20 提供了詳細命令。 缺省情況下,編碼使用的是PS

2021-05-07 15:30:13 6222

6222

剛學ZYNQ的時候,看到里面反復提到PS和PL,還以為PS是PhotoShop的意思,PL是哪種型號的簡稱。 稍微了解之后才知道,ZYNQ是ARM和FPGA的組合,PS是programming

2021-06-18 16:09:46 8666

8666 PS176是一個顯示端口? (DP)至HDMI? 2.0視頻接口轉換器適用于需要視頻協議轉換的電纜適配器、電視接收器、監視器和其他應用。它將接受任何顯示端口輸入格式,包括DP 1.1a、dp

2021-12-29 15:03:46 6532

6532

的協議,可用于寄存器式控制/狀態接口。例如,Zynq XADC 使用 AXI4-Lite 接口連接到 Zynq PS。

2022-05-10 09:52:12 1949

1949 MPSoC含有PS、PL;在PS和PL之間有大量接口和信號線,比如AXI、時鐘、GPIO等。缺省情況下,PS和PL之間有接口和信號線被關閉。加載bit后,軟件才會打開PS和PL之間的接口和信號線

2022-08-02 09:45:03 676

676 Xilinx提供超低延時編解碼方案,在ZCU106單板上可以驗證。文檔MPSoC VCU TRD 2020.2 Low Latency XV20 提供了詳細命令。缺省情況下,編碼使用的是PS DDR

2022-08-02 09:12:42 535

535

本應用筆記描述了使用可編程邏輯(PL)中的高速串行收發器通過擴展多路復用I/O(EMIO)接口和1000BASE?X或SGMII物理接口使用基于處理系統(PS)的千兆以太網MAC(GEM) 。

2022-09-09 10:36:03 1319

1319 電子發燒友網站提供《將Zynq PS和PL與內存映射寄存器集成.zip》資料免費下載

2022-12-06 15:14:29 2

2 S_AXI_ACP_FPD接口實現了PS 和PL 之間的低延遲連接,通過這個128位的接口,PL端可以直接訪問APU的L1和L2 cache,以及DDR內存區域。故PL側可以直接從cache中拿到APU的計算結果,同時也可以第一時間將邏輯加速運算的結果送至APU。

2023-02-01 15:36:53 1708

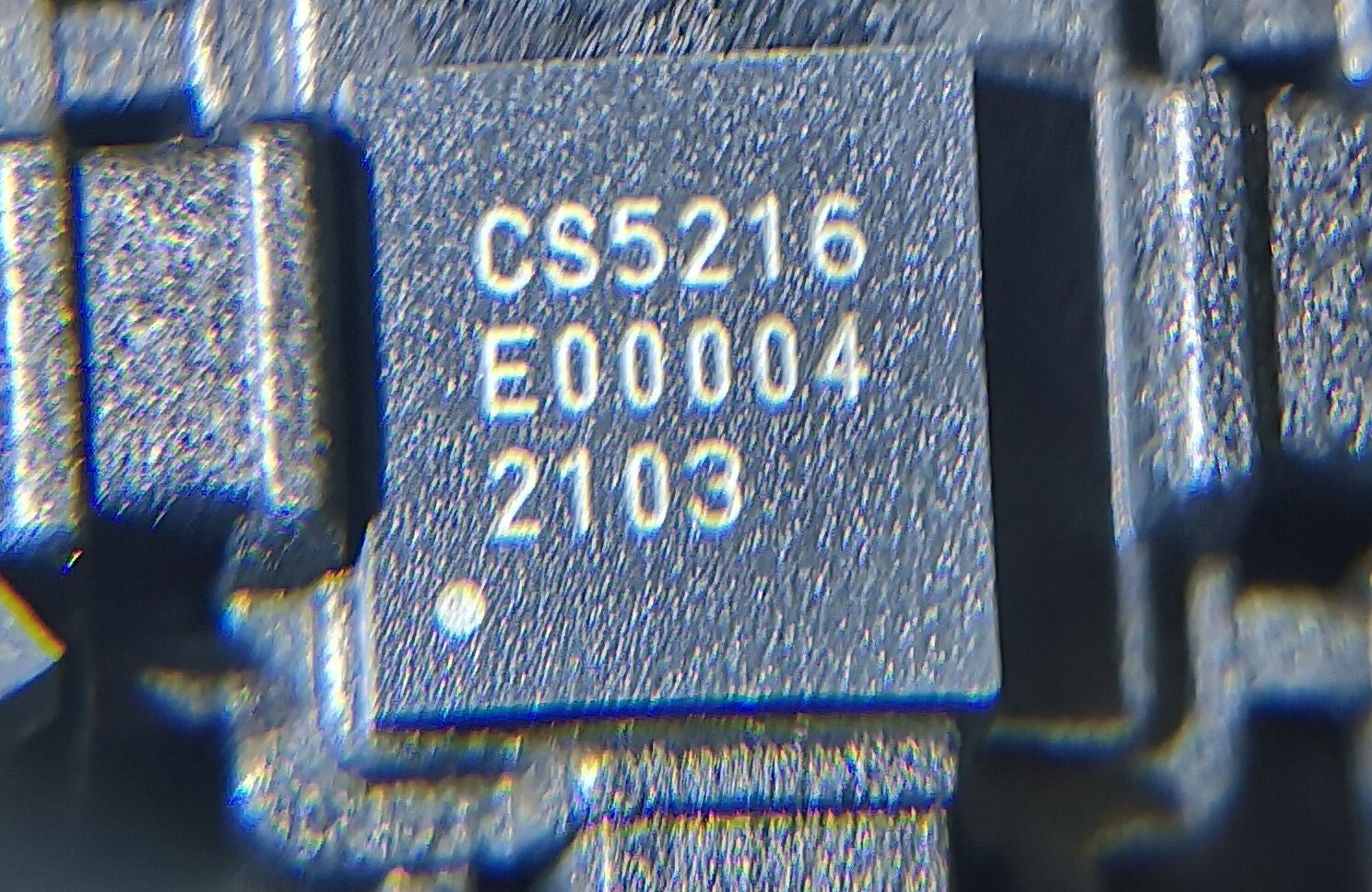

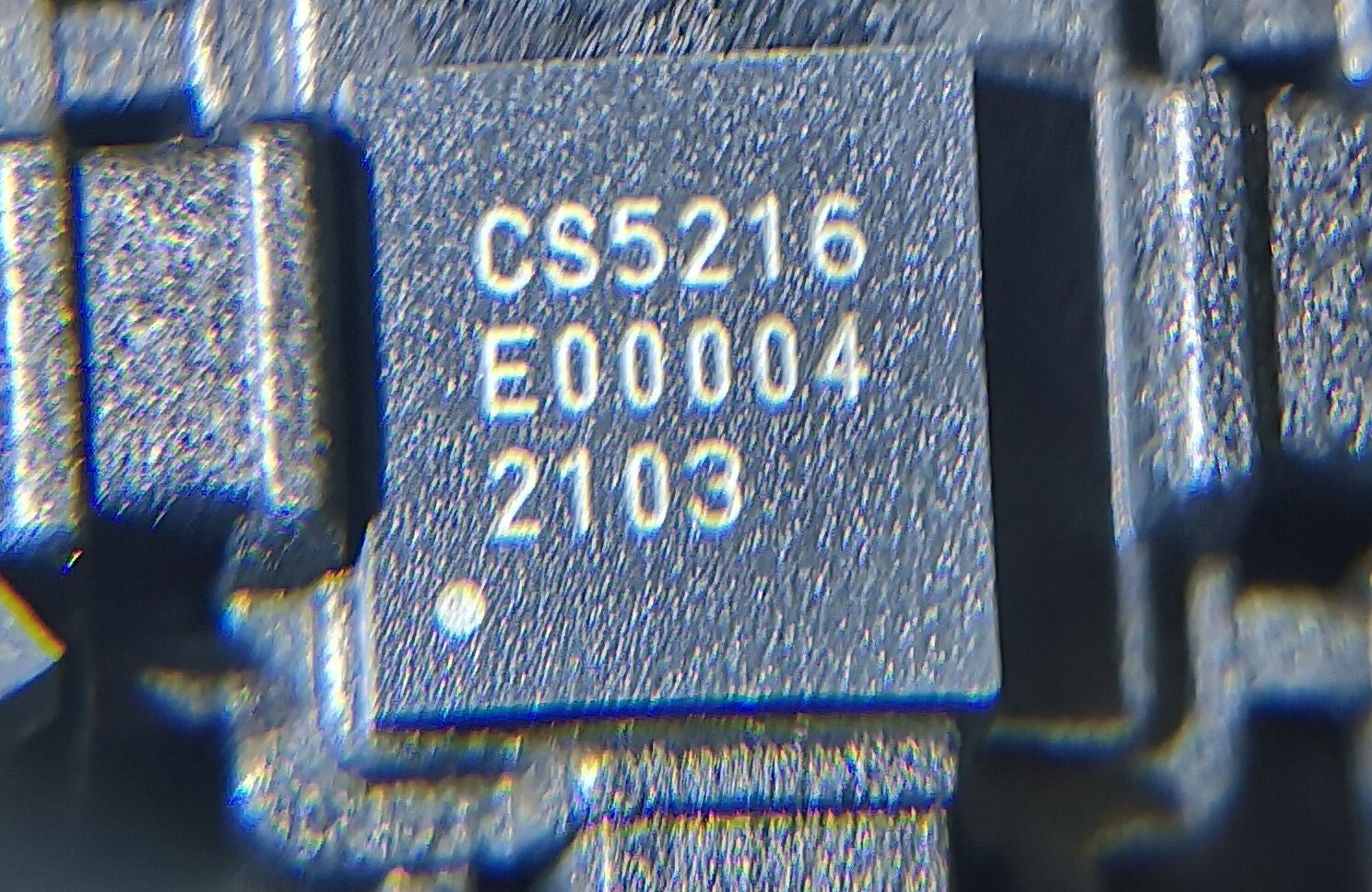

1708 CS5216 DP轉HDMI Pin to Pin替代PS8402A方案|PS8402A替代方案|替代PS8402A

2022-03-23 16:16:09 560

560

PS176替代方案|PS176 DP++? to HDMI(4K@30Hz)替代方案|CS5218替代PS176

2022-03-23 18:27:07 974

974

電子發燒友網站提供《基于PS和PL的1G/10G以太網解決方案應用筆記.pdf》資料免費下載

2023-09-15 10:29:25 1

1 電子發燒友網站提供《基于PS和PL的1G/10G以太網解決方案.pdf》資料免費下載

2023-09-15 10:05:18 0

0 驪微電子供應PL3368CPL3369C10-12W電源方案,可以直接兼容替換DP2525,更多產品手冊、應用料資請向驪微電子申請。>>

2021-12-10 15:18:06 4

4 資料\Demo\All-Programmable-SoC-demos\”目錄下。案例包含PL端Vivado工程,主要使用Xilinx提供的標準IP核配置PL端資源實現接口擴展,同時包含PS端裸機/Linu

2023-01-03 15:50:37 18

18

正在加载...

電子發燒友App

電子發燒友App

評論