串行RapidIO針對高性能嵌入式系統(tǒng)芯片間和板間互連而設計,它將是未來十幾年中嵌入式系統(tǒng)互連的最佳選擇。

????本文比較RapidIO和傳統(tǒng)互連技術的優(yōu)點;介紹RapidIO協(xié)議架構,包格式,互連拓撲結構以及串行RapidIO物理層規(guī)范。介紹串行RapidIO在無線基礎設施方面的應用。

RapidIO 與傳統(tǒng)嵌入互連方式的比較

隨著高性能嵌入式系統(tǒng)的不斷發(fā)展,芯片間及板間互連對帶寬、成本、靈活性及可靠性的要求越來越高,傳統(tǒng)的互連方式,如處理器總線、PCI總線和以太網,都難以滿足新的需求 。 ????處理器總線主要用作外部存儲器接口,如德州儀器(TI) C6000系列DSP的外部存儲器接口,可支持外接同步SDRAM、SBSRAM及FIFO,也可支持異步SRAM、FLASH等。外部存儲器接口也可用作與板內FPGA或ASIC芯片互連,這種情況下,F(xiàn)PGA或ASIC模擬一個DSP支持的存儲器接口,DSP則把FPGA或ASIC當作存儲器來訪問。 ????這類同步接口帶寬可達10Gbps,如德州儀器TMS320C6455 DSP的DDR2接口最大帶寬為17.066Gbps,SBSRAM接口最大帶寬為8.533Gbps。然而,這種接口也存在一些局限性:

接口管腳多,硬件設計困難。常見的DDR2接口有70~80個管腳;

只能用于板內互連,無法用于板間互連;

不是點對點的對等互連,DSP始終是主設備,其它器件只能做從設備。

PCI是廣泛用于計算機內器件互連的技術。傳統(tǒng)PCI技術也采樣類似于上述存儲器接口的并行總線方式,如TMS320C6455 DSP的PCI接口,有32bits數據總線,最高時鐘速度為66MHz,共有42個管腳。 ????最新的串行PCI Express技術采用與串行RapidIO(SRIO, Serial RapidIO)類似的物理層傳輸技術,使得帶寬達到10Gbps左右。 ????但由于其主要的應用仍是計算機,而且為了兼容傳統(tǒng)PCI技術,使得它在嵌入式設備方面的應用具有一定的局限性,如不支持點對點對等通信等。 ????眾所周知,以太網是使用最廣泛的局域網互連技術,它也被擴展應用到嵌入式設備互連,但它的局限性也是顯而易見的:

不支持硬件糾錯,軟件協(xié)議棧開銷較大;

打包效率低,有效傳輸帶寬因此而減小;

只支持消息傳輸模式,不支持對對端設備的直接存儲器訪問(DMA, Direct Memory Access)。

針對嵌入式系統(tǒng)的需求以及傳統(tǒng)互連方式的局限性,RapidIO標準按如下目標被制定:

針對嵌入式系統(tǒng)機框內高速互連應用而設計。

簡化協(xié)議及流控機制,限制軟件復雜度,使得糾錯重傳機制乃至整個協(xié)議棧易于用硬件實現(xiàn)。

提高打包效率,減小傳輸時延。

減少管腳,降低成本。

簡化交換芯片的實現(xiàn),避免交換芯片中的包類型解析。

分層協(xié)議結構,支持多種傳輸模式,支持多種物理層技術,靈活且易于擴展。

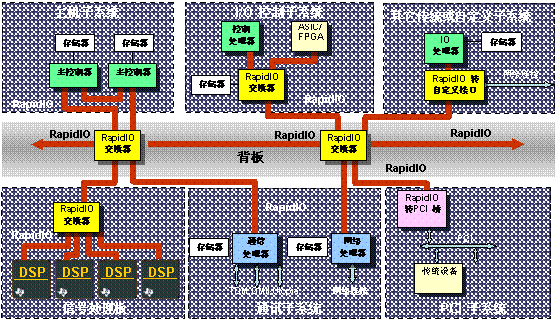

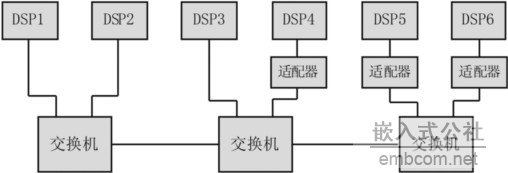

圖1展示了RapidIO互連在嵌入式系統(tǒng)中的應用。

??圖1 RapidIO在嵌入式系統(tǒng)中的應用

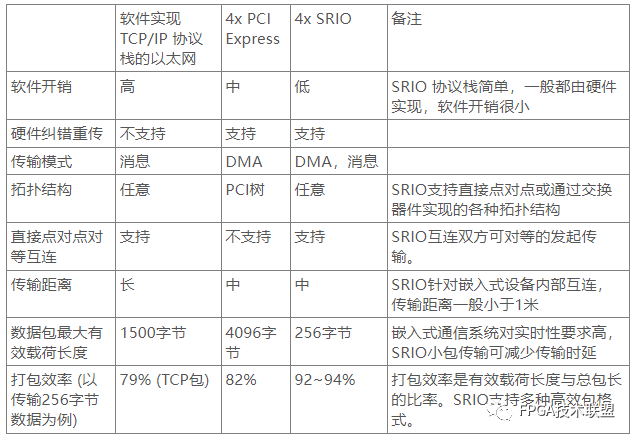

表1總結比較了的三種帶寬能達到10Gbps的互連技術:以太網,PCI Express和串行RapidIO,從中可以看出串行RapidIO是最適合高性能嵌入式系統(tǒng)互連的技術。

?表1 10G級互連技術比較

串行RapidIO協(xié)議

RapidIO行業(yè)協(xié)會成立于2000年,其宗旨是為嵌入式系統(tǒng)開發(fā)可靠的,高性能,基于包交換的互連技術。RapidIO協(xié)議的簡要發(fā)展歷史是:

2001年初,最初的標準被發(fā)布

2002年6月,1.2版標準發(fā)布

2005年6月,1.3版標注發(fā)布

串行RapidIO是物理層采用串行差分模擬信號傳輸的RapidIO標準。SRIO 1.x 標準支持的信號速度為1.25GHz、2.5GHz、3.125GHz;正在制定的RapidIO 2.0標準將支持5GHz、6.25GHz. ????目前,幾乎所有的嵌入式系統(tǒng)芯片及設備供應商都加入了RapidIO行業(yè)協(xié)會。德州儀器(TI) 2001年加入該組織,2003年成為領導委員會成員。2005年底,德州儀器(TI)推出第一個集成SRIO(Serial RapidIO)的DSP,后來又陸續(xù)推出共5款支持SRIO的DSP,這使得RapidIO的應用全面啟動。

RapidIO協(xié)議結構及包格式

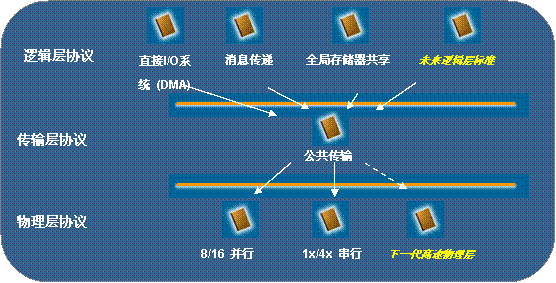

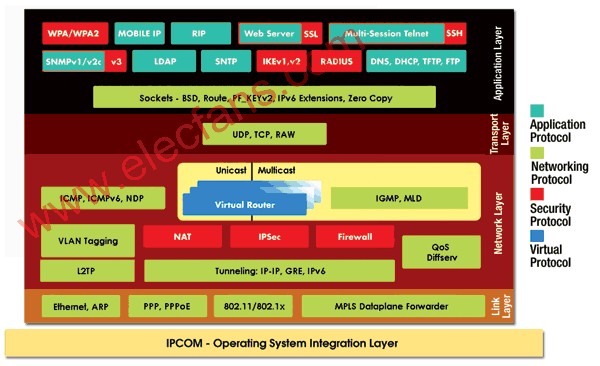

為了滿足靈活性和可擴展性的要求,RapidIO協(xié)議分為三層:邏輯層、傳輸層和物理層。圖2說明了RapidIO協(xié)議的分層結構。

圖2 RapidIO協(xié)議分層結構 ????

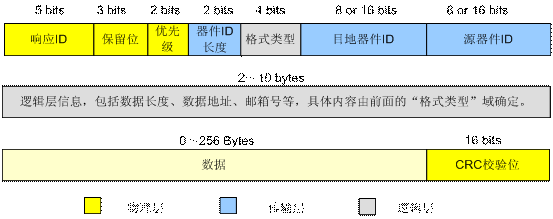

邏輯層定義了操作協(xié)議;傳輸層定義了包交換、路由和尋址機制;物理層定義了電氣特性、鏈路控制和糾錯重傳等。 ????象以太網一樣,RapidIO也是基于包交換的互連技術。如圖3所示,RapidIO包由包頭、可選的載荷數據和16bits CRC校驗組成。包頭的長度因為包類型不同可能是十幾到二十幾個字節(jié)。每包的載荷數據長度不超過256字節(jié),這有利于減少傳輸時延,簡化硬件實現(xiàn)。

圖3 RapidIO包格式 ????上述包格式定義兼顧了包效率及組包/解包的簡單性。RapidIO交換器件僅需解析前后16bits,以及源/目地器件ID,這簡化了交換器件的實現(xiàn)。

邏輯層協(xié)議

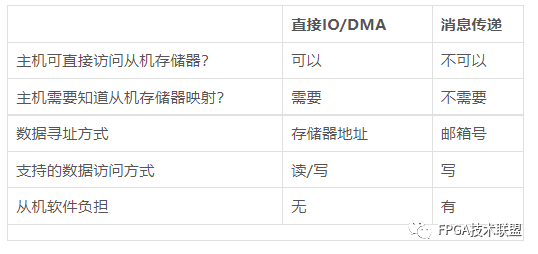

邏輯層定義了操作協(xié)議和相應的包格式。RapidIO支持的邏輯層業(yè)務主要是:直接IO/DMA (Direct IO/Direct Memory Access)和消息傳遞(Message Passing)。 ????直接IO/DMA模式是最簡單實用的傳輸方式,其前提是主設備知道被訪問端的存儲器映射。在這種模式下,主設備可以直接讀寫從設備的存儲器。直接IO/DMA在被訪問端的功能往往完全由硬件實現(xiàn),所以被訪問的器件不會有任何軟件負擔。從功能上講,這一特點和德州儀器DSP的傳統(tǒng)的主機接口(HPI, Host Port Interface)類似。但和HPI口相比,SRIO(Serial RapidIO)帶寬大,管腳少,傳輸方式更靈活。 ????對上層應用來說,發(fā)起直接IO/DMA傳輸主要需提供以下參數:目地器件ID、數據長度、數據在目地器件存儲器中的地址。 ????直接IO/DMA模式又可進一步分為以下幾種傳輸格式:

NWRITE: 寫操作,不要求接收端響應。

NWRITE_R: 帶響應的NWRITE(NWRITE with Response),要求接收端響應。

SWRITE:流寫(Stream Write),數據長度必須是8字節(jié)的整數倍,不要求接收端響應。

NREAD: 讀操作。

SWRITE是最高效的傳輸格式;帶響應的寫操作或讀操作效率則較低,一般只能達到不帶響應的傳輸的效率的一半。 ????消息傳遞(Message Passing)模式則類似于以太網的傳輸方式,它不要求主設備知道被訪問設備的存儲器狀況。數據在被訪問設備中的位置則由郵箱號(類似于以太網協(xié)議中的端口號)確定。 ????從設備根據接收到的包的郵箱號把數據保存到對應的緩沖區(qū),這一過程往往無法完全由硬件實現(xiàn),而需要軟件協(xié)助,所以會帶來一些軟件負擔。對上層應用來說,發(fā)起消息傳遞主要需提供以下參數:目地器件ID、數據長度、郵箱號。表2比較了直接IO/DMA和消息傳遞模式。 表2 直接IO/DMA和消息傳遞的對比

傳輸層協(xié)議

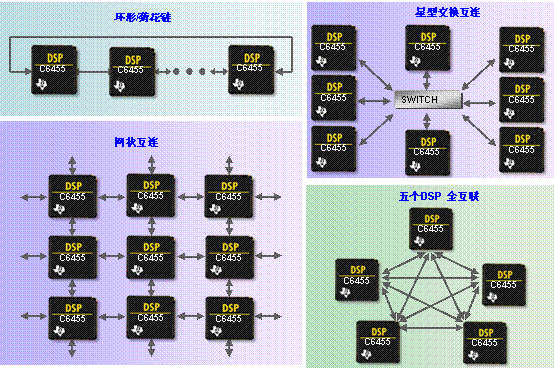

RapidIO是基于包交換的互連技術,傳輸層定義了包交換的路由和尋址機制。 ????RapidIO網絡主要由兩種器件,終端器件(End Point)和交換器件(Switch)組成。 ????終端器件是數據包的源或目的地,不同的終端器件以器件ID來區(qū)分。RapidIO支持8 bits 或 16 bits器件ID,因此一個RapidIO網絡最多可容納256或65536個終端器件。與以太網類似,RapidIO也支持廣播或組播,每個終端器件除了獨有的器件ID外,還可配置廣播或組播ID。 ????交換器件根據包的目地器件ID進行包的轉發(fā),交換器件本身沒有器件ID。 ????RapidIO的互連拓撲結構非常靈活,除了通過交換器件外,兩個終端器件也可直接互連。以德州儀器(TI)的TMS320C6455 DSP為例,它有4個3.125G的SRIO口,它可支持的拓撲結構如圖4所示

圖4 RapidIO支持靈活多樣的拓撲結構

物理層協(xié)議

RapidIO 1.x 協(xié)議定義了以下兩種物理層接口標準:

8/16 并行LVDS協(xié)議

1x/4x 串行協(xié)議 (SRIO)

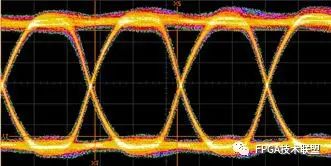

并行RapidIO由于信號線較多(40~76)難以得到廣泛的應用,而1x/4x串行RapidIO僅4或16個信號線,逐漸成為主流,所以本文僅介紹串行RapidIO。 ????串行RapidIO基于現(xiàn)在已廣泛用于背板互連的SerDes(Serialize Deserialize)技術,它采用差分交流耦合信號。差分交流耦合信號具有抗干擾強、速率高、傳輸距離較遠等優(yōu)點。差分交流耦合信號的質量不是由傳統(tǒng)的時序參數來衡量,而是通過眼圖來衡量,眼圖中的“眼睛”張得越開則信號質量越好。圖5是一個典型的串行RapidIO信號的眼圖。

圖5 串行RapidIO信號眼圖 ????差分信號的強弱由一對信號線的電壓差值表示,串行RapidIO協(xié)議規(guī)定信號峰-峰值的范圍是200mV-2000mV。信號幅度越大,則傳輸距離越遠,RapidIO協(xié)議按信號傳輸距離定義兩種傳輸指標:

短距離傳輸(Short Run),<=50厘米,主要用于板內互連,推薦的發(fā)送端信號峰-峰值為500mV-1000mV

長距離傳輸(Long Run),>50厘米,主要用于板間或背板互連,推薦的發(fā)送端信號峰-峰值為800mV-1600mV

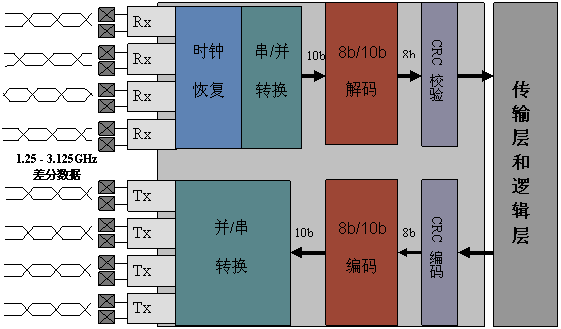

為了支持全雙工傳輸,串行RapidIO收發(fā)信號是獨立的,所以每一個串行RapidIO口由4根信號線組成。標準的1x/4x 串行RapidIO接口,支持四個口,共16根信號線。這四個口可被用作獨立的接口傳輸不同的數據;也可合并在一起當作一個接口使用,以提高單一接口的吞吐量。 ????德州儀器TMS320C6455 DSP上集成了標準的1x/4x串行RapidIO接口,如圖6所示。

圖6德州儀器TMS320C6455 DSP 1x/4x 串行RapidIO接口框圖 ????發(fā)送時,邏輯層和傳輸層將組好的包經過CRC編碼后被送到物理層的FIFO中,“8b/10b編碼”模塊將每8bit數據編碼成10bits數據,“并/串轉換”模塊將10bits并行數據轉換成串行bits,發(fā)送模塊把數字bit轉換成差分交流耦合信號在信號線上發(fā)送出去。這里的8b/10編碼的主要作用是:

保證信號有足夠的跳變,以便于接收方恢復時鐘。串行RapidIO沒有專門的時鐘信號線,接收端靠數據信號的跳變恢復時鐘。所以需要把信號跳變少的8bits數據(如全0或全1)編碼成有一定跳變的10bits數據。另外,也使得總體數據中0和1的個數均衡,以消除直流分量,保證交流耦合特性;

8b/10編碼可擴大符號空間,以承載帶內控制符號。10bits能表示1024個符號,其中256個表示有效的8bits數據,剩下的符號中的幾十個被用作控制符號。控制符號可被用作包分隔符,響應標志,或用于鏈路初始化,鏈路控制等功能;

8b/10編碼能實現(xiàn)一定的檢錯功能。1024個符號中,除了256個有效數據符號和幾十個控制符號外,其它符號都是非法的,接收方收到非法符號則表示鏈路傳輸出錯。

接收的過程則正好相反,首先接收方需要根據數據信號的跳變恢復出時鐘,用這個時鐘采樣串行信號,將串行信號轉換為10bits的并行信號,再按8b/10b編碼規(guī)則解碼得到8bits數據,最后做CRC校驗并送上層處理。 ????數據被正確的接收時,接收端會發(fā)送一個ACK響應包給發(fā)送端;如果數據不正確(CRC錯或非法的10bits符號),則會送NACK包,要求發(fā)送方重傳。這種重傳糾錯的功能由物理層完成,而物理層功能往往由硬件實現(xiàn),所以不需要軟件干預。 ????串行RapidIO支持的信號速率有三種:1.25GHz,2.5GHz,3.125GHz。但由于8b/10b編碼,其有效數據速率分別為:1Gbps, 2Gbps, 2.5Gbps。4個1x端口或一個4x端口支持的最高速率為10Gbps。

串行RapidIO在無線基礎設施上的應用

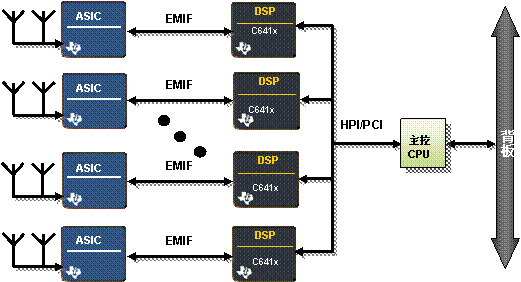

無線基礎設施如基站、媒體網關等,是典型的高性能嵌入式通信系統(tǒng),它們對互連的帶寬、時延、復雜度、靈活性、可靠性都有非常高的要求。而串行RapidIO正是滿足這些要求的最佳選擇。 ????以無線基站為例,在SRIO出現(xiàn)之前,無線基站的基帶處理的典型框圖如圖7所示。

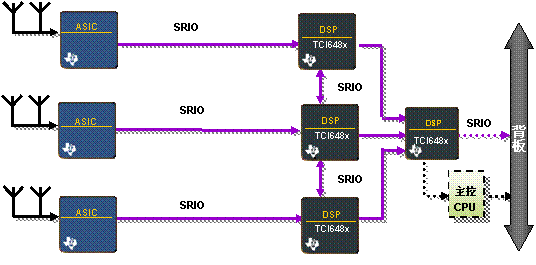

圖7 傳統(tǒng)無線基站基帶處理框圖 ????在傳統(tǒng)的基站中,DSP與ASIC或FPGA之間的互連一般用外部存儲器接口EMIF(External Memory Interface);DSP之間或DSP與主機之間一般用HPI(Host Port Interface)或PCI互連。它們的主要缺點是:帶寬小;信號線多;主從模式接口,不支持對等傳輸。另外,DSP不能直接進行背板傳輸。 ????使用SRIO(Serial RapidIO)則可有效的解決這些問題,大大提高無線基站的互連性能。圖8顯示了一種無線基站基帶互連框圖。在這里,SRIO實現(xiàn)了大部分器件之間的互連,甚至可支持DSP進行直接背板傳輸。

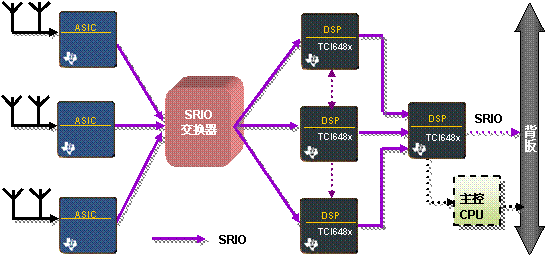

圖8 SRIO提高無線基站互連性能 ????通過SRIO交換器件互連可以進一步提高基帶處理的靈活性,圖9顯示了一種基帶SRIO交換互連的框圖。這種互連有利于實現(xiàn)先進的基帶處理資源池架構,數據可被送到任何一個通過SRIO交換器互連的處理器中,從而達到各個處理器的負載均衡,更加有效的利用系統(tǒng)的整體處理能力。

圖9 SRIO交換為無線基站基帶處理提供更大的靈活性 ????綜上所述,對嵌入式系統(tǒng)尤其是無線基礎設施,串行RapidIO是最佳的互連技術。高達10Gbps的帶寬、低時延和低軟件復雜度滿足了飛速發(fā)展的通信技術對性能的苛刻需求;串行差分模擬信號技術滿足了系統(tǒng)對管腳數量的限制,及對背板傳輸的需求;靈活的點對點對等互連、交換互連,和可選的1.25G/2.5G/3.125G三種速度能滿足多種不同應用的需求。 ????隨著串行RapidIO技術的發(fā)展成熟,以及越來越多的廠商的支持,串行RapidIO技術必將成為高性能嵌入式互連的主流技術。

編輯:黃飛

?

電子發(fā)燒友App

電子發(fā)燒友App

評論