寄存器,是集成電路中非常重要的一種存儲單元,通常由觸發器組成。在集成電路設計中,寄存器可分為電路內部使用的寄存器和充當內外部接口的寄存器這兩類。

2023-07-21 16:59:22 2761

2761

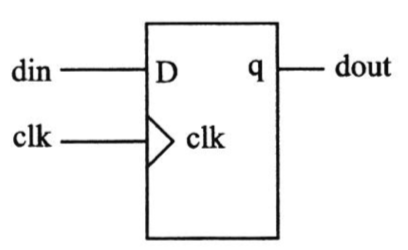

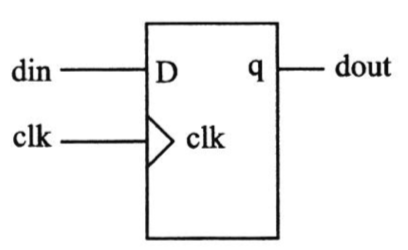

現代邏輯設計中,時序邏輯設計是核心,而寄存器又是時序邏輯的基礎,下面將介紹幾種常見的寄存器的Verilog設計代碼供初學者進行學習理解。

2023-07-27 09:03:59 1899

1899

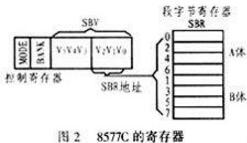

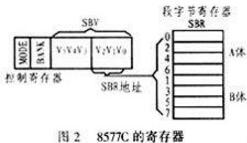

最近在玩74HC595,大學期間也玩過,只是當時沒有做筆記習慣,所以好多東西都沒有留底稿,最近一直想干點事,那就先從74HC595這個款8位移位寄存器/鎖存器(3狀態)開始吧,這款芯片有好多廠商在做

2021-12-07 07:40:09

輸出六同相緩沖/驅動器74170 TTL 開路輸出4×4寄存器堆74173 TTL 三態輸出四位D型寄存器74174 TTL 帶公共時鐘和復位六D觸發器74175 TTL 帶公共時鐘和復位四D觸發器

2011-08-01 16:25:44

我是FPGA的新手想請教一下Verilog中什么時候需要給變量定義寄存器。一開始我以為每個輸入、輸出都要定義沒定義的話默認為一,但是今天看到一段代碼輸入變量[3:0] key_in并沒有定義寄存器。

2017-01-18 19:55:47

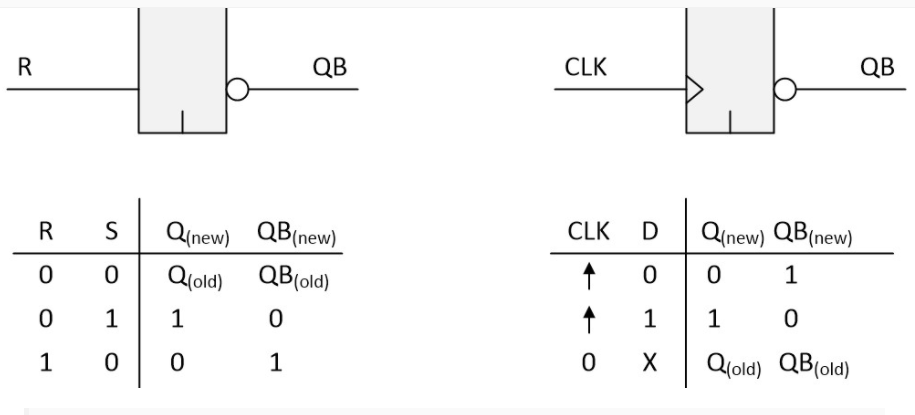

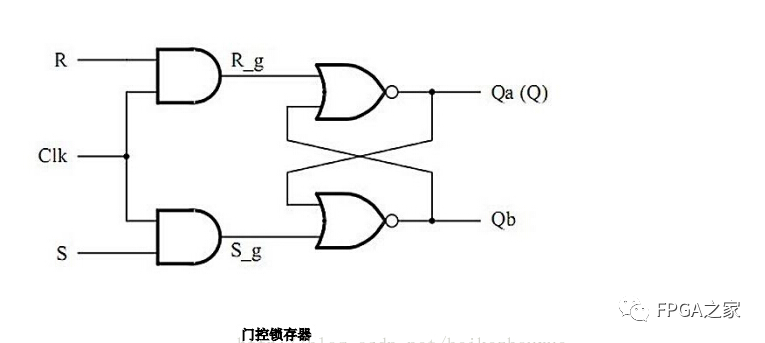

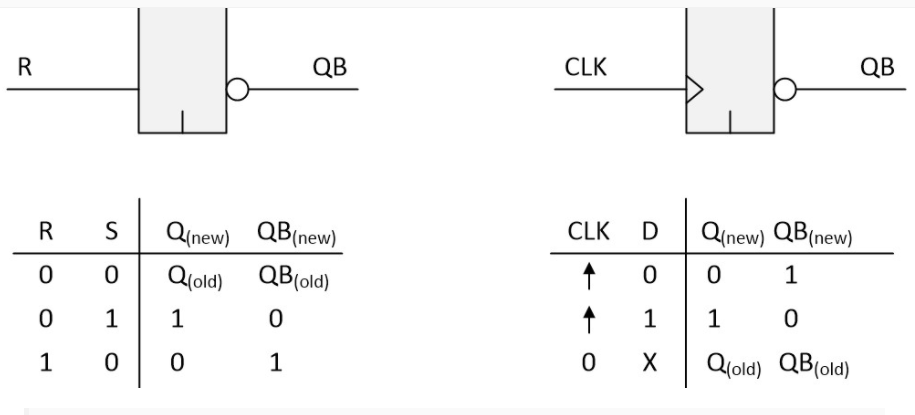

觸發器:flipflop鎖存器:latch寄存器:register鎖存器是電平觸發的存儲單元,數據存儲的動作取決于輸入時鐘(或者使能)信號的電平值,盡當鎖存器處于使能狀態時輸出才會隨著數據輸入

2019-08-27 08:30:00

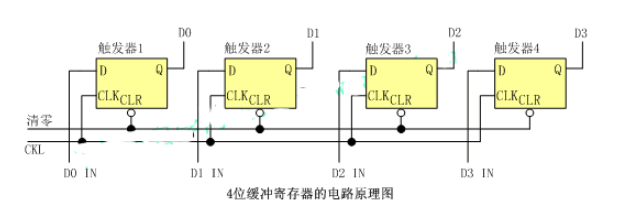

,但這種時序邏輯電路只包含存儲電路。寄存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1位二進制數,所以由N個鎖存器或觸發器可以構成N位寄存器。 工程中的寄存器一般按計算機中字節

2018-07-03 11:50:27

存儲電路。寄存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1位二進制數,所以由N個鎖存器或觸發器可以構成N位寄存器。 工程中的寄存器一般按計算機中字節的位數設計,所以一般有8位

2019-06-27 04:20:03

本帖最后由 gk320830 于 2015-3-9 20:36 編輯

寄存器電路及應用寄存器1、寄存器寄存器中用的記憶部件是觸發器,每個觸發器只能存一位二進制碼。 按接收

2010-09-18 08:40:09

寄存器?寄存器的功能是存儲二進制代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成。補充:觸發器,在數字電路系統中

2022-02-24 06:35:10

最近學了下ARM7,我發現,每個寄存器都有個32位的地址。這么說,對某個寄存器的操作,其實最根本就是對這個地址操作。而寄存器的概念就是有觸發器和控制門組成的數字電路。但我越是深究,疑惑就越多。比如:為什么用軟件能夠改變寄存器的某位的值呢?求各位討論討論

2012-04-06 13:48:35

觸發器:能夠存儲一位二值信號的基本單元電路統稱為“觸發器”。鎖存器:一位觸發器只能傳送或存儲一位數據,而在實際工作中往往希望一次傳送或存儲多位數據。為此可把多個觸發器的時鐘輸入端CP連接起來,用一個

2018-09-11 08:14:45

觸發器實驗1)熟悉常用觸發器的邏輯功能及測試方法。2)了解觸發器邏輯功能的轉換。三.實驗內容及步驟 (1) 基本RS觸發器邏輯功能測試(2) JK觸發器邏輯功能測試(3) D觸發器邏輯功能的測試

2009-03-20 10:01:05

“復位”端。具有置位、復位功能的觸發器稱為R-S觸發器。雙穩態觸發器可用來構成各種計數器、分頻器和寄存器等。射極耦合觸發器又稱施密特觸發器,其原理電路如圖2。它也由兩級反相器直接耦合而成。第一級反相器

2012-06-18 11:42:43

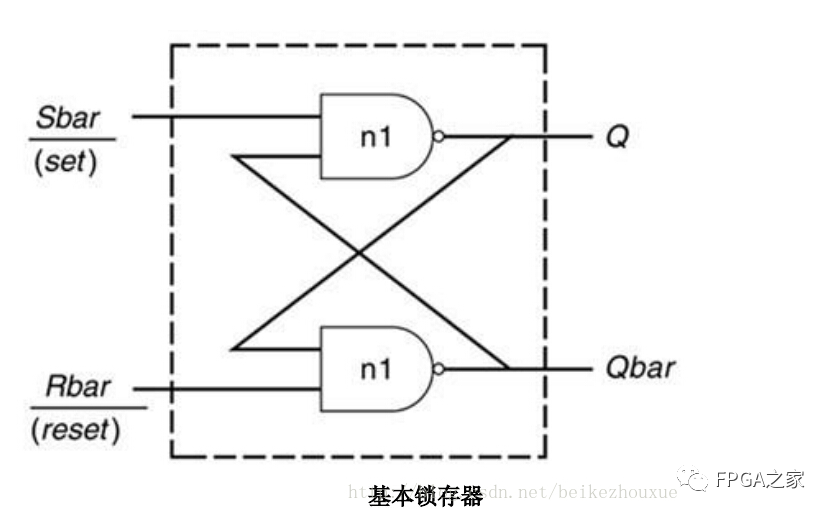

請問,鎖存器的工作原理是什么?

2013-10-15 19:35:26

的數據和運算結果,它被廣泛的用于各類數字系統和計算機中。其實寄存器就是一種常用的時序邏輯電路,但這種時序邏輯電路只包含存儲電路。寄存器的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1

2011-10-09 16:19:46

鎖存器的工作原理是什么?鎖存器的動態特性及其應用有哪些?觸發器的工作原理是什么?觸發器的電路結構是如何構成的?

2021-11-03 06:48:50

鎖存器和觸發器1.什么情況要用到鎖存器?狀態不能保持?現在的單片機狀態都是可以保持的吧2.看到很多產品用施密特觸發器作為門極驅動器(柵極驅動器),是隔離的作用還是其他?這種觸發器和專用的門極驅動器有哪些異同

2022-03-10 17:52:14

數碼管的動態顯示截取了部分程序,使用了74hc573鎖存器,但是我覺得去掉鎖存器程序照樣可以執行,那么這里使用鎖存器的意義是什么呢?還是說只是用一下沒有什么特殊的含義? for( i=0; i

2013-03-11 16:59:52

數碼管的動態顯示截取了部分程序,使用了74hc573鎖存器,但是我覺得去掉鎖存器程序照樣可以執行,那么這里使用鎖存器的意義是什么呢?還是說只是用一下沒有什么特殊的含義?

for( i=0

2023-10-26 07:18:07

前言在學習了基本鎖存器原理后,剩下就是對各個外設以及對單片機寄存器的相關學習,如果沒有看過之前對鎖存器原理的講解的同學,可以回看一下。藍橋杯基礎教程之鎖存器操作(非常重要!)學習藍橋杯必看

2021-12-03 08:05:27

的,不過一定要保證所有的latch信號源的質量,鎖存器在CPU設計中很常見,正是由于它的應用使得CPU的速度比外部IO部件邏輯快許多。latch完成同一個功能所需要的門較觸發器要少,所以在asic中用的較多。

2019-04-23 03:35:28

請教下CY8CMBR3xxx系列中的LATCHED_BUTTON_STAT寄存器鎖存機制是怎樣的?器件是在什么時候

去清除LATCHD_BUTTON_STAT?謝謝。

2024-01-24 07:43:17

今日偶然看到一些知名企業的筆試試題,隨便掃描了下,看到有幾道關于FPGA/CPLD的題目,小小的編程題,用VerilogHDL或VHDL語言編觸發器,腦袋轉了一下,模糊似乎清晰,清晰又像浸入模糊

2012-02-22 13:54:40

D觸發器中PRN、CLRN區別在Quartus II當中查看RTL視圖會有PRN和CLRN(CLR)兩個引腳的區別PRN是異步置位,可以將輸出Q置為輸入D(輸出Q立馬變成輸入D)CLRN(CLR)是異步復位,將輸出Q置地。

2022-01-11 06:43:53

(14)FPGA觸發器與寄存器區別1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA觸發器與寄存器區別5)結語1.2 FPGA簡介FPGA(Field

2022-02-23 06:16:56

指標都是有余量的。輕微的違反tSU或者tH并不會發生亞穩態,只是導致觸發器的tCO超出器件的規范(spec)。只有當數據的跳變出現在亞穩態捕捉窗口W (見圖2中的W,fs級別的時間窗口),才會發生亞穩態

2012-12-04 13:51:18

FPGA如何實現對片外寄存器的讀寫(Verilog語言)?它與單片機有區別嗎?

2016-03-24 09:40:43

操作與具有相同“置位”和“復位”輸入的先前SR觸發器完全相同。這次的區別是,即使S和R都為邏輯“ 1” ,“ JK觸發器”也沒有SR鎖存器的無效或禁止的輸入狀態。該JK觸發器基本上是一個門控SR觸發器

2021-02-01 09:15:31

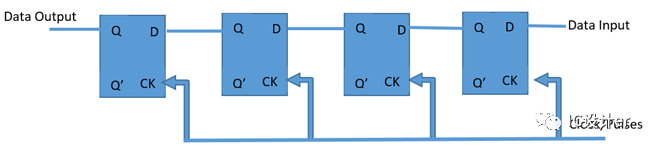

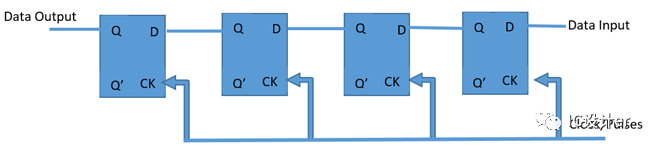

左邊一個觸發器中原來的數據(F0接收的輸入數據D1)。寄存器中的數據依次右移一位。 2、移位寄存器作用 移位寄存器是一種存儲器,存在里邊的數據可以從低位向高位移動或從高位向低位移動。例如一個8位

2019-06-20 04:20:27

【8-15】端口配置寄存器 32位IDR 數據寄存器 32位 輸入ODR 數據寄存器 32位 輸出BSRR 置位/復位寄存器 32位BRR 復位寄存器 16位LCKR 鎖存寄存器 32位3、常用的IO端口寄存器 CRL CRH IDR ODR4、CRL ...

2022-02-28 06:51:38

STM32時鐘分析寄存器:寄存器的功能是存儲二進制代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成在計算機領域

2021-08-10 06:28:45

山地車的設備配置器中,我看到了觸發器輸入和觸發通道輸入的選項。

我可以知道這兩者有什么區別,以及使用它們而不是另一個的注意事項嗎?

2024-01-24 07:53:07

jk觸發器是什么原理jk觸發器特性表和狀態轉換圖

2021-02-26 08:18:24

,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成。在計算機領域,寄存器是CPU內部的元件,包括通用寄存器、專用寄存器和控制寄存器。寄存器擁有非常高的讀寫速度,所以在寄存器之間的數據傳送非常快。STM32內部的所有寄存器都有唯一

2021-08-10 06:07:57

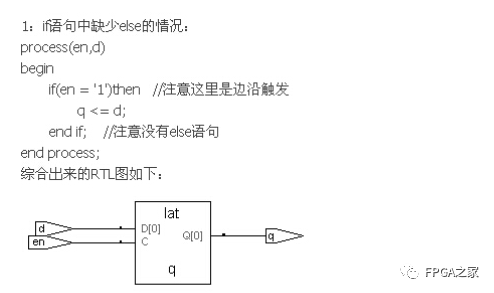

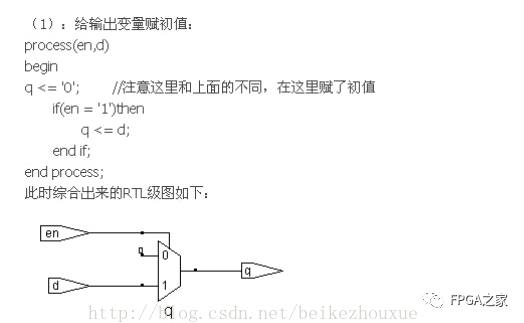

。由引可見,實現“保持不變”的關鍵在于D寄存器。眾所周知,組合邏輯代碼是沒有D寄存器的,那么它又是如何實現保持不變呢?這個就會用到鎖存器了。 上圖左邊是組合邏輯代碼,右邊是其電路。為了讓信號b保持不變

2020-03-02 00:25:31

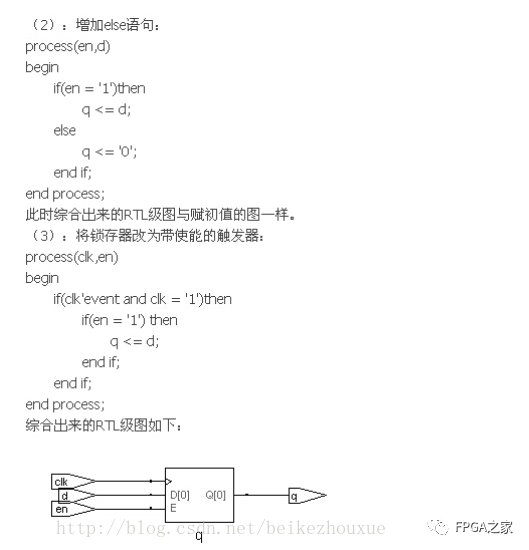

寄存器。 在FPGA設計中建議如果不是必須那么應該盡量使用觸發器而不是鎖存器。鐘控D觸發器其實就是D鎖存器,邊沿D觸發器才是真正的D觸發器,鐘控D觸發器在使能情況下輸出隨輸入變化,邊沿觸發器只有在邊沿跳

2018-10-27 22:38:21

2020.3.26_學習筆記兩個D觸發器? 最近發現一個問題,代碼中會特地的新建一個D觸發器用來鎖存信號,讓很多人都比較疑惑,明明一個D觸發器就可以檢測輸入是上升沿和下降沿。?兩個觸發器的目的主要

2021-07-30 06:44:48

根據輸入信號改變輸出狀態。把這種在時鐘信號觸發時才能動作的存儲單元電路稱為觸發器,以區別沒有時鐘信號控制的鎖存器。觸發器是一種能夠保存1位二進制數的單元電路,是計算機中記憶裝置的基本單元,由它可以組成

2019-12-25 17:09:20

你好我是Xylinx的新手,我10年前才使用Altera設計。我需要設計一個使用1GHz時鐘速度的電路來同步時鐘D-FF和移位寄存器和鎖存器。任何FPGA都可以支持這個嗎?你能給我一些關于觸發器

2020-03-30 08:45:38

光立方必須是74ALS573這種鎖存器嗎?我現在有這種74hc373d的鎖存器能用嗎?

2013-11-22 00:18:53

本帖最后由 xvjiamin 于 2021-9-26 20:46 編輯

如圖,在編寫TDC延時鏈的時候,結果通過D觸發器做鎖存。但是出現了紅色的不定態,這是為什么?該怎么解決呢?可以看到,信號

2021-09-26 20:46:03

邏輯可構成時序邏輯電路,簡稱時序電路。現在討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器。雙穩態:電子電路中。其雙穩態電路的特點是:在沒有外來觸發信號的作用下,電路始終處于原來的穩定狀態。在外

2016-05-21 06:50:08

型觸發器的Q輸出直接連接到D輸入,從而使器件具有閉環“反饋”,則連續的時鐘脈沖將使每兩個時鐘周期使雙穩態“切換”一次。在計數器教程中,我們看到了如何將數據鎖存器用作“二進制分頻器”或“頻率分頻器”以

2021-02-03 08:00:00

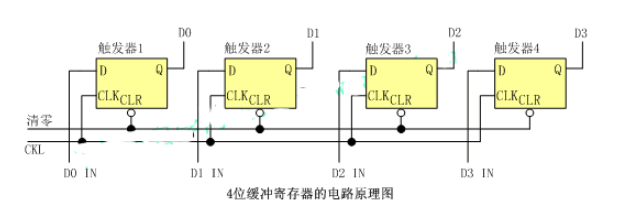

用D觸發器設計的四位移位寄存器

2016-06-13 13:05:50

邏輯,應在敏感信號表中列出所有的輸入信號;7、所有的內部寄存器都應該可以被復位;8、用戶自定義原件(UDP元件)是不能被綜合的。一:基本Verilog中的變量有線網類型和寄存器類型。線網型變量綜合成wire,而寄存器可能綜合成WIRE,鎖存器和觸發器,還有可能被優化掉。二:veril...

2021-07-29 06:10:04

如何用D觸發器設計四位移位寄存器。求程序框圖

2016-06-13 13:48:29

的存儲電路是由鎖存器或觸發器構成的,因為一個鎖存器或觸發器能存儲1位二進制數,所以由N個鎖存器或觸發器可以構成N位寄存器。(2)什么是寄存器映射由于存儲器本身沒有地址,給存儲器分配地址的過程就叫存儲器映射,在存儲器Block2 這塊區域,設計的是片上外設,它們以四個...

2022-02-28 09:36:37

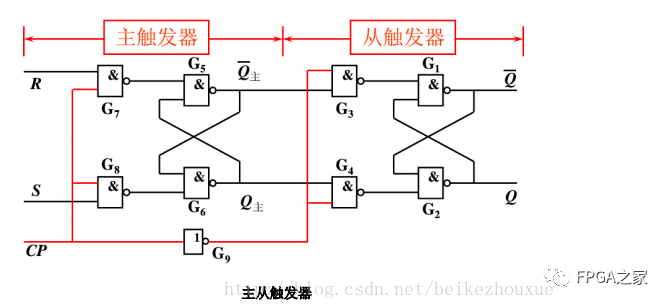

Verilog模型有哪幾種?Verilog HDL模型是由哪些模塊構成的?如何用Verilog HDL語言描述D型主從觸發器模塊?

2021-10-19 08:36:32

單片機內部有大量寄存器, 寄存器是一種能夠存儲數據的電路, 由觸發器構成。1.觸發器觸發器是一種具有記憶存儲功能的電路, 由門電路組成。 常見的觸發器包括: RS 觸發器、 D 觸發器和 JK觸發器

2022-01-20 07:13:51

`請問鎖存器下面3個針腳怎么接線?`

2014-12-28 15:45:25

想做一個基于D觸發器的寄存器,結果運行時出現這種情況,請大神指點一下

2019-06-27 10:14:56

一、定時器0/11、控制寄存器TCON為定時器/計數器T0、T1的控制寄存器,同時也鎖存T0、T1溢出中斷源和外部請求中斷源等,TCON格式如下:TCON : 定時器/計數器中斷控制寄存器 (可位尋址)]

2021-12-02 08:26:15

Chapter5 鎖存器與觸發器5.1 基本雙穩態電路一、雙穩態電路具有0 、1 兩種邏輯狀態, 一旦進入其中一種狀態,就能長期保持不變的單元電路,稱為雙穩態存儲電路,簡稱雙穩態電路。1. 最基本

2021-07-30 06:43:29

晶體管,門電路,鎖存器,觸發器的理解

2021-01-12 07:55:02

和K輸入點連接在一起,即構成一個T觸發器。應用場合:時鐘有效遲后于數據有效。這意味著數據信號先建立,時鐘信號后建立。在CP上升沿時刻打入到寄存器。

2019-06-20 04:20:50

由與非門構成的555定時器觸發鎖存電路解析

2021-04-07 06:20:04

移位寄存器概要 在數字電路中,移位寄存器(英語:shiftregister)是一種在若干相同時間脈沖下工作的以觸發器為基礎的器件,數據以并行或串行的方式輸入到該器件中,然后每個時間脈沖依次向左或

2019-06-20 04:20:29

移位寄存器概要 在數字電路中,移位寄存器(英語:shiftregister)是一種在若干相同時間脈沖下工作的以觸發器為基礎的器件,數據以并行或串行的方式輸入到該器件中,然后每個時間脈沖依次向左或

2019-06-20 04:20:47

鎖存器就是把當前的狀態鎖存起來,使CPU送出的數據在接口電路的輸出端保持一段時間鎖存后狀態不再發生變化,直到解除鎖定。還有些芯片具有鎖存器,比如芯片74LS244就具有鎖存的功能,它可以通過把一個

2022-03-01 07:00:42

電平觸發器和邊沿觸發器符號

2019-10-18 09:01:09

、BRR五、鎖存寄存器 LCKR1、LCKR六、ODR、BSRR、BRR之間的聯系與區別**既然ODR寄存器既可以輸出高電平也可以輸出低電平那么為什么還需要BSRR和BRR呢?****為什么BSRR

2022-01-18 09:15:23

預放大鎖存比較器是什么工作原理?運放鎖存器的電路結構分析如何使用Spectre預放大鎖存比較器進行仿真?

2021-04-08 06:56:02

具有三態輸出和施密特觸發器輸入的八路透明 D 類鎖存器 Number of channels (#) 8 Technology Family HCS Supply

2022-12-12 15:16:21

具有三態輸出和施密特觸發器輸入的八路透明 D 類鎖存器 Number of channels (#) 8 Technology Family HCS Supply

2022-12-12 15:16:22

具有施密特觸發輸入和三態輸出寄存器的 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology

2022-12-12 15:16:26

具有施密特觸發輸入和三態輸出寄存器的汽車類 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8

2022-12-12 15:16:35

具有輸出鎖存器的 8 位移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology Family

2022-12-12 15:18:38

具有輸入鎖存器的 8 位移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family

2022-12-12 15:18:38

具有輸出鎖存器的串行輸入移位寄存器 Configuration Serial-in, Parallel-out Bits (#) 8 Technology Family

2022-12-12 15:21:52

具有輸入鎖存器的串行輸出移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family

2022-12-12 15:21:52

具有輸入鎖存器的移位寄存器 Configuration Parallel-in, Serial-out Bits (#) 8 Technology Family LS

2022-12-12 15:21:53

寄存器與移位寄存器

寄存器是用來寄存數碼的邏輯部件,所以必須具備接收和寄存數碼的功能。任何一種觸發器都可以構成寄存器,每一個觸發器存放一位二進

2010-03-12 15:19:40 59

59 本文開始介紹了寄存器分類、特點與用途,其次介紹了觸發器的分類與觸發器的作用,最后介紹了寄存器和觸發器的區別。

2018-04-11 14:39:23 25447

25447

寄存器是由觸發器組成的,一個觸發器是一個一位寄存器。多個觸發器就可以組成一個多位的寄存器。由于寄存器在計算機中的作用不同,從而被命名不同,常用的有緩沖寄存器、移位寄存器、計數器等。下面我們就簡單的來介紹下這些寄存器的電路結構及工作原理。

2020-06-19 16:44:45 17323

17323

你有沒有遇到過這樣奇怪的事:你一直以為自己知道某件事,但當你試著向別人解釋它時,你才發現自己的論述中存在漏洞和邏輯上的差異?這就是我最近所遇到的情況,當時有人問我鎖存器和觸發器之間的區別,以及

2021-01-05 16:03:53 5109

5109

寄存器的功能是存儲二進制代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成。

2020-12-31 16:42:41 10613

10613 STM32 第二天寄存器寄存器功能:寄存器的功能是存儲二進制代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成

2021-12-08 17:36:11 18

18 (14)FPGA觸發器與寄存器區別1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA觸發器與寄存器區別5)結語1.2 FPGA簡介FPGA(Field

2021-12-29 19:41:06 1

1 寄存器?寄存器的功能是存儲二進制代碼,它是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲1位二進制代碼,故存放n位二進制代碼的寄存器,需用n個觸發器來構成。補充:觸發器,在數

2022-01-04 10:45:24 9

9 1:鎖存器、觸發器、寄存器的關聯與區別 首先應該明確鎖存器和觸發器是由與非門之類的東西構成。尤其是鎖存器,雖說數字電路定義含有鎖存器或觸發器的電路叫時序電路,但鎖存器有很多組合邏輯電路的特性

2022-12-19 12:25:01 8206

8206 觸發器也是單個寄存器,當一個寄存器設計有多個觸發器時,可以存儲一位,可以容納更多位數據。最后,移位寄存器是一種用于存儲或傳輸數據的邏輯電路。

2023-01-06 14:22:09 1067

1067 你有沒有遇到過這樣奇怪的事:你一直以為自己知道某件事,但當你試著向別人解釋它時,你才發現自己的論述中存在漏洞和邏輯上的差異?這就是我最近所遇到的情況,當時有人問我鎖存器和觸發器之間的區別,以及為什么它們都與寄存器有關。

2023-01-30 15:21:15 2666

2666 帶輸入觸發器的 8 位移位寄存器-74HC_HCT597

2023-02-15 19:01:46 0

0 帶輸入觸發器的 8 位移位寄存器-74HC_HCT597_Q100

2023-02-15 19:01:59 0

0 cpu寄存器和存儲器的區別 寄存器存在于CPU中,速度很快,數目有限;存儲器是內存,速度稍慢,但數量很大。寄存器的功能是存儲二進制代碼,是由具有存儲功能的觸發器組合起來構成的。一個觸發器可以存儲

2023-03-21 15:12:16 866

866 移位寄存器是一種時序邏輯電路,能夠存儲和傳輸數據。它們由觸發器組成,這些觸發器的連接方式使得一個觸發器的輸出可以作為另一個觸發器的輸入,具體取決于所創建的移位寄存器的類型。

2023-09-20 10:44:13 2470

2470

電子發燒友App

電子發燒友App

評論