Aurora 是一個很高效的低延遲點對點的串行協(xié)議,它使用了GTP收發(fā)器。它旨在隱藏GTP的接口細節(jié)和開銷。

2018-01-26 09:46:59 11614

11614

firmware文件夾下只有ipnc_rdk_fw_m3video.xem3和ipnc_rdk_fw_m3vpss.xem3兩個M3核固件更新生成,而DSP核的固件ipnc_rdk_fw_c6xdsp.xe674

2020-08-19 09:41:08

本帖最后由 黎釋 于 2017-5-17 16:57 編輯

我在FPGA中調用AURORA_8b10b核時,發(fā)現(xiàn)在接受端RX_SRC_RDY_N一直為低電平,也就是說一直在接受數(shù)據(jù),可是我在

2017-05-17 16:55:51

小弟最近在調用Aurora 8b/10b IP模塊時,在用modelsim功能仿真時,一切正常。 但是直接使用了例化后的example,并將Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

使用ISE 14.1,我試圖在Virtex-4 FX中生成一個簡單的Aurora 8B / 10B內核。核心似乎生成(生成完整的.vhd函數(shù)模型文件),但不會在.vho文件中生成任何代碼以實例化到我

2019-03-20 15:43:41

我開發(fā)了一個應用程序,包括Userapp,Aurora IP 8b10b v8.3,兩個FIFO(Tx和Rx)和sram模塊。我使用ISim模擬了總應用程序。我得到了所需的結果。現(xiàn)在,我的疑問

2020-03-30 08:49:04

最近使用V6130T和75T鏈接,aurora8B10BIP核,ISE14.5.上電以后可以channelup正常,一旦FPGA別的部分開始工作,電流變大了就發(fā)現(xiàn)數(shù)據(jù)出錯,有softerror。改變

2015-03-06 10:52:56

現(xiàn)象描述:仿真器直接連接開發(fā)板,編譯鏈接下載仿真程序都沒有問題,運行正常。生成ldr文件燒寫到flash之后無法正常啟動。生成和燒寫ldr的方法都沒有問題,已經回讀驗證過,板子上的啟動管腳狀態(tài)正常,可能是什么原因?

2018-08-28 11:48:39

你好!我現(xiàn)在在嘗試電路板上TMS320C6670 雙核驅動調試。發(fā)現(xiàn)調試存在問題。當我將.txt放在L2SRAM中時,調試正常。但當我將.txt.放在共享內存中時,出現(xiàn)有的斷點無效,及有些判斷

2018-06-21 17:12:52

您好!

我們現(xiàn)在遇到這樣一個問題:

C6678的電源、時鐘、復位已全部完成,并且復位狀態(tài)信號RESETSTAT也已經拉高,覺得通過這個信號可以看出芯片復位已經完成,但是通過仿真器連接,核0連接不上

2018-06-21 03:03:27

嗨,核納米板 stm32l432kc 上的 HSE 值是多少?未來:24MHz 晶體但是當我在 cubemx 中初始化默認設置時,它將 HSE 設置為 8 MHz。在船上用戶手冊中找不到船上 HSE 的價值。

2022-12-28 06:36:15

)在CCS串口欄或其他串口調試工具上可以看到M核的輸出信息。04程序實測我們以gpio_led_blink為例,來演示硬件仿真功能。(1)將am62-mcu-m4f0_0-fw放至開發(fā)板,這一步必須有

2023-03-31 11:40:45

ATK-DAP仿真器 BURNER 5V

2023-03-28 13:05:53

ATK-HSDAP仿真器 BURNER

2023-03-28 13:05:52

你好, 我正在使用Aurora 8B / 10B v5.3 IP內核,Virtex 5 FPGA用于使用SFP電纜的GB收發(fā)器。我使用核心生成器創(chuàng)建了IP核,獲得了示例設計(所有文件)。我模擬了示例

2020-04-07 14:52:25

DAP仿真器 BURNER

2023-03-28 13:06:20

,而且不知道怎么把小數(shù)生成Hex文件存到ROM里面,于是把數(shù)據(jù)擴大了2^12倍。之前用產生的余弦函數(shù)來試得到的結果是對的,fft之后就是一條線譜。我是用的DSP builder調用fft ip核來做

2016-04-21 20:36:18

的基礎上,給出了一種仿真調試方 案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結構分析OpenCores網站提供的OC8051 IP核

2012-08-11 11:41:47

例程

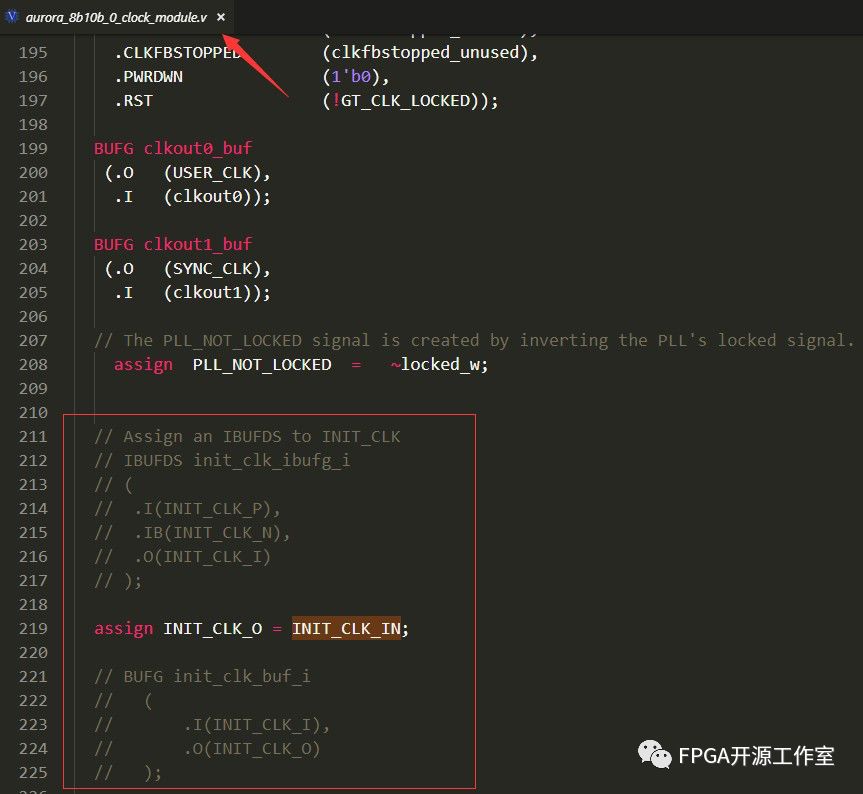

右鍵點擊剛生成的IP,選擇“Open IPExample Design”,打開IP對應配置下的測試工程,選擇指定路徑,自動打開新生成的測試工程。

4、閱讀示例工程,仿真分析

工程中包含了時鐘

2023-11-17 11:09:22

Vivado:2016.4FPGA:xcvu190Hello,我在兩個xcvu190平臺之間遇到Aurora 64B66B IP(v11.1)的一些問題。使用x4 GTY通道將IP配置為全雙工,成幀

2018-09-28 11:29:48

IP核生成文件:XilinxAlteraIP 核生成文件:(Xilinx/Altera同) IP 核生成器生成ip 后有兩個文件對我們比較有用,假設生成了一個 asyn_fifo 的核,則

2012-08-12 12:21:36

我制作了一個Aurora 64/66項目。 6.25 Gb / s,250 Mhz參考時鐘。看一下生成的示例設計。在UCF的示例設計中,我生成了Xilinx工具#50 MHz板時鐘約束NET

2020-07-27 12:10:28

本帖最后由 elecfans跑堂 于 2015-9-7 13:54 編輯

一個項目里有IP核rom,想改其中的參數(shù)重新生成,結果打開失敗,然后我把它移除了,在項目里邊新添加不了,提示如下錯誤

2015-09-07 12:21:59

PCB板上的高速信號需要進行仿真串擾嗎?

2023-04-07 17:33:31

最近在做FFT IP核,,走了好多彎路,LISENCE激活過了0034的IP核,通過修改LISENCE.DAT的方法。后來生成FFT的時候卡住,又嘗試了關閉quartus_map進程和重裝jre

2019-04-03 16:16:21

請問一下,我使用QuartusII 13.0 生成不了Rapid IO IP核,iP核已破解,其他諸如FIR、CIC、NCO等都能正常生成,到底是怎么回事呢?是Quartus版本的問題嗎?

2017-07-17 16:23:29

ST-LINK仿真器 BURNER 5V

2023-03-28 13:06:38

創(chuàng)建項目時,我無法添加 touchGFX 生成器,并且在版本 4.16 的發(fā)行說明中它說:“TouchGFX 生成器以前可用于具有雙核 MCU 的項目盡管尚未支持 H747* 和 H745*。”我還可以獲取 touch GFX 軟件使用的項目來生成在創(chuàng)建圖形應用程序時編程到評估板的二進制文件

2022-12-28 08:33:03

USB Blaster仿真器 BURNER 5V

2023-03-28 13:06:20

在vivado生成ip核后缺少一大片文件,之前是可以用的,中途卸載過Modelsim,用vivado打開過ISE工程,因為工程中很多IP核不能用所以在重新生成過程中發(fā)現(xiàn)了這個問題,還請大神告知是怎么回事?

2023-04-24 23:42:21

在仿真fft ip核時 輸出信號一直為0,檢查了輸入波形,應該沒有問題,大家?guī)兔纯窗奢斎胧怯蓃om里面的mif文件產生的信號。

2017-11-21 10:44:53

我用quartus II調用modelsim仿真fft ip核,仿真結束后我想驗證下數(shù)據(jù)是否正確,結果是:我用matlab生成同樣的整形數(shù)據(jù),然后用modelsim仿出的結果txt文件與用

2012-09-20 12:48:37

我調用了一個ip核 在下載到芯片中 有一個time-limited的問題 在完成ip核破解之后 還是無法解決 但是我在Google上的找到一個解決方法就是把ip核生成的v文件加到主項目文件中就是上面

2016-05-17 10:28:47

請教各位大神,小弟剛學FPGA,現(xiàn)在在用spartan-3E的板子,想用上面的DDR SDRAM進行簡單的讀寫,用MIG生成DDR核之后出現(xiàn)了很多引腳,看了一些資料也不是很清楚,不知道怎么使用生成的這個IP核控制器來進行讀寫,希望大神們稍作指點

2013-06-20 20:43:56

modelsim 仿真 altera IP核(ROM,RAM實例)急求大神們ROM和RAM 的綜合仿真代碼

2015-11-19 21:02:57

modelsim仿真fftip核方法:重點有3:1,添加庫文件方式正確2,添加編譯文件,要包括.vo文件3,仿真時要重新再添加一下庫文件

2013-05-12 14:05:12

本帖最后由 liu1032042013 于 2017-5-3 22:16 編輯

使用quartus 12.1生成NCO IP 核失敗,進度條一直卡著不動,經百度得網友分享的方法,成功解決問題

2017-05-02 21:39:22

quartus 11.0 IP核的simulation如果勾選 就生成不出IP核出錯,但是不選的話就沒辦法RTL仿真 求大神問題原因或者解決方法

2016-11-25 20:39:45

用的xilinx的FFT 9.1版本的ip核 , 仿真出來的結果和我MATLAB算出來的結果差的很多,也沒有倍數(shù)關系,scaled因數(shù)改了好幾次,沒有溢出,波形大致相同,但是數(shù)值上差的太多,已經弄了快兩周了,求做過這個的講講經驗。

2018-07-10 16:16:31

相關、下載仿真。添加信號:時鐘配置:仿真波形如下,分析與上一篇是一樣的,這里不再詳細說明。對于SignalTap Ⅱ和Modelsim的使用經過這幾個IP核的學習應該算是熟悉了,其實使用是次要的,主要

2016-10-11 22:24:16

Aurora最新實驗室記錄視頻。注意,右上角相機為老式磁帶相機,時間軸對不準

2014-01-29 12:18:28

你好!我正在使用Aurora 64/66示例設計項目(4個通道),每個clk發(fā)送8幀。當使用我的Vivado調試工具從我的K7開發(fā)板獲取RX數(shù)據(jù)時,在最后一幀(如

2019-04-10 09:57:31

用 quartus 生成一個ddr2的ip核,選擇了生成仿真模型,但生成不了,文件目錄下沒有example.v,只有一個對應 的sdc文件 。 另外生成報告里還有 一個warning ,,求指導

2017-09-07 11:48:09

本帖最后由 Laputa_fly 于 2013-11-23 13:46 編輯

用quartus9.0調用了altera FFT IP 核 生成了modisim 和 matlab 的仿真文件。用modelsim 仿真有結果。但是按照官方的使用說明用matlab仿真時出現(xiàn)問題。請大家?guī)兔鉀Q一下。謝謝!

2013-11-23 13:43:41

1、在Picorv32 / 蜂鳥E203軟核上運行RT-Thread 首先介紹一下我用的 FPGA 開發(fā)板,也就是荔枝糖(EG4S20),這塊開發(fā)板性價比應當算是很高了,100RMB有20K邏輯

2022-09-16 16:15:39

在quartus II13.0版本上調用FFT IP核并進行modelsim-altera仿真,在生成IP核時,step2中勾選generate simulation model、generate

2016-10-07 22:23:33

樹莓派Pico采用他自己的處理器RP2040,雙核M0,133MHz。為了體驗它的雙核編程環(huán)境和性能,我用它來實現(xiàn)一個AppleII仿真,當然是在AppleWin代碼基礎上移植改造的。Core0用作

2022-05-24 20:58:55

基于FPGA的FFT和IFFT IP核應用實例AT7_Xilinx開發(fā)板(USB3.0+LVDS)資料共享騰訊鏈接:https://share.weiyun.com/5GQyKKc百度網盤鏈接

2019-08-10 14:30:03

導入(2) 編譯與仿真(3) 綜合(4) IP核封裝(5) IP核測試基于創(chuàng)龍科技TLK7-EVM開發(fā)板,是一款基于Xilinx Kintex-7系列FPGA設計的高端評估板,由核心板和評估底板組成

2021-02-19 18:36:48

文章,小編就將以飛凌嵌入式的OKMX8MP-C開發(fā)板為例,為大家介紹多核異構處理器M核程序的啟動配置、程序編寫和實時仿真的過程。飛凌嵌入式OKMX8MP-C開發(fā)板所搭載的NXP i.MX8M Plus處理器

2023-02-21 16:08:17

如何仿真IP核(建立modelsim仿真庫完整解析)

2012-08-15 13:16:12

你好,我正在嘗試使用Aurora 8B / 10B建立僅傳輸(流媒體)。現(xiàn)在使用Vivado 2014.4進行模擬階段。我知道GTXE2_COMMON原語需要在設計中使用以包含一個QUAD PLL

2020-08-14 08:49:13

嗨,我正在嘗試將Aurora與Virtex-6 LX240t配合使用。示例設計是由核心生成器(11.5和12.1)生成的測試代碼。當我使用環(huán)回模式(近端PCS和PMA)進行測試時,兩者都能正常工作

2020-06-02 13:14:40

嗨, 我在自定義板(Kintex 7)中為Aurora 8b10b創(chuàng)建了兩個項目。Aurora Simplex_Tx和Aurora Simplex _RX。我想將這些設計整合在一起。我已將Rx的源文件添加到Tx項目中。我應該將Rx項目的XDC文件添加到Tx項目中嗎?謝謝,Abinaya

2020-08-17 09:59:17

在使用Aurora時,我可以決定是否發(fā)送數(shù)據(jù)嗎?非常感謝您的幫助。

2020-07-25 11:22:01

本文在分析OpenCores網站提供的一款OC8051IP核的基礎上,給出了一種仿真調試方案;利用該方案指出了其中若干邏輯錯誤并對其進行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

的經驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現(xiàn)在有一些經驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

HI可以兩個或多個BD地址,動態(tài)改變在一個板上生成使用PSoC Creator?最好的問候,Yoshizu

2019-10-22 06:14:47

我的quartus ii 版本13.1fft核版本13.1 modelsim版本64位 10.4在quartus ii 中使用rtl仿真時(已經在quartus ii中編譯成功) 彈出

2019-02-26 16:21:08

在開發(fā)板上正常運行的程序生成.hex文件后無法在proteus上仿真,用到了外部中斷和systick定時器,配置的引腳也完全沒反應

2023-09-25 07:07:05

本帖最后由 yirenonege 于 2012-5-17 10:05 編輯

用 core insert生成的核怎么刪掉啊?以前沒有過ISE,工程下面的文件也太多了另外如何觀測兩個模塊之間的連線

2012-05-13 18:22:51

fft仿真沒有輸出,初始值不正常,但上板驗證沒問題,試過重新生成ip核沒有用,請教一下是什么問題。

2019-05-10 10:27:57

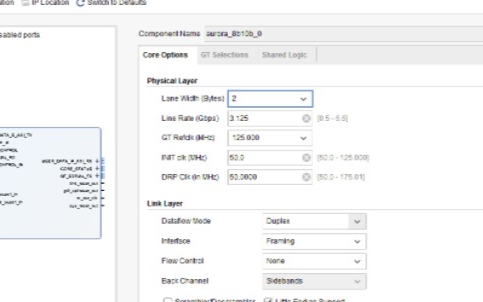

我使用Aurora(5.2)內核在125MHz GT REFclock上運行光纖,核心表示將使用2.5Gbps的線速(線寬為16位)。我現(xiàn)在需要發(fā)送更高分辨率的圖像,看不出核心生成器如何生成

2019-06-20 15:26:44

IMX6Q四核開發(fā)板,怎么做到分核運行?

2022-01-10 06:59:30

沒用過ISE,不知道生成的IP核文件夾中 ,哪些是需要添加到modelsim中用于仿真的文件 。拿ram舉例,仿真庫文件還應該添加哪些內容。希望大神們指導下 多謝

2018-12-18 17:58:32

請問為什么生成FFT ip 核會卡在生成這一步,前兩天還好好的。求大神的解決辦法,網上實在找不到方法

2016-11-01 13:42:43

如題,調用altera公司的FFT IP核,用的是13.1版本,將modulsim仿真的結果輸入到matlab畫出頻譜圖,功能仿真結果沒有問題,但門級仿真中除了原頻率信息外,出現(xiàn)了很多不存在的頻率

2018-08-28 20:43:56

高速DAP仿真器 BURNER

2023-03-28 13:06:20

描述了利用Vega Prime生成紅外場景的方法,針對該方法在成像制導仿真系統(tǒng)應用中出現(xiàn)的問題進行了討論。介紹了地形場景模型的建立方法;分析了制導仿真圖像生成、仿真數(shù)據(jù)流程等方

2011-05-19 18:25:30 0

0 基于8051的Proteus仿真-DAC0832生成鋸齒波

2016-09-01 23:28:14 42

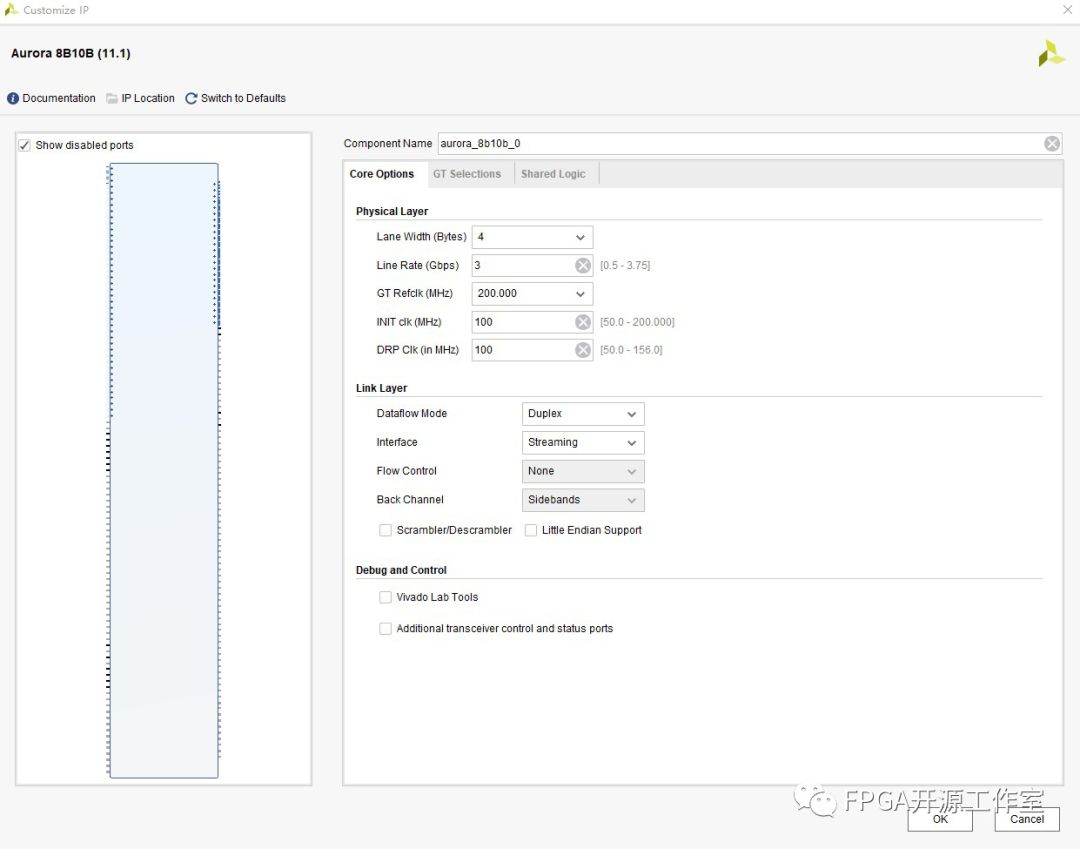

42 Aurora 是賽靈思的高速串行通信協(xié)議,一直在行業(yè)內非常受歡迎。當某些應用領域中的行業(yè)協(xié)議實現(xiàn)過程太過復雜或者太耗費資源時,Aurora 通常是首選方案。Aurora 能實現(xiàn)低成本、高數(shù)據(jù)速率

2017-11-17 05:31:09 2090

2090

Aurora系統(tǒng)被關注,源于2019年6月,國外媒體注意到華為在自家產品測試Aurora系統(tǒng)的消息。在國外媒體更早關于該系統(tǒng)的報道中,他們發(fā)現(xiàn)開發(fā)Auroa系統(tǒng)的公司早在2015年就被俄羅斯巨商收入麾下。

2019-08-29 14:37:10 4271

4271 在AWS re:Invent上,AWS發(fā)布了新一代Aurora Serverless,以及一個讓客戶能更輕松的從SQL Server遷移到Amazon Aurora PostgreSQL的新功能

2020-12-03 10:38:28 1666

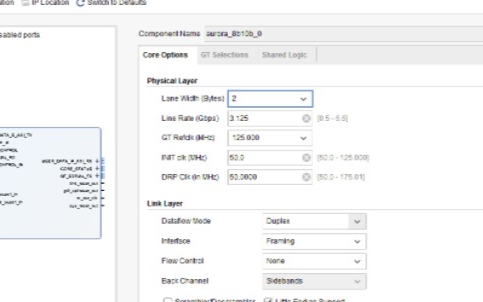

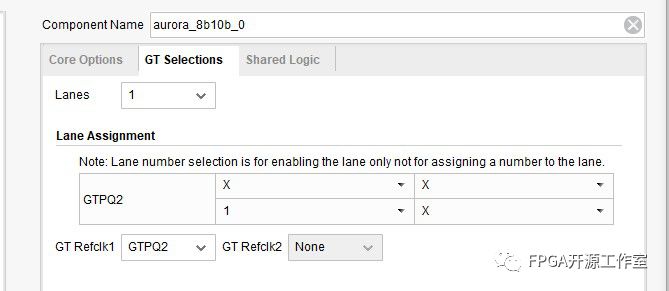

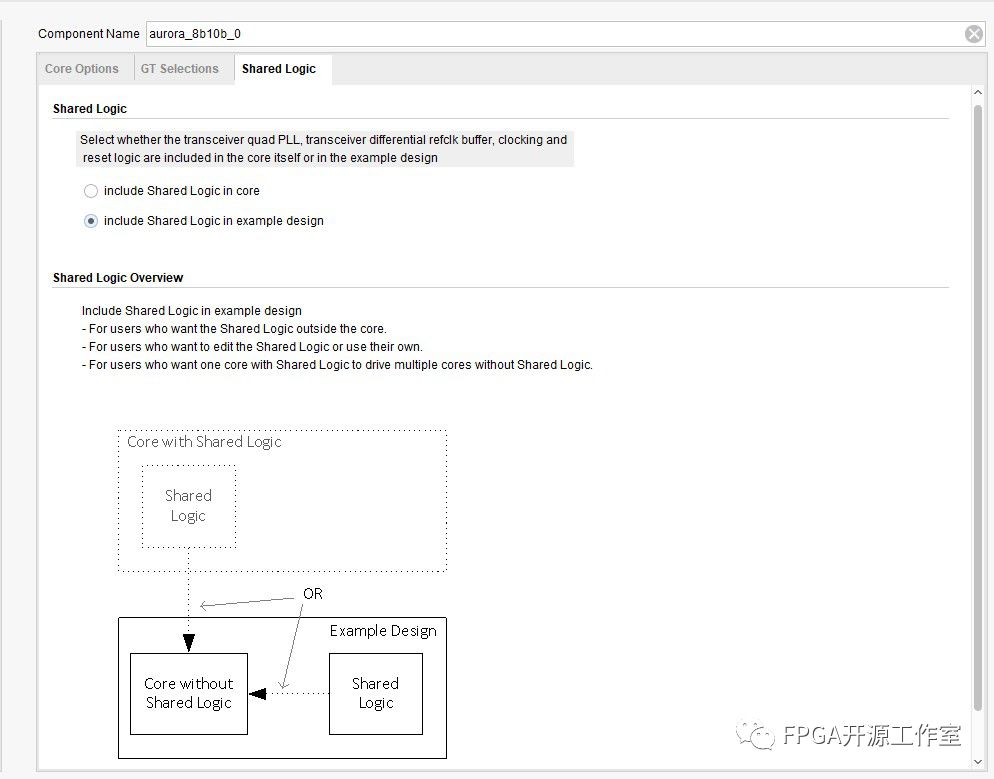

1666 開門見山的說,跟DDR/PCIE/GTX這種復雜的IP相比,

Aurora配置那是相當?shù)暮唵巍W咧?/div>

2022-02-19 18:52:10 6548

6548

Aurora 是一個用于在點對點串行鏈路間移動數(shù)據(jù)的可擴展輕量級鏈路層協(xié)議。這為物理層提供透明接口,讓專有協(xié)議或業(yè)界標準協(xié)議上層能方便地使用高速收發(fā)器。雖然使用的邏輯資源非常少,但 Aurora

2022-02-19 18:21:55 6013

6013

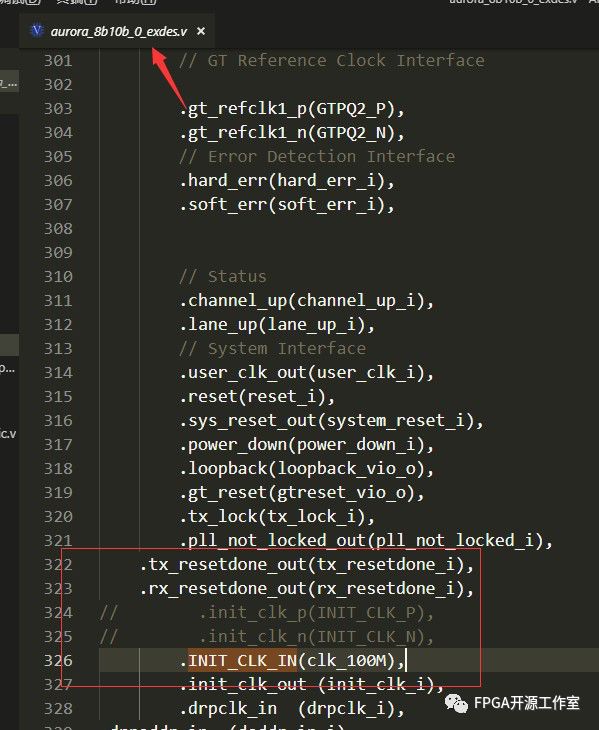

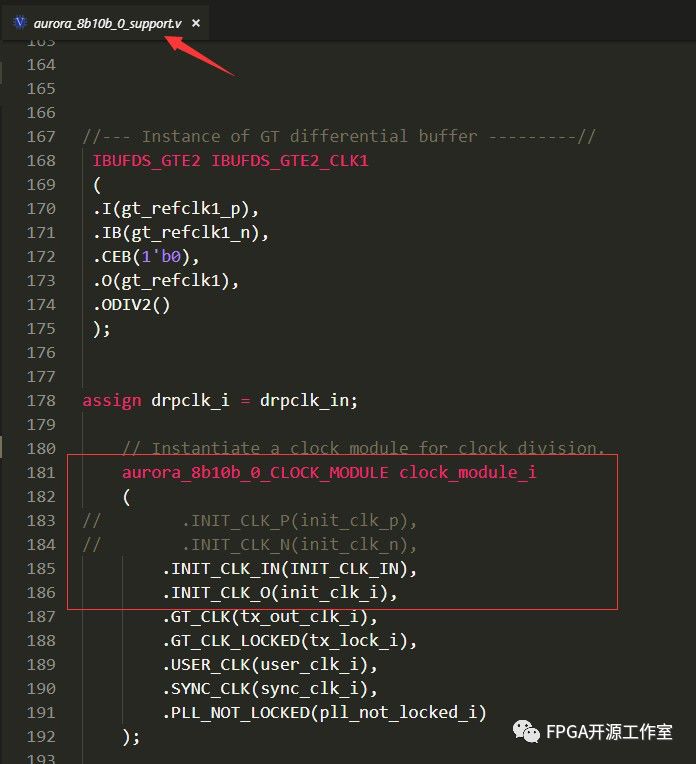

在Vivado軟件中,我們生成好IP后可以可以打開帶有例子的工程,進行仿真查看LANE_UP和CHANNEL_UP信號拉高后,即可認為光纖通道初始化成功,在對其數(shù)據(jù)接口進行查看,官方給的例程主要分為三大塊,數(shù)據(jù)產生模塊、光纖傳輸模塊、數(shù)據(jù)檢查模塊 。

2023-03-30 09:28:46 1012

1012 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論