對于提高單片機系統設計,提高系統的可靠性顯得尤為重要。對單片機系統而言,干擾因素有兩種,一是來源于系統外部環境和其它電氣設備產生的干擾,通過傳導和輻射等途徑影響單片機系統正常工作;二是來源于系統內部,由系統結構、制造工藝等決定以及內部元器件在工作時產生干擾,通過地址、電源線、信號線、分布電容等傳輸,影響開關電源模塊系統工作狀態。

一. 什么是干擾源?

干擾源是指產生干擾的元件、設備或信號。產生的干擾包括:

(1)電磁干擾,如繼電器開關啟動、靜電放電、電網電壓波動等都可能引起不同程度的瞬變浪涌電壓,會造成IC和半導體器件PN結燒毀、氧化層擊穿等。

(2)人為干擾,如機械振動、繼電器觸點抖動、元器件安裝和電路板布線引起的電磁耦合、接插件接觸不良、虛焊、放大器自激、電源紋波等。

(3)環境因素干擾,如噪聲和環境溫濕度、以及太陽黑子的變化,空間粒子輻射等。

每一個設備干擾造成的誤操作,可能運行千次才出現一次,甚至是上萬,百萬才出現一次。時間上是一天,一個月,甚至是一年很多年。但是干擾出現所造成的嚴重后果,是我們無法想象到的。

在這里我先引用一個小插曲:

“原來我在鎮江做焊機的時候,老是出現焊機在上電瞬間有信號輸出,出現的頻率很高,最嚴重的一次是差點將一個客戶員工的手指壓到。后來我想了個方法就是是在信號輸出的I/O口上加上一個50k的上拉電阻,發現問題還是有,但是出現的頻率降下來了,后來又改用15k的電阻,就徹底地把那個問題給解決了。”

干擾信號源也遵循歐姆定律,越存在干擾的場合,跟測試使用的上拉電阻也有聯系。想知道他是怎么解決的,可以看下下面的文章:

[話題] 【MCU每周論點】如何提高單片機的抗干擾能力? 親 你懂嗎?

二. 干擾源產生的原因是什么?

下面回到正題,

??????? 單片機干擾的原因還包括傳播途徑、敏感器件的使用,也會使單片機受到干擾。

干擾對單片機系統的影響主要通過三種途徑傳輸,包括:

(1)輸入系統。一般情況下,開關電源模塊星載儀器的檢測對象往往是微弱物理信號,通過放大的運放電路和高精度A/D轉換電路組成。如串入干擾,會使輸入的模擬信號失真,數字信號出錯,從而導致采集的數據誤差增大。

(2)輸出系統。一旦受到干擾,將使各輸出信號混亂,不能正常反應單片機系統的真實輸出。但一般單片機輸出電路都具有較高的電平,不易受到干擾,需要注意的是其對其他電路的干擾影響。

(3)CPU系統。該干擾主要是由CPU內部時鐘和噪聲引起的,它可使單片機系統總線上的數字信號錯亂,CPU得到錯誤的地址信號,使程序跑飛或死循環,導致輸出錯誤,并將這個錯誤一直傳遞,造成系統失敗。

敏感器件

在星載儀器單片機系統中,通常會用到一些如A/D、D/A變換器、弱信號放大器等容易被干擾的器件,也是產生干擾的重要原因。

三. 單片機抗干擾技術與措施

單片機系統電路復雜,產生干擾原因也很多,那我們平時應該如何去預防單片機干擾,提高單片機性能與抗干擾影響呢。下面有幾種常用的抗干擾措施:

1、切斷干擾的傳播途徑

1)增加干擾源(如電機、繼電器)與敏感器件(如單片機)的距離,用地線把他們隔離或者在敏感器件加上屏蔽罩。

2)電路板合理分區,將強信號、弱信號、數字信號、模擬信號電路合理地分區域布置。

4)、單片機和大功率器件的地線要單獨接地,以減小互相干擾。大功率器件要盡可能布置在電路板的邊緣。

5)、在單片機I/O口,電路板連接線等關鍵地方,使用抗干擾元件可顯著提高電路的抗干擾性能。

6)、晶振與單片機引腳盡量靠近,用地線把時鐘區隔離起來,晶振外殼接地并固定。

2、盡量采用抗干擾性能強的單片機

1)、降低單片機內部的電源噪聲

在傳統的數字集成電路設計中,通常將電源端和地端分別布置在對稱的兩邊。例如左下角為地,左上角為電源。這使得電源噪聲穿過整個硅片。改進方法將單片機的電源和地安排在兩個相鄰的引腳上,這樣不僅降低了穿過整個硅片的電流,還便于印制板上設計電源退耦電容,以降低系統噪聲。

2)、降低時鐘頻率

單片機測控系統的時鐘電路是一個調頻噪聲源,它不僅能干擾本系統,還對外界產生干擾,使其他系統的電磁兼容檢測不能達標。在保證系統可靠性的前提下,選用時鐘頻率低的單片機可降低系統的噪聲。以8051單片機為例,當最短指令周其為1US時,時鐘是12MHZ。而同樣速度的MOTOROLA兼容單片機的廠商在不犧牲運算速度的前提下,將時鐘頻率降低到原來的1/3。特別是MOTOROLA公司新推出的68HC08系列單片機、內部采用了鎖相倍頻技術,將外部時鐘除至32KHZ,而內部總線速度卻提高到8MHZ,甚至更高。

3)、EFT技術

隨著超大規模集成電路的發展,單片機內部的抗干擾技術也在不斷進步。MOTOROLA公司新推出的68HC08系列單片機,采用EFT技術進一步提高了單片機的抗干擾能力,當振蕩電路的正弦波信號受到外界干擾時,其波形上會疊加一些毛刺。若以施密特電路對其整形時,這種毛刺會成為觸發信號干擾正常的時鐘信號。但是交替使用施密電路和RC濾波可以使這類毛刺不起作用,這就是EFT技術。

3、單片機測控系統中的頻率抖動技術

將頻率拉動信號疊加到輸入信號的隨機噪聲上,雖然會增加轉換的總噪聲,但增加的噪聲是用來補償輸出數碼量化噪聲的,可使量化誤差不再輸入信號的函數而是抖動噪聲瞬時值的函數。因此,利用頻率顫抖信號可去除量化噪聲與輸入信號之間的相關性。頻率拉動信號的大小通常約為1/3LSB有效值。例如,在未加頻率拉動的情況下,ADC輸出的量化噪聲是瞬時輸入信號幅度的函數,量化拉動之后,因抖動信號的幅度不依賴于輸入信號,故量化噪聲與輸入信號無關,從而消除了ADC輸出諧波分量,但這是以增加總噪聲為代價的。需要指出的是,并不一定在ADC輸入端實際施加顫抖噪聲,也可利用地轉換器的熱噪聲作為頻率抖動信號,但ADC要有足夠的輸出位數以確保能夠去除輸入信號與量化噪聲的相關性。

4、防止漏電流的技術

應當在清潔、干燥、通風、環境溫度適宜的條件下使用智能化單片機測控系統。系統受潮后導致絕緣電阻下降,會產生漏電流。輕測使測量誤差增大,控制不靈;重則會造成適中故障,損壞元器件。例如,當印制板受潮時,A/D轉換器輸入阻抗下降,讀數不準,并且伴有跳數現象。這也是一些數字電壓表在雷雨季節無法正常工作的主要原因。對于受潮的印制板,可用無水酒精擦凈表面,然后用電吹風烘干,以消除漏電。

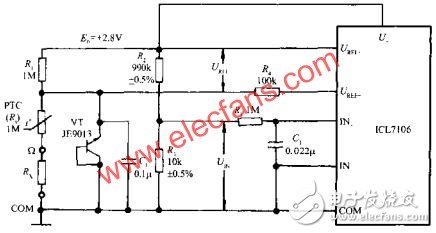

有些精密集成電路,專門設置了防止極間漏電用的保護環。例如由美國哈里斯公司生產的ICL7650型斬波自穩零式精密運算放大器,HI7195A型帶微處理器的5 1/2位A/D轉換器,均設置了兩個保護環引出端。設計電路時將兩個保護環接地,即可消除印制板上輕微漏電對測量所造成的影響。

5、濾波技術

濾波是指從混有干擾或噪聲的信號中獲取有用信號的方法,能實現上述功能的部件叫濾波器。在數字儀表中常見的濾波器主要有三種:無源濾波器,有源濾波器,數字濾波器。

1)無源濾波器

無源濾波器是由R、L、C元件構成的,根據干擾信號的特點,可選低通濾波器、高通濾波器和帶通濾波器。此外還有帶阻濾波器等類型。對于50HZ電磁場干擾,可在測控系統輸入端加一級雙T濾波器。

2)有源濾波器

有源濾波器是包含有源器件(例如晶體管、運算放大器)的各種濾波器。與單純使用R、L、C元件的無源濾波器相比,能省去體積龐大的電感元件,便于實現小型化、集成化。有源濾波器適用于較低頻率的濾波。二階有源帶通濾波器的典型電路參見下圖。

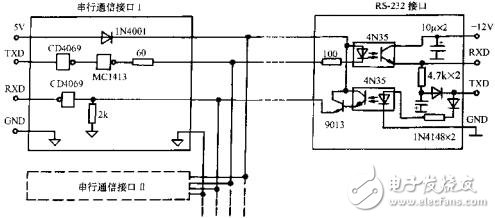

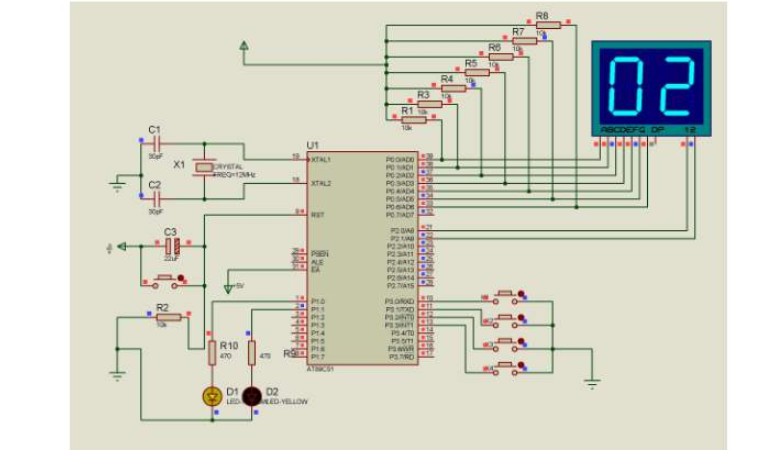

6、隔離技術

所謂隔離技術,是指將噪聲源與信號線相互隔離開的技術。在單片機系列中經常采用光耦合器來實現傳感器與輸入通道的隔離、I/O接口的隔離及內部電路的隔離。此外,在遠距離傳輸信號時,也需要采用光電隔離技術。一種采用光電隔離技術的網絡通信接口電路如下圖所示。在對被傳輸的模擬信號進行隔離時,宜選用線性光耦合器,其電流傳輸比接近于常數。

此外,在測試系統中還經常用變壓器隔離,繼電器隔離,貝母隔離等技術。

7、抵制傳輸線上的干擾

傳輸線宜選用雙絞線或同軸電纜屏蔽線,盡管雙絞線的頻帶較窄,但其波阻抗高,抗共模干擾能力強,雙絞線上的每個小環路的電磁感應用干擾能相互抵消,并且其分布電容較大,可起到積分電容的效果,因此對電磁場具有一定的抵制作用。使用長傳輸線時需要注意阻抗匹配問題。否則傳輸線上會產生反射波,造成信號失真。

8、正確選擇接地點

在單片機測控系統內部,大致有6種地線:信號線、模擬地、數字地、功率地、交流地和屏蔽地。

設計整機電路時應根據技術條件和實際情況來決定究竟是浮地還是接地,需要采用哪種地線,選擇單點接地還是多點接地。

9、傳感器的屏蔽

在工業現場使用集成溫度傳感器時,很容易引入干擾。為提高信噪比,可以給傳感器加上屏蔽。有些溫度傳感器,采用TO-52型金屬殼封裝,并且專有一個管腳接管殼。使用時將此腳接地,即可由管殼起來屏蔽作用。對于塑料封裝的集成溫度傳感器,必要時可用薄銅管做外屏蔽,把傳感器裝入后再用環氧樹脂封固,二者保持絕緣。這種全密封式傳感器特別適合測量液體和蒸氣的溫度。

10、塑料機的屏蔽

目前,采用ABS工程逆料制成的塑料機箱以其造型美觀,攜帶輕便等優點,深受人們的青睞。為使機箱具有屏蔽作用,可用噴涂、真空、沉積等方法在機箱內表面覆蓋一層導電膜。也可以自己加工屏蔽層,在機箱內表面粘粘一層鋁箔,再與公共地連通。

11、元器件的選擇

為降低元器件的噪聲,應盡量采用金屬膜電阻和低噪聲的有源器件。為了減小溫度漂移,全部元件需經過高、低溫老化處理。必要時,前級放大器、有源濾波器要加溫度補償電路。A/D轉換器的積分電容應選漏電小、介質損耗因數低的聚丙烯或聚苯乙烯電容。ICL7650型精密運放和IC7660型DC/DC轉換器泵電容,均應采用鉭電容。

能用低速器件就不用高速器件,高速器件只用在關鍵的地方。

12、消噪電路

帶隙基準電壓源是一種作為電壓基準的高穩定度電壓源,目前正廣泛用于數字儀表、智能儀器及測試系統中。在基準電壓輸出端并聯一只0.1UF的消噪電容,能濾除高頻噪聲。

當電路的輸出狀態維持不變時允許加到輸入端的噪聲電壓最大值,稱為電壓噪聲容限。噪聲容限愈高,說明器件的抗干擾能力,應盡量CMOS電路來代替TTL電路。CMOS電路的噪聲容限可達電源電壓的40%,而TTL電路大約只有電源電壓的16%。

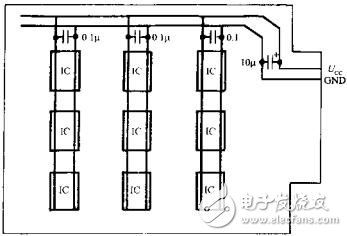

13、電源即耦電容

單片機測控系統中許多電路都是公用一個直流電源的。這就要求電源線不得在各電路之間引入干擾,并且當負載發生變化時直流電源線上不應產生波動。但實際上很難做到,因為直流電源的內阻抗,并且當負載發生變化時直流電源線上不應產生波動。但實際上很難做到,因為直流電源的內阻抗和電源引線的交流阻抗不可能為零。利用退耦電容不僅能降低直流電源的內阻抗,還能避免各電路之間通過電源線相互干擾。

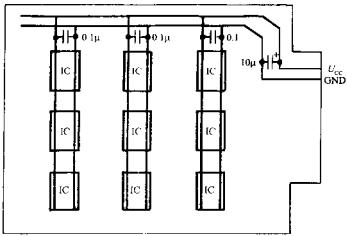

在單片機測控系統中使用了大量的數字IC,而每片數字IC本身都是一個脈沖干擾源,它們也會通過電源線相互干擾。解決辦法是在印制板電源進線端并聯一只10UF~100UF鉭電容進行電源退耦,同時在每個芯片的電源進線端再并聯一只高頻、低分布的電感的陶瓷電容,容量一般取0.1UF,當頻率超過 15MHZ時,可取0.01JF,電路如圖所示。退耦電容的引腳要盡量短。

電子發燒友App

電子發燒友App

評論