在RS232 中本來 CTS 與 RTS 有明確的意義,但自從賀氏(HAYES ) 推出了聰明貓(SmartModem)后就有點混淆了,不過現在這種意義為主流意義的,各大芯片制造廠家對 UART

2021-05-17 11:35:41 7384

7384

時序分析是FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-10-21 09:28:58 1283

1283 ,我只需要把芯片的RX和TX連接到PSoC,對嗎?在UART PSoC上沒有CTS和RTS可用嗎?謝謝你

2019-10-29 09:52:04

ClockTree Synthesis,時鐘樹綜合,簡稱CTS。時鐘樹綜合就是建立一個時鐘網絡,使時鐘信號能夠傳遞到各個時序器件。CTS是布局之后相當重要的一個步驟,在現如今集成了上億個晶體管

2019-01-18 17:35:57

我對從 ESP32-S2-WROOM 到我的主機設備的 UART 接線非常困惑。主機設備需要 RX、TX、RTS 和 CTS。由于我使用 UART0 進行編程,因此我想使用 UART1 在我的主機

2023-03-01 06:33:14

: uart7_sleep_mx-0 { pins {pinmux = , /* UART7_RX */, /* UART7_TX */, /* UART7_RTS */; /* UART7_CTS

2022-12-28 08:53:58

邏輯電路分為組合邏輯電路和時序邏輯電路。第四章已經學習了組合邏輯電路的分析與設計的方法,這一章我們來學習時序電路的分析與設計的方法。在學習時序邏輯電路時應注意的重點是常用時序部件的分析與設計這一

2018-08-23 10:28:59

這種時序圖第一次見,不會分析。1.希望技術支持或者哪位大神從編程的角度分析一下這個時序。2.上面的線為什么是曲線,代表什么意思?3.CLK正負的產生源可否是由DSP的引腳產生,經反相器,通過電容,形成兩路互補的信號?附件圖像 1.png35.7 KB

2018-12-03 09:15:27

請告訴我有關 CY7C65223-24LTXI 的引腳處理的信息。

不使用流量控制功能時,RTS 和 CTS 引腳是否應處于打開狀態?

2024-03-07 07:54:55

FPGA時序分析系統時序基礎理論對于系統設計工程師來說,時序問題在設計中是至關重要的,尤其是隨著時鐘頻率的提高,留給數據傳輸的有效讀寫窗口越來越小,要想在很短的時間限制里,讓數據信號從驅動端完整

2012-08-11 17:55:55

影響FPGA本身的性能,而且也會給FPGA之外的電路或者系統帶來諸多的問題。(特權同學,版權所有)言歸正傳,之所以引進靜態時序分析的理論也正是基于上述的一些思考。它可以簡單的定義為:設計者提出一些特定的時序

2015-07-09 21:54:41

首先是背景。我正在做一個USB到串行轉換器,相當于一個老學校RS232模擬調制解調器。(后端是唯一的,但是前端使用RS232端口(TX、RX、RTS、DTR、CTS、DSR、RI和DCD)中正常的8

2018-12-11 15:01:43

配置為我的項目輸出系統時鐘的DCM。自定義此IP后,我有以下問題:Spartan-3 DCM需要哪些約束(用于時序分析),它們是否會自動放置在我的項目中的某個位置?

2019-08-02 09:54:40

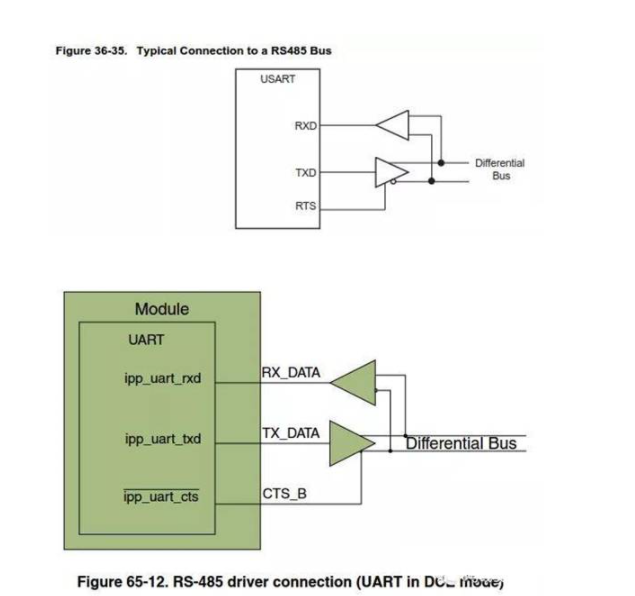

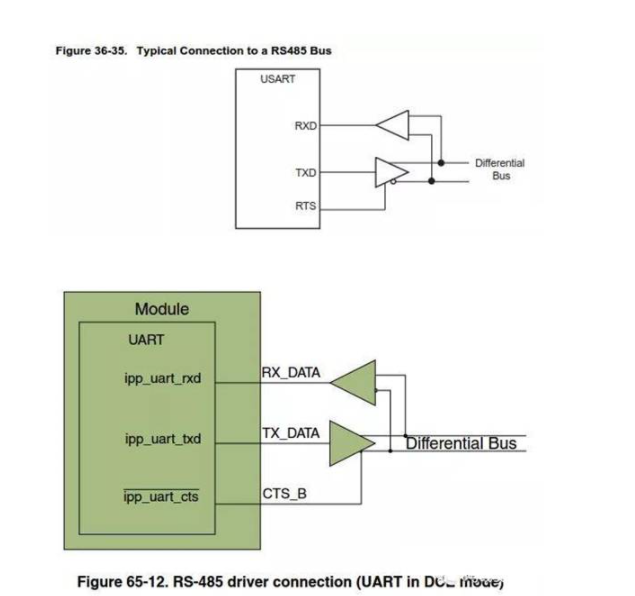

UART中的硬件流控RTS與CTS最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從賀

2021-08-11 09:06:46

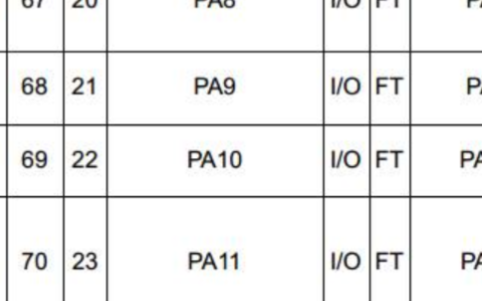

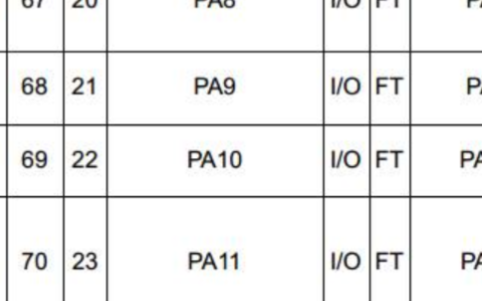

用的是STM32F407,如果我配置的時候不用USART2的硬件流控,那PA1這個腳能用作ADC1_IN1的功能么,USART2_RTS和ADC1_IN1都在PA1上。USART已啟用情況下,如何將RTS和CTS引腳當做通用IO使用?

2018-12-10 17:38:47

以下是USB底層信號的一些定義及時序圖,雖然很簡潔,但能理解后,對后續的USB學習是很有幫助的,特推薦給大家!BTW,本月(4月20號周六)在深圳有一場很接地氣、很容易入門的USB線下、小型技術交流

2019-04-08 16:30:26

自己做了一個工程,靜態時序分析的結果CLK信號的SLACK是負值(-7.399ns),書上說該值是負值時說明時序不對,但是我感覺時序仿真的結果是對的。是不是時序仿真波形正確就不用管靜態時序分析的結果了?請高手指點

2010-03-03 23:22:24

小弟接觸串口通訊不深,試過max232串口電路三線制可以成功傳輸數據;現在想使用max3232進行通訊,參考電路如下: RS232端有四根信號線,TX\RX\RTS\CTS,在max232電路中三

2012-11-15 17:51:39

跟大家分享一下 u***轉串口 9針 引腳定義:1 DCD載波檢測2 RXD 接收數據3 TXD 發送數據4 DTR 數據終端準備好5 SGND 信號地線6 DSR 數據準備好7 RTS 請求發送8 CTS 清除發送9 RI振鈴提示可以通過短接2、3 判斷電腦串口是否正常,如圖:

2016-03-27 14:06:18

芯片管腳有兩組UART,一組UART_TX,UART_RX。一組 UART_CTS,UART_RTS,這有什么區別?都是作為I/O口,有其他用途? 請說說看法,以及言外...

2019-01-23 11:23:48

:一類用于片內各功能部件的控制,它們是芯片設計師關注的問題,對用戶沒有什么意義。另一類用于片外存儲器或I/O端口的控制,需要通過器件的控制引腳送到片外,這部分時序對分析硬件電路的原理至關重要,也是軟件

2018-07-21 16:38:31

定義:我從文檔中推測,MAX3160Cap TTL端管腳定義MAX3160 TTL 管腳定義TXD:8RXD:16RTS:7CTS:152,MAX3160 RS232管腳定義:

2020-02-14 11:25:57

Ds1302Read(uchar addr);void Ds1302Init();void Ds1302ReadTime();這幾個函數,是根據時鐘芯片時序圖定義的還是你自己想象出來而定義的?如果是根據時序圖定義那時序圖又要怎么看呢,哪些該寫哪些不該寫?

2016-06-10 10:39:48

你好

我正在使用 CYBT-343026 (CYW20706) 上的 PUART 向具有 CTS/RTS 流量控制的主機 MCU 發送/接收數據。 主機 MCU 有時會通過長時間拉高 CYBT

2024-03-01 11:31:04

哪里有講stm32的USARTx_RTS和USARTx_CTS硬件流控制的,看了很多例子都是不用硬件流控制的

2017-03-24 13:44:29

可以通過程序框圖中的VISA屬性節點(Property Node)中的Modem Line Settings里的屬性來讀、寫串口中的DTR和RTS等控制線。LabVIEW 6.x, 7.x請根據

2019-07-01 14:13:15

挑戰。本文主要介紹了邏輯設計中值得注意的重要時序問題,以及如何克服這些問題。最后介紹了利用Astro工具進行時序分析的方法。關鍵詞:ASIC;同步數字電路;時序;Astro引言 隨著系統時鐘頻率的提高

2012-11-09 19:04:35

只能分析一些簡單的時序圖,稍微復雜點的就感覺力不從心啊,求講解

2023-11-10 07:43:21

時間稱為時鐘抖動,如圖 2所示。一般情況下的時序分析是不考慮時鐘抖動,如果考慮時鐘抖動,則建立時間應該是Tsu+T1,保持時間應該是Th+T2。 2.時鐘偏斜時序偏斜分析圖如圖 3所示。時鐘的分析起點是源

2018-04-03 11:19:08

以時鐘芯片DS1302為例子來分析時序圖并寫出代碼

2021-04-02 06:00:39

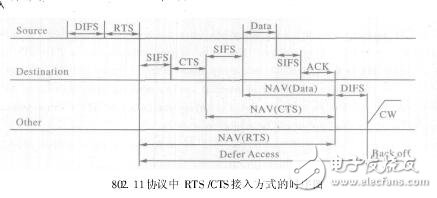

://forums.xilinx.com/t5/PicoBlaze/PicoBlaze-FAQ-Can-the-UART-support-CTS-RTS/td-p/636但我不明白如何實現流量控制的CTS和RTS信號。這些信號是否必要

2019-08-23 09:38:03

如何看時序圖,如何用時序圖?求一些詳細的資料。

2013-01-21 12:29:00

電腦上軟件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代碼里的流控配置做配合,還是不太理解。我現在板子上的CTS和RTS用跳線帽連上了,然后我PC端上的流控開和關都能收到

2015-11-12 10:14:14

問個問題,拿過來一個芯片datasheet,怎么由它的時序圖把程序寫出來? 我看過一些芯片的時序圖,懂是可以懂得,但再看程序,里面定義了很多函數,向I2C總線結構的程序,還有開啟和關閉I2C,類似這種。。。能否只從時序圖直接寫出它的程序? 路過的朋友可以探討下并留下你的寶貴建議,謝謝。

2013-12-17 10:10:57

IOMUXC_GPIO_AD_B0_09 引腳需要設置引腳,并且可以通過使用“fsl_iomuxc.h”中的“IOMUXC_GPIO_AD_B0_09_LPUART1_RTS_B”定義來實現。在這種情況下,我可以

2023-05-05 09:52:21

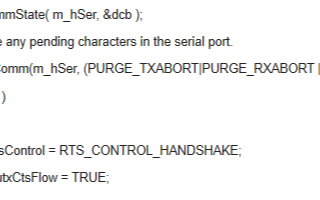

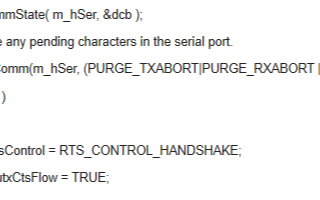

大家好,求助一個問題,有償,會給你沖手機話費,問題如下:我在使用FT232時,上位機又是會連續發一些指令,這時下位機不能接收上位機的信息時就會對CTS置1,但是上位機檢測CTS的代碼如下,但是好像

2016-10-27 08:06:17

請教如何做時序分析

2013-06-01 22:45:04

連接MCU 的UART,但僅使用 TX,RX,請問RTS,DSR,CTS,RI,DTR,DCD,ACT等管腳應該如何處理(懸空?上下拉?)以及電源管腳的連接,是否有個不帶流控的典型應用電路圖

2022-07-05 06:46:13

哪位朋友用過ST的UARTS CTS/RTS,STM32F4 discovery USART CTS/RTS怎么設置?有官方提供的例子嗎?

2018-09-04 09:38:09

想做個板子, 想把串口模塊的線都接出來, 以供學習用(不管功能和作用怎么樣), 其中RTS和CTS都能在9針串口定義中找到定義, 但沒找到UART_CK, 問下這根線應該接在9針串口的哪個位置??再

2020-03-11 02:27:06

在庫函數里的操作就是開啟CTS RTS 或者是NONE可是真的體驗和操作是怎么樣才可以感覺得到的呢?

2018-10-15 08:54:23

請問串口的SR寄存器里的狀態位為什么只有CTS判斷的,沒有RTS,在CR寄存器里也沒有位是對RTS進行操作的,難道是要直接對GPIO置1和0進行操作嗎?

2019-02-26 08:00:36

請問串口的SR寄存器里的狀態位為什么只有CTS判斷的,沒有RTS,在CR寄存器里也沒有位是對RTS進行操作的,難道是要直接對GPIO置1和0進行操作嗎?

2015-11-15 14:45:37

電腦上軟件的硬流控怎么配合板子上的CTS,RTS,以及板子上的CTS,RTS 和代碼里的流控配置做配合,還是不太理解。我現在板子上的CTS和RTS用跳線帽連上了,然后我PC端上的流控開和關都能收到

2019-02-25 06:04:43

藍牙模塊的TX、RX、RTS、CTS和51單片機應該怎么連接嘞????求高人指導啊

2019-01-21 06:35:44

的周期。Duty cycle:高電平持續時間(正相位)和低電平持續時間(負相位)。Edge times: 上升沿和下降沿的時間。時鐘約束通過定義時鐘, 所有內部時序路徑 ( 觸發器到觸發器路徑 )都將

2023-04-20 16:17:54

Cadence高速PCB的時序分析:列位看觀,在上一次的連載中,我們介紹了什么是時序電路,時序分析的兩種分類(同步和異步),并講述了一些關于SDRAM 的基本概念。這一次的連載中,

2009-07-01 17:23:27 0

0 Cadence 高速 PCB 的時序分析 1.引言 時序分析,也許是 SI 分析中難度最大的一部分。我懷著滿腔的期許給 Cadence 的資深工程師發了一封 e-mail,希望能夠得到一份時序分析的案

2010-04-05 06:37:13 0

0 時序約束與時序分析 ppt教程

本章概要:時序約束與時序分析基礎常用時序概念QuartusII中的時序分析報告

設置時序約束全局時序約束個別時

2010-05-17 16:08:02 0

0 特性

Programmable Auto-RTS and Auto-CTS

In Auto-CTS Mode, CTS Controls Transmitter

2010-09-09 22:18:03 7

7 !!好貨 CTS60 CTS60 CTS 60 CTS-60 數字無線測試儀 譚艷飛13543805887歐陽’S現貨中山市華儀通電子儀器有限公司聯系人:譚艷飛(經理)手機:13543805887 電話: 0760-226808

2008-08-19 10:37:53 601

601 %$!二手 CTS65 CTS 65 CMD55 CTS60 綜合測試儀 譚艷飛13543805887歐陽S

中山市華儀通電子儀器有限公司

聯系人:譚艷飛(經理)歐陽婧(特助)

手機

2008-09-09 23:10:37 567

567 !!瘋狂/甩賣 CTS60 CTS60 CTS60 數字無線測試儀 譚艷飛/李13543805887

2008-10-14 09:06:08 610

610 %$!二手 CTS65 CTS 65 CMD55 CTS60 綜合測試儀譚艷飛13543805887歐陽S中山市華儀通電子儀器有限公司聯系人:譚艷飛(經理)歐陽婧(特助)

2008-10-14 11:02:21 535

535 !!供應CTS55 CTS55數字無線綜測儀CTS55 小兵/李小姐

東莞市銀通電子儀器有限公司聯系人:歐陽小兵/李小姐手機:13332662998/13790420385電話:0769-87912629傳真:0769-87912842MAIL

2008-11-17 15:19:50 393

393 !銷售/回收CTS60 CTS60數字無線測試儀CTS60.小兵/李S

東莞市銀通電子儀器有限公司聯系人:歐陽小兵/李小姐手機:13332662998/13790420385電話:0769-87912629傳真:0769-87912842MAI

2009-01-17 16:05:35 534

534 跳變點是所有重要時序分析工具中的一個重要概念。跳變點被時序分析工具用來計算設計節點上的時延與過渡值。跳變點的有些不同含義可能會被時序分析工程師忽略。而這

2010-09-15 10:48:06 1461

1461

定義了時鐘單位階躍信號C(n) 提出了一種利用帶相對時鐘坐標的邏輯方程表示邏輯信號的方法通過對所設計的DDR SDRAM控制器的讀寫時序的分析建立了控制器主要信號的時序表達式并利用

2011-09-26 15:34:12 39

39 討論了靜態時序分析算法及其在IC 設計中的應用。首先,文章討論了靜態時序分析中的偽路徑問題以及路徑敏化算法,分析了影響邏輯門和互連線延時的因素。最后通過一個完整的IC 設計

2011-12-20 11:03:16 95

95 _靜態時序分析(Static_Timing_Analysis)基礎及應用[1]。

2016-05-09 10:59:26 31

31 基于時序路徑的FPGA時序分析技術研究_周珊

2017-01-03 17:41:58 2

2 靜態時序分析基礎及應用

2017-01-24 16:54:24 7

7 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2017-02-11 19:08:29 3938

3938

!大量收購/回收CTS60綜合測試儀CTS60 孫峰/何S:13549469921 東莞市宏達電子儀器有限公司 聯系人:孫峰/何S(銷售工程師):13549469921 客 服QQ

2018-03-27 05:11:01 1107

1107 STA的簡單定義如下:套用特定的時序模型(Timing Model),針對特定電路分析其是否違反設計者給定的時序限制(Timing Constraint)。以分析的方式區分,可分為Path-Based及Block-Based兩種。

2018-04-03 15:56:16 10

10 本文檔的主要內容詳細介紹的是UART中的硬件流控RTS與CTS的知識點詳細資料說明。最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。

2019-05-31 17:53:00 10

10 中低端路由器上使用disp interface 查看相應串口狀態信息,其中DCD、DTR、DSR、RTS及CTS等五個狀態指示分別代表什么意思? DCD ( Data Carrier Detect

2019-04-25 18:28:00 7

7 最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從賀氏(HAYES ) 推出了聰明

2019-04-24 18:29:00 3

3 靜態時序分析是一種驗證方法,其基本前提是同步邏輯設計(異步邏輯設計需要制定時鐘相對關系和最大路徑延時等,這個后面會說)。靜態時序分析僅關注時序間的相對關系,而不是評估邏輯功能(這是仿真和邏輯分析

2019-11-22 07:07:00 3179

3179 時序分析是以分析時間序列的發展過程、方向和趨勢,預測將來時域可能達到的目標的方法。此方法運用概率統計中時間序列分析原理和技術,利用時序系統的數據相關性,建立相應的數學模型,描述系統的時序狀態,以預測未來。

2019-11-15 07:02:00 2570

2570

ESM335x系列工控主板支持5路高速串口,其中COM2口支持硬件RTS/CTS流控功能,其RTS/CTS分別與ESM335x的GPIO1/GPIO0復用,應用程序可以獨立設置是否使能RTS/CTS

2020-02-04 11:22:47 1273

1273

STM32的USART中RTS、CTS的作用和意義

2020-03-20 11:11:35 7101

7101

靜態時序分析是檢查芯片時序特性的一種方法,可以用來檢查信號在芯片中的傳播是否符合時序約束的要求。相比于動態時序分析,靜態時序分析不需要測試矢量,而是直接對芯片的時序進行約束,然后通過時序分析工具給出

2020-11-11 08:00:00 58

58 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2021-01-08 16:57:55 28

28 本文檔的主要內容詳細介紹的是時序分析的靜態分析基礎教程。

2021-01-14 16:04:00 14

14 CTS7-100與CTS7-200的主要區別說明。

2021-05-09 10:21:49 5

5 方法,能夠有效減少時序路徑問題分析所需工作量。 時序路徑問題分析定義為通過調查一條或多條具有負裕量的時序路徑來判斷達成時序收斂的方法。當設計無法達成時序收斂時,作為分析步驟的第一步,不應對個別時序路徑進行詳細時序分

2021-05-19 11:25:47 2677

2677

UART中的硬件流控RTS與CTS最近太忙了,沒時間寫對Ucos-II的移植,先將工作中容易搞錯的一個知識點記錄下來,關于CTS與RTS的。在RS232中本來CTS 與RTS 有明確的意義,但自從

2021-12-09 12:21:11 16

16 時序分析時FPGA設計中永恒的話題,也是FPGA開發人員設計進階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2095

2095

電子發燒友App

電子發燒友App

評論