1 引言

射頻識別(RFID)技術作為一種新興的自動識別技術,近年來在國內外得到了迅速發展。目前,我國開發的RFID產品普遍基于中低頻,如二代身份證、票證管理等。在超高頻段我國自主開發的產品較少,難以適應巨大的市場需求以及激烈的國際競爭。超高頻(UHF)標簽是指工作頻率在860~960 MHz的RFID標簽,具有可讀寫距離長、閱讀速度快、作用范圍廣等優點,可廣泛應用于物流管理、倉儲、門禁等領域。為適應市場需求,本文以EPC C1G2協議為主,ISO/IEC18000.6為輔,設計了一種應用于超高頻標簽的數字電路。

2 UHF RFID標簽的工作原理

射頻識別系統通常由讀寫器(Reader)和射頻標簽(RFID Tag)構成。附著在待識別物體上的射頻標簽內存有約定格式的電子數據,作為待識別物品的標識性信息。讀寫器可無接觸地讀出標簽中所存的電子數據或者將信息寫入標簽,從而實現對各類物體的自動識別和管理。讀寫器與射頻標簽按照約定的通信協議采用先進的射頻技術互相通信,其基本通訊過程如下。

(1)讀寫器作用范圍內的標簽接收讀寫器發送的載波能量,上電復位;

(2)標簽接收讀寫器發送的命令并進行操作;

(3)讀寫器發出選擇和盤存命令對標簽進行識別,選定單個標簽進行通訊,其余標簽暫時處于休眠狀態;

(4)被識別的標簽執行讀寫器發送的訪問命令,并通過反向散射調制方式向讀寫器發送數據信息,進入睡眠狀態,此后不再對讀寫器應答;

(5)讀寫器對余下標簽繼續搜索,重復(3)

(4)分別喚醒單個標簽進行讀取,直至識別出所有標簽。

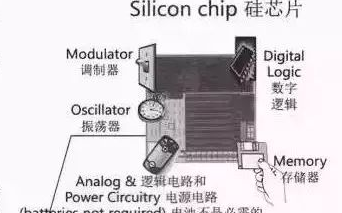

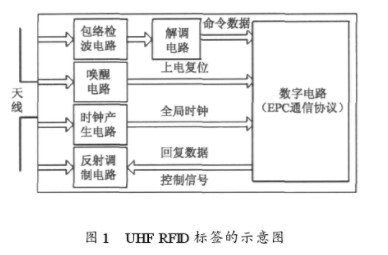

3 UHF RFID標簽的結構及系統規格

UHF RFID標簽的示意圖如圖1所示,由模擬和數字兩部分組成。模擬電路主要包括天線、喚醒電路、時鐘產生電路、包絡檢波電路、解調電路和反射調制電路;數字部分主要實現EPC通信協議,識別讀寫器發出的命令并執行,如實現多標簽閱讀時的防沖突方法、執行讀寫器發送的讀寫命令、實現讀寫器和標簽的通訊過程以及對輸出數據進行編碼等。協議規定的標簽系統規格如表1所示。

4.標簽數字電路的設計方法

4.1 電路的整體系統設計

經過對協議內容的深入研究,本文采用Top.down的設計方法,首先對電路功能進行詳細描述,按照功能對整個系統進行模塊劃分;再用VHDL硬件描述語言進行RTL代碼設計并進行功能仿真;功能驗證正確后,采用EDA工具,指定工藝庫,進行邏輯綜合優化;最后采用自動布局布線進行版圖設計形成芯片。本文確定的系統結構框圖如圖2所示,它包括譯碼模塊、CRC (循環冗余校驗,cyclic redundancy check)校驗模塊、狀態機模塊、CRC產生模塊、存儲器、編碼模塊和時鐘分頻模塊。譯碼模塊接收模擬部分解調出的命令信號,根據協議中規定的命令格式將信號譯碼成標簽數字部分可識別的二進制數據,并發送到CRC校驗模塊和狀態機模塊。CRC校驗模塊對收到的命令進行完整性校驗,若確認為有效命令,則觸發狀態機模塊,控制標簽執行相應操作,如讀寫存儲器、防沖突控制等。處理完成后則將要發送的數據送至CRC產生模塊產生相應的CRC校驗碼,然后將要發送的數據和校驗碼一起送至編碼模塊,最后由編碼模塊以特定的脈沖形式發送給模擬部分進行處理后再采用射頻技術發送給讀寫器。為降低功耗,時鐘分頻模塊將全局時鐘進行分頻,分頻后的頻率可由數字部分其他模塊使用。存儲器存儲標簽的標識性信息。下面將具體介紹各模塊的實現方法。

4.2 譯碼模塊具體實現方法

讀寫器發出的命令采用PIE (pulse.interval encoding)格式,命令以同步頭(preamble)開始,如圖3所示。譯碼模塊的實現方法為:首先判斷同步頭,標簽對輸入信號進行檢測,一旦檢測到下降沿說明可能是一條新命令的定界符(delimiter),馬上計數低電平,將計數值存人寄存器count0中,同時檢測輸入信號是否有上升沿跳變,若發現上升沿跳變,則數據清零重新計數,并把delimiter之后的計數值存入寄存器count中,不斷比較寄存器count0和count的值,依據圖3所示的關系依次判斷出delimiter, 數據0,RTcal(reader to tag calibration),TRcal (tag to reader calibration), 確認同步頭;然后把同步頭之后的數據比RTcal/2短的作為數據0,比RTtcal/2長的作為數據1,從一系列高低電平中恢復出真正的1信號和0信號,依次存入命令寄存器,并提供控制狀態機及校驗模塊的相關標志位。

4.3 CRC校驗和產生模塊

UHF RFID系統采用循環冗余校驗(CRC校驗)來判斷數據的有效性和完整性,CRC校驗可以保護讀寫器發出的RjT (reader to tag)命令和標簽反向散射的TjR (tag to reader)序列。從數學角度來看,CRC校驗是用將被處理的數據字節當作一個二進制多項式A ( )的系數,該系數除以發送方和接收方預先約定好的生成多項式g ( )后,將求得的余數P ( )作為CRC校驗碼。CRC的計算包括了要計算其CRC值的數據字節以及所有前面的數據字節的CRC值。當一個數據塊被傳輸時,數據發送方計算此數據塊的CRC校驗碼,并將此校驗碼附在數據塊后一起傳輸。數據接收方計算所有接收數據的CRC值,其結果總是零,否則在傳輸過程中一定出現了傳輸錯誤。用零校驗可以很容易地分析數據的完整性,避免代價很高的校驗和比較過程。協議中采用線性反饋移位寄存器來實現CRC校驗,CRC.5校驗和CRC.16校驗的電路示意圖如圖4所示。

4.4 射頻標簽中的狀態機

RFID標簽所有的操作都基于由一系列邏輯控制的狀態轉換進行的,此為標簽數字電路的核心部分。本設計采用有限狀態機來實現此模塊,這里用到了3類基本操作和7種典型的狀態。如圖5所示,當收到不同命令時,標簽將會在7種狀態間進行轉換。選擇(select)命令和盤存(inventory)命令用于從標簽群中識別出特定的一個,標簽所處的相應狀態為ready,arbitrate,reply,acknowledged;一旦標簽被識別,讀寫器即可發出訪問(access)命令,讀取標簽的信息或將信息發送給標簽,標簽所處的相應狀態為open,secured,killed。

識別多個標簽時采用隨機分槽防碰撞算法(slotted random anti.collision algorithm)解決沖突問題。讀寫器向讀寫范圍內的每個標簽發送包含參數Q (取值0 15)的Query命令,控制標簽往各自的分槽計數器內載入一個由Q值決定的隨機數(取值范圍0~2Q.1),隨機數的產生主要基于線性移位反饋寄存器 。讀寫器再發出其他inventory命令改變隨機數的值,只有當隨機數的值為0時,標簽才會應答。若多個標簽的計數器值同時為0時,這些標簽同時應答,從而造成沖突。讀寫器檢測到沖突后,發出inventory命令讓沖突標簽的隨機數值從0000h(十六進制數)變到7FFFh,再通過設置新的Q參數來隨機散列分槽計數器值,使得發生沖突的多個標簽逐一被識別,保留一個處于活動狀態的標簽與讀寫器建立無碰撞通信,這樣就有效地解決了沖突問題。雖然此種方法的判別線性度(215_1)比二進制數搜索法(2蜥)低,但讀取速度高,演算機制完整,可防范多種信號碰撞的可能性,大幅降低信號碰撞的幾率。

4.5 編碼模塊

標簽反向散射給讀寫器的數據采用FM0編碼,圖6給出了FM0編碼的格式。

FM0編碼的數據前應以前同步碼開始,選擇哪種前同步碼由讀寫器所發命令中的TRext參數決定;FM0編碼在每個數據邊界處倒轉相位,并在數據0中間倒轉相位。FM0編碼具有記憶功能,一序列的信號中,后一位電平必須承接上一位末尾電平,所以需要一個寄存器存放上一位末尾處的電平信號,由此來判斷下一信號的起始電平。根據讀器所發命令確定標簽返回數據的鏈路頻率(LF:link frequency), 由內部時鐘計數產生所需頻率,以此作為標簽返回數據的發送頻率。為降低功耗,可以將全局時鐘分頻,降低時鐘頻率。為了準確實現編碼的功能,需要在充分理解標準的基礎上,嚴格定義該模塊與狀態機之間的接口時序。編碼模塊只有與狀態機模塊在時序上密切配合,雙方才能正確地發送和接收信號。實現過程為:當狀態機發送的使能信號有效時,編碼模塊進入編碼狀態,同時,狀態機送出數據信號;編碼模塊被觸發啟動后,首先按照協議要求產生前同步碼,再把要輸出的數據依次編碼,產生1 bit中高低各半的0信號或統一電平的1信號,串行送出;當狀態機發送最后一位數據的同時,通知編碼模塊,狀態機的數據已經發送完畢。

4.6 存儲器及存儲控制邏輯

RFID標簽的數據信息都存儲在存儲器中,一般采用EEPROM,用于存儲EPC代碼以及password等標簽的標識性信息。存儲器與狀態機的接口 5 J為:Di是存儲器輸入數據信號;Do是存儲器輸出數據信號;Addr是存儲器輸入地址信號;oen是存儲器輸出使能信號,高電平有效;cen是存儲器芯片使能信號,高電平有效;we是存儲器讀寫控制信號,we=1時寫有效;we=0時讀有效。

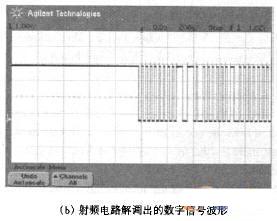

5 仿真結果及版圖

本文采用VHDL完成了UHF RFID標簽數字電路的RTL代碼設計,同時對標簽與讀寫器通訊過程進行全面的模擬和仿真,并基于0.18μm CMOS工藝標準單元庫,用EDA相關工具對該電路進行了前端綜合和后端物理實現。仿真結果如圖7所示,可以看到,綜合后的電路將讀寫器發出的PIE格式命令CMD data成功地譯碼為二進制數據,存人命令寄存器command中,并提供了控制狀態機及校驗模塊的相關命令的使能信號(Query en,QueryAdjust—en等);在各種命令使能信號的觸發下標簽執行相應操作,按讀寫器要求產生各種輸出數據(rn,handle等);并將輸出數據進行FM0編碼產生CMD out;還實現了與存儲器的接口。仿真結果顯示標簽數字電路在各情況下均正常工作,完全滿足協議要求。綜合后的電路規模約為11000門,功耗約為35μw。由于電路規模很大,要通過自動布局線進行版圖設計,所設計的版圖如圖8所示。版圖已經通過了DRC(設計規則檢查)和LVS(版圖與電路圖一致比較)驗證,時序分析也滿足要求,電路具有較大的裕量,可靠性較高。

本文依據EPC C1G2及ISO/IEC18000—6協議,利用VHDL硬件描述語言和EDA工具設計實現了UHF RFID標簽數字電路,可應用于工作在超高頻段的各種RFID標簽的數字部分。文中給出的仿真結果表明完成的設計符合協議要求。邏輯綜合也得到讓人滿意的結果,這些都保證了電路的高性能和后端設計的順利完成。后期的工作是對流片結果進行測試,另外,在滿足協議功能要求的基礎上,如何盡可能地簡化電路結構并盡可能降低功耗是進一步研究的課題。

電子發燒友App

電子發燒友App

評論