現(xiàn)有的電網(wǎng)質(zhì)量分析板受器件和分析方法的限制,大多對系統(tǒng)中的暫態(tài)、短時擾動信息難以快速、準(zhǔn)確地捕捉.隨著高速數(shù)字信號處理?DSP 技術(shù)的發(fā)展及其制造成本的降低,DSP技術(shù)在電力系統(tǒng)的各個研究領(lǐng)域得到了廣泛的應(yīng)用.表1是DSP方式與傳統(tǒng)芯片處理方式的能力對比,從中可以看出DSP用作處理器的優(yōu)勢.

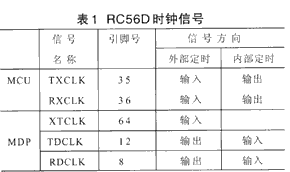

表1 DSP與傳統(tǒng)芯片處理能力對比表

| CPU系統(tǒng) | 采樣通道數(shù) | DFT計算時間 | 采樣時間/(μs) | 采樣結(jié)果精度(%) |

| TMS320F206晶振:10MHz | 40 | 整型30點28μs | 24 | 0.2 |

| 80C196晶振:12MHz | 16 | 整型12點1500μs | 160 | 0.5 |

| 80C51晶振:12MHz | 8 | 整型12點1500μs | 60 | 0.5 |

2 基于TMS320F206的硬件設(shè)計

基于DSP處理板的主體設(shè)計思想是采用DSP芯片TMS320F206構(gòu)成數(shù)字處理系統(tǒng),并以下位機為主體實現(xiàn)實時采樣、數(shù)據(jù)處理、分析和短時儲存,然后與上位機進行數(shù)據(jù)通訊,以及利用遠程計算機進行展示和數(shù)據(jù)庫存儲管理等.具體操作如下:

(1)用處理板測量并計算三相電流、電壓的有效值、有功功率、無功功率以及功率因數(shù);對40Hz~2MHz頻率輸入信號進行測頻采樣;

(2)對數(shù)據(jù)進行處理,分析查錯,給出報警類別,并給出開關(guān)量輸出信號以便進行開合閘操作;

(3)對電壓、電流的l~63次諧波進行分析,給出幅度、相位以及三相電壓、電流的總畸變率;

(4)通過16C552芯片UART擴展2個RS-232和一個RS-485接口以便與上位機進行數(shù)據(jù)交換,同時擴展一并行口以與打印機相連;

(5)用看門狗進行刷新、復(fù)位并實時檢測系統(tǒng);

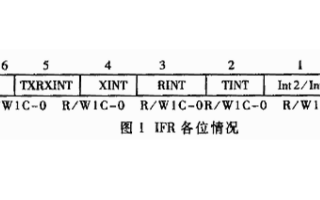

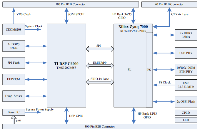

該處理板的主控芯片選用定點DSP芯片TMS320F206.系統(tǒng)的硬件功能框圖如圖1所示.

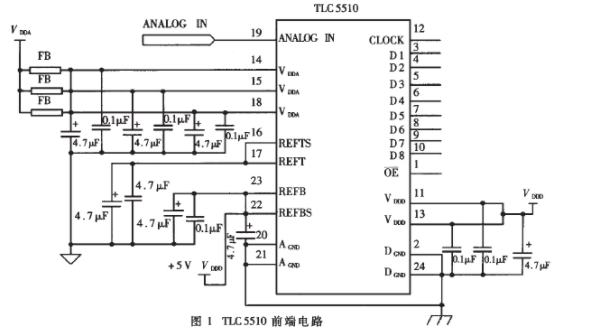

該電網(wǎng)采樣數(shù)據(jù)處理板的功能是在數(shù)字信號處理芯片TMS320F206的控制下完成的.數(shù)據(jù)采樣模塊采用的3片高速14位A/D芯片MAX125在工作時外接與16C552公用的16MHz時鐘,因其并行接口數(shù)據(jù)訪問和總線釋放的時間特性與DSP的特性兼容,因此,其轉(zhuǎn)換結(jié)果可由DSP不加等待狀態(tài)而直接讀取.3片MAX125在此用12路進行同步采樣?不用的通道為防干擾應(yīng)接地.電壓、電流等模擬量通過變壓器轉(zhuǎn)換成-5V~+5V的電壓,并在濾波后接入MAX125,轉(zhuǎn)換開始信號由DSP的引腳TOUT提供給3片MAX125的CONVST引腳,并在上升沿啟動采樣,片內(nèi)的時序發(fā)生器可控制指定的通道以使其按順序進行轉(zhuǎn)換,并將結(jié)果存儲在片內(nèi)14Bit×4的RAM中,轉(zhuǎn)換結(jié)束后,每片MAX125的INT引腳變低?3片通過CPLD或門輸出給DSP.讀取結(jié)果時,執(zhí)行連續(xù)讀操作,第一次讀到的是第一通道的數(shù)據(jù),第二次讀的是第二通道的數(shù)據(jù),依此類推.

16C552是TI?TLl6C552 、EXAR?ST16C552 、VLSI?VL16C552 等公司生產(chǎn)的異步通信芯片.在采樣處理板中?16C552可作為RS232、RS485串口和打印機并口的擴展芯片,并通過MAX232驅(qū)動芯片來和MAX1486驅(qū)動芯片與上位機進行通訊.圖2為UART擴展的電路圖.

由于TMS320F206僅有一個同步通訊口,因而設(shè)計中采用DSP的UART擴展.同時由于輸入輸出接口的資源有限,故采用了CPLD擴展.圖2中將DSP及電源、地、光電耦合器等做了簡化,有興趣的讀者可以查詢相關(guān)資料.本系統(tǒng)中16C552的串口和并口都工作在中斷工作方式,16C552的CLK端外接15.9744MHz晶振時,可通過設(shè)置除數(shù)寄存器的高、低位DLM、DLL來確定通訊的波特率.

在硬件電路設(shè)計中,l6C552的片內(nèi)寄存器選擇線A0~A2以及讀寫信號均由DSP直接控制.串、并行通道的片選線CSA、CSB和CSP則由CPLD直接控制,可根據(jù)需要選擇串行通信方式還是并行通信方式.為防止干擾,系統(tǒng)加入了光電隔離器,由于RS232電平與CMOS電平不同,因此RS232驅(qū)動器與CMOS電平連接時必須經(jīng)過電平轉(zhuǎn)換,MAX232就是完成這一功能的.另外,用MAXl486來實現(xiàn)與RS485的通訊,該驅(qū)動芯片的OE、H/F可決定電路是工作在半雙工還是全雙工狀態(tài),并可由CPLD來控制選擇.l6C552的并口可直接連接到PC機的并口上而無須電平轉(zhuǎn)換.通訊時,通過中斷INT1~INT3可向CPLD邏輯塊發(fā)生申請,并由DSP響應(yīng).

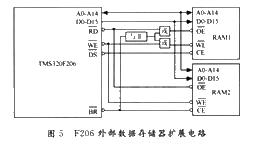

為了便于調(diào)試和實現(xiàn)程序加載、設(shè)置軟件斷點等功能,系統(tǒng)擴展了32k的快速SRAM來將程序、參數(shù)放入其中,調(diào)試成功后,可將待固化程序通過仿真器燒入TMS320F206的第一塊16k字的Flash中,第二塊用于固化放置重要參數(shù).為了調(diào)試方便和有效利用資源,程序、數(shù)據(jù)片選應(yīng)采用圖3所示的連接方式,調(diào)試時程序選用前16k(8000H~BFFFH)的SRAM,后16k(C000H~FFFFFH)用于存放數(shù)據(jù)參數(shù).

該系統(tǒng)能測量40Hz~2MH的信號頻率.測量工頻時,電網(wǎng)信號經(jīng)變壓器降壓后,再經(jīng)過濾波器和比較器送給CPLD進行計數(shù)測量.8MHz(CLK)晶振脈沖輸入可以使用單獨的有源晶振,也可以用CPLD對已有的16MHz晶振分頻得到.

選用完成系統(tǒng)電源監(jiān)控的看門狗復(fù)位芯片MAX1232,可設(shè)置為自動刷新和手動復(fù)位結(jié)合方式.當(dāng)電壓檢測器監(jiān)控到Vcc低于所選擇的容限時,系統(tǒng)將輸出并保持復(fù)位電平;以使DSP能在一定時間內(nèi)觸發(fā)ST端來刷新看門狗.如果ST在250ms間隔內(nèi)未觸發(fā),MAX1232自動發(fā)出信號來復(fù)位系統(tǒng).

3 基于TMS320F206的軟件流程

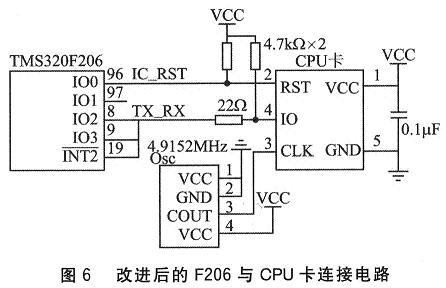

該數(shù)據(jù)采集處理板通過TMS320F206內(nèi)部定時器中斷來啟動A/D轉(zhuǎn)換,中斷周期被設(shè)置為每周波采樣64點,即約312.5ns觸發(fā)一次中斷.MAX125的12路A/D轉(zhuǎn)換完成后,電路將觸發(fā)中斷信號INT0給DSP.實時數(shù)據(jù)由DSP通過連續(xù)讀脈沖將數(shù)據(jù)存到內(nèi)、外部擴展RAM或通過通訊擴展芯片傳給上位機.當(dāng)數(shù)據(jù)采樣達到64個點后,開始執(zhí)行FFT單元.通常將FFT算法程序塊存到DSP內(nèi)部存儲單元B0中,該單元是一個64點同址基2 時間抽取的FFT模塊.通過DSP算法可實現(xiàn)對各項電能質(zhì)量指標(biāo)及其它電參數(shù)的計算與分析,同時進行數(shù)據(jù)處理(包括諧波分析和不平衡度分析),也就是在采樣點采樣后實時檢測信號的峰值、有效值等信息,以判斷過壓、欠壓、振蕩等電能質(zhì)量問題.最后將實時波形或分析譜結(jié)果傳送到PC上位機或其它網(wǎng)絡(luò)上.系統(tǒng)的每個采樣周期的時間分配見圖4 所示.其軟件主程序和中斷處理程序流程圖分別見圖5、圖6 所示.

我國對電網(wǎng)質(zhì)量研究起步較晚,目前使用的電網(wǎng)質(zhì)量檢測設(shè)備與發(fā)達國家還有一定距離,因此,電網(wǎng)污染問題仍然有待于進一步解決,傳統(tǒng)的采樣裝置有待于進一步優(yōu)化提高,本文設(shè)計的電力采樣處理板采用DSP芯片構(gòu)成數(shù)字處理系統(tǒng),以下位機為主體實現(xiàn)實時采樣、數(shù)據(jù)處理、分析和短時儲存,同時與上位機進行數(shù)據(jù)通訊并利用遠程計算機展示和存儲管理數(shù)據(jù)庫.實驗證明:利用該設(shè)備可提高系統(tǒng)的運算速度和精度?而且性價比很高.

電子發(fā)燒友App

電子發(fā)燒友App

評論