實時語音識別系統中,由于語音的數據量大,運算復雜,對處理器性能提出了很高的要求,適于采用高速DSP實現。雖然DSP提供了高速和靈活的硬件設計,但是在實時處理系統中,還需結

2011-10-03 11:10:53 1895

1895

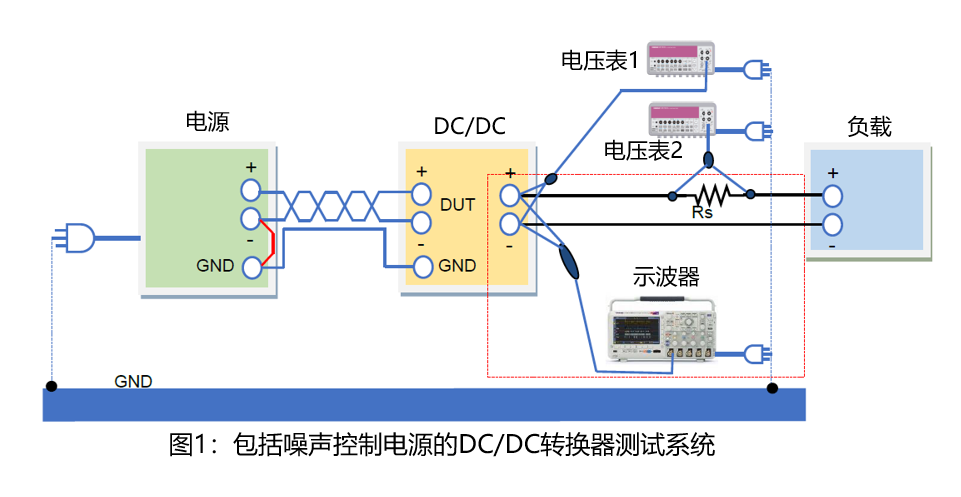

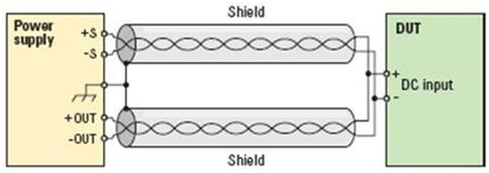

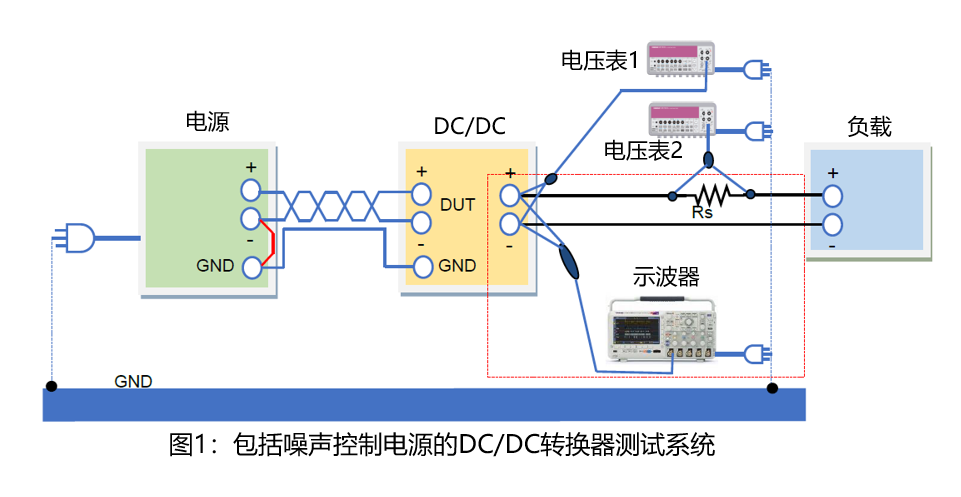

有些測試對于噪聲很敏感,那么如何降低噪聲?本文就選擇電源以及引線連接的方式兩個方面闡述如何降低測試中的噪聲。

2015-08-05 14:29:18 1554

1554

紋波噪聲是衡量電源的一個重要指標,一個好的電源必須要把輸出紋波噪聲控制在一個合理的范圍內。但一般有哪些行之有效的降低紋波噪聲的對策呢?下面我們拋磚引玉,簡單討論常用的八個方法。

2015-12-24 10:34:06 2003

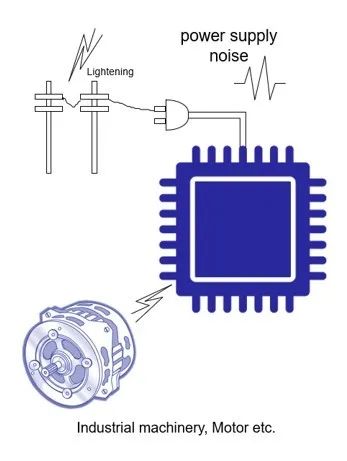

2003 外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。

2016-03-14 16:21:37 3173

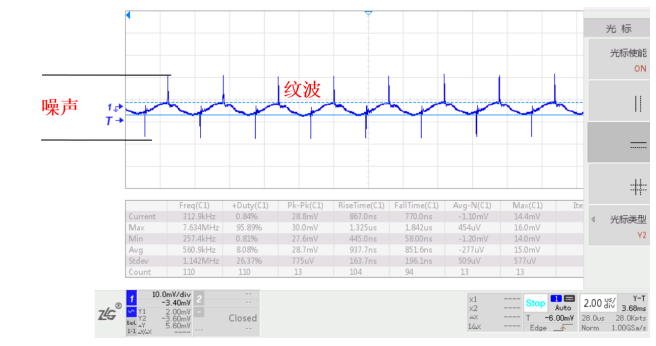

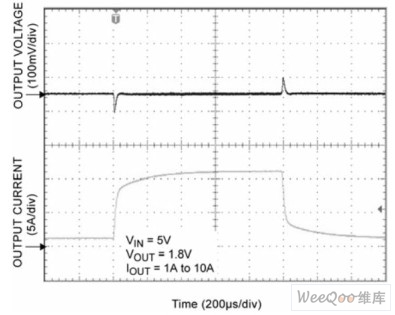

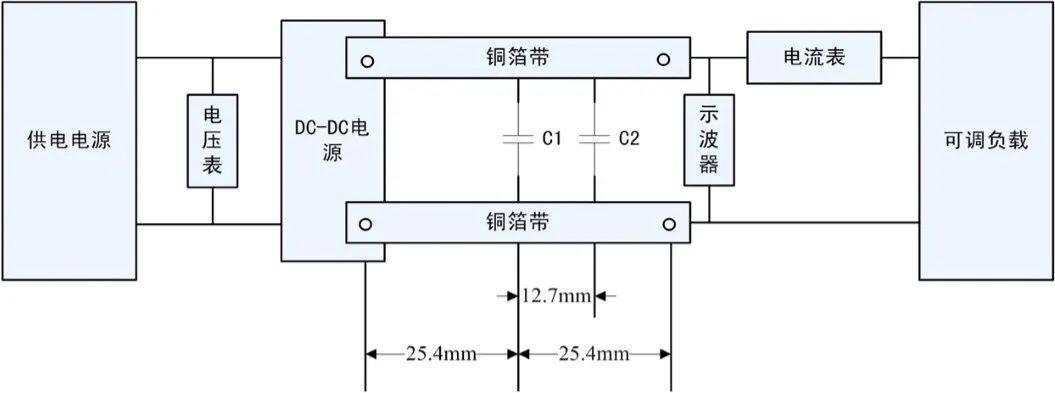

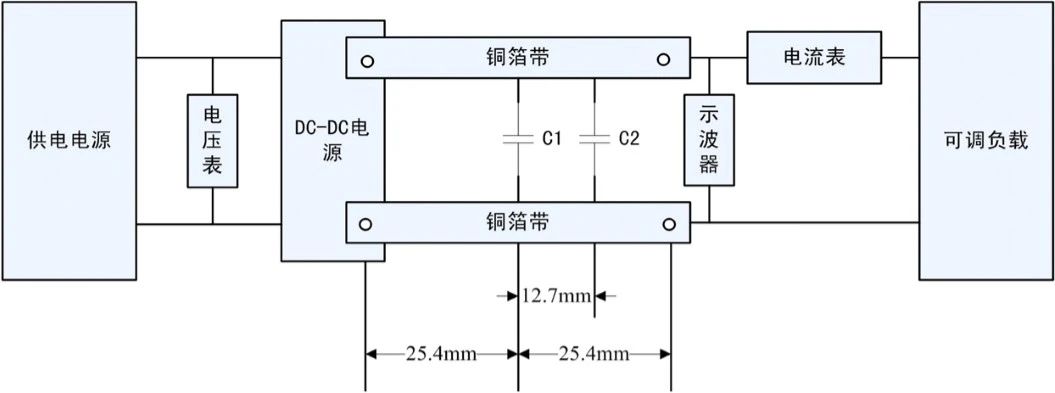

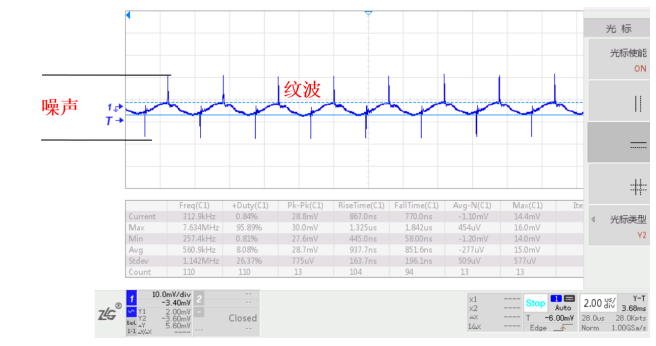

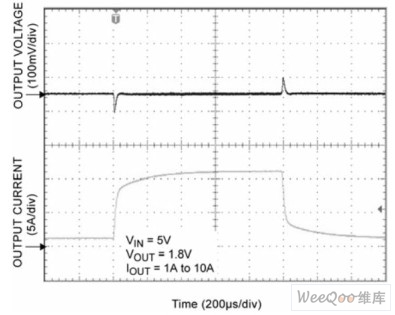

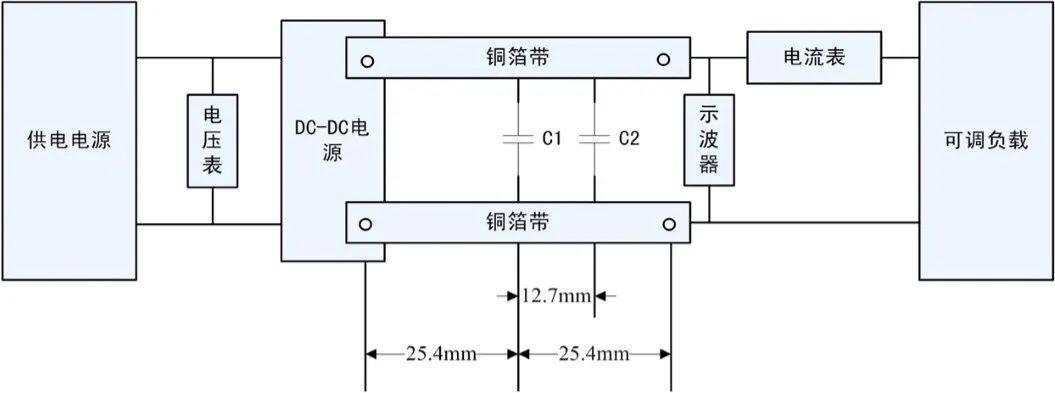

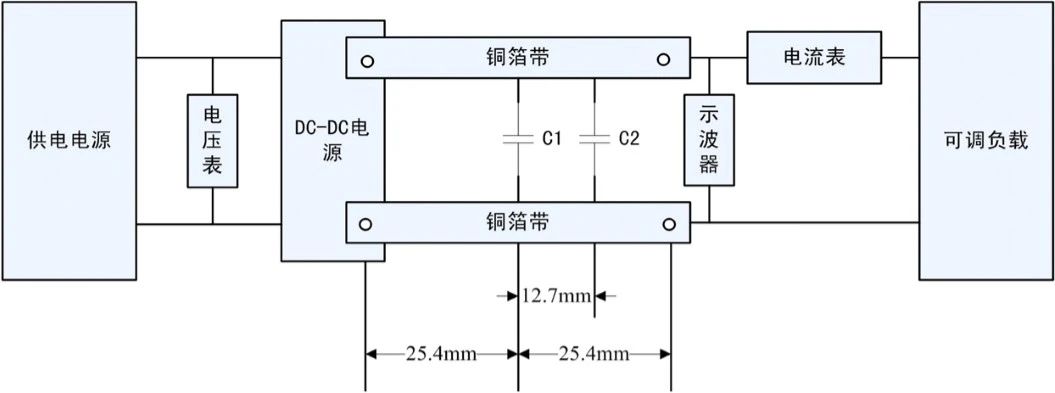

3173 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2018-08-08 14:53:36 8244

8244

在所有器件特性中,噪聲可能是一個特別具有挑戰性、難以掌握的設計課題。本文主要介紹電源噪聲對于高速DAC相位噪聲的影響。

2022-08-18 09:47:18 938

938 的 ADP1761取代。在某些偏移處噪聲降低多達10 dB,接近時鐘的貢獻(15002D)。圖17.AD9162評估板噪聲噪聲不僅會因為穩壓電源的器不同而大不相同,而且可能受到輸出電容、輸出電壓和負載

2018-10-17 10:22:55

Brannon,Brad。應用筆記AN-756,采樣系統以及時鐘相位噪聲和抖動的影響。ADI公司,2004。Reeder, Rob。 "高速ADC的電源設計." ADI公司,2012年2月

2017-05-10 14:39:39

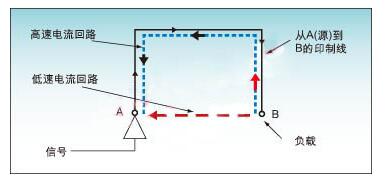

為什么要重視電源噪聲問題?電源噪聲是如何產生的?電源系統去耦如何設計?

2021-03-11 07:01:30

處理其發生的固有開關噪聲。開關電源不但可通過設計,最大限度地降低其開關噪聲,而且還可納入輸出濾波器,進一步降低該噪聲。但只有經過實際測量后才能確切知道電源所產生的噪聲級別。瞬態紋波噪聲為何要測量噪聲

2022-11-23 06:19:44

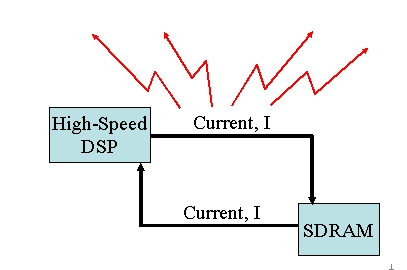

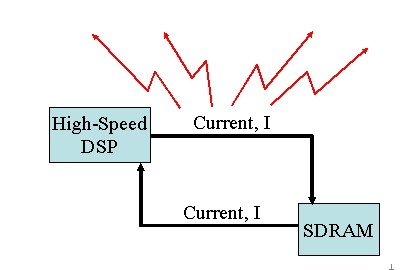

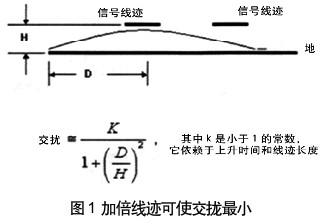

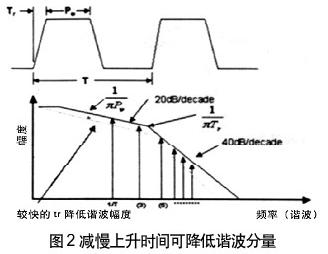

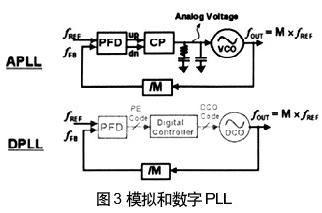

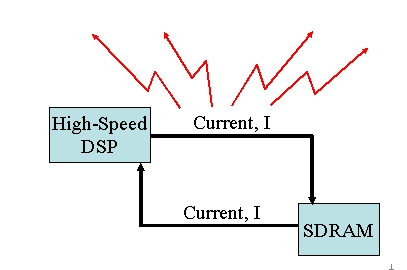

。本文就將為大家介紹在DSP系統中如何有效避免噪聲和EMI產生,對其中的電源隔離和鎖相環進行介紹。 電源隔離和鎖相環 如何實現最佳供電是控制噪聲和輻射的最大挑戰。動態負載開關環境很復雜,包括的因素

2018-11-30 17:14:11

PCB電源供電系統設計概覽降低電源供電系統的阻抗應該遵循什么原則?

2021-04-27 06:40:47

摘要:紋波噪聲是衡量電源的一個重要指標,一個好的電源必須要把輸出紋波噪聲控制在一個合理的范圍內。但一般有哪些行之有效的降低紋波噪聲的對策呢?下面我們拋磚引玉,簡單討論常用的八個方法。 1

2018-11-30 16:49:13

開關電源設計的噪聲降低法

2019-02-28 11:14:15

降低噪聲與干擾1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。(2) 可用串一個電阻的辦法,降低控制電路上下沿跳變速

2010-02-26 11:42:31

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2019-01-26 22:53:49

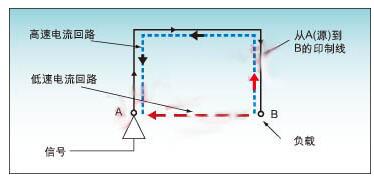

的若干問題。 電源設計 高速DSP系統PCB板設計首先需要考慮的是電源設計問題。在電源設計中,通常采用以下方法來解決信號完整性問題。 考慮電源和地的去耦 隨著DSP工作頻率的提高,DSP和其他

2012-10-23 21:57:52

針對在高速DSP系統中PCB板可靠性設計應注意的若干問題。 電源設計 高速DSP系統PCB板設計首先需要考慮的是電源設計問題。在電源設計中,通常采用以下方法來解決信號完整性問題。 考慮電源

2018-09-21 16:29:53

BGA封裝屬于球柵陣列貼片封裝,在開發中系統的物理實現上,也就是板級設計牽涉到很多高速數字電路的設計技術。高速系統中,噪聲干擾的產生是第一影響因素,高頻電路還會產生輻射和沖突,而較快的邊緣速率則會產生

2018-09-12 15:09:57

當今許多應用都要求高速采樣模數轉換器(ADC)具有12位或以上的分辨率,以便用戶能夠進行更精確的系統測量。然而,更高分辨率也意味著系統對噪聲更加敏感。系統分辨率每提高一位,例如從12位提高到13位

2018-10-19 09:34:26

第一篇 DSP系統的降噪技術 隨著高速DSP(數字信號處理器)和外設的出現

2009-04-08 12:07:41

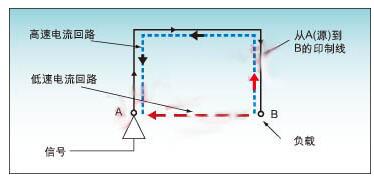

`高速布線的電源噪聲`

2012-09-21 13:52:56

噪聲沒有任何改變,依然為200mv左右,導致傳感器精度急劇降低。將電源模塊去掉,直接采用線性電源輸入,噪聲降低為10mv,ADR4550的輸出噪聲依然和其輸入電源噪聲一致。

現想咨詢下:

ADR4550為何沒有起到對電源噪聲抑制的功能?

2024-01-08 09:16:11

以上兩個參數,可以合理的設計電源工作頻率。 3.電源布局設計---噪聲的來源和降低 1)運放的輸入與輸出 在設計電源時,良好的布局可以降低電源噪聲,電源噪聲主要有三種:運算放大器的輸入與輸出

2023-03-16 15:55:02

小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路上下沿

2018-09-18 15:40:54

的產生是通過導體和通過輻射。很多電磁發射源,如光照、繼電器、DC電機和日光燈都可引起干擾。AC電源線、互連電纜、金屬電纜和子系統的內部電路也都可能產生輻射或接收到不希望的信號。在高速數字電路中,時鐘電路

2014-11-19 14:07:27

的一些小竅門。 下面是經過多年設計總結出來的,在PCB設計中降低噪聲與電磁干擾的24個竅門: (1) 能用低速芯片就不用高速的,高速芯片用在關鍵地方。 (2) 可用串一個電阻的辦法,降低控制電路

2018-11-28 17:05:55

致力于研究噪聲的測量和分析,為當代 環境問題作出自己的貢獻。 我們噪聲實時分析系統這一項目已經開展五年有余,項目經驗豐富。目前開發的噪聲分析系統是基于TMS320C6747這款DSP芯片,前期更是

2015-10-29 14:14:41

和低頻噪聲(1/f噪聲)等,在這里我們不予討論。外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。常見外部噪聲源電源紋波

2018-03-28 17:14:04

為什么要重視電源噪聲問題?怎么對電源系統的噪聲余量進行分析?如何計算?電源系統的噪聲來源?

2021-03-11 07:02:05

削弱。為了避免系統性能下降,必須充分了解信號鏈對電源噪聲的靈敏度。這可通過設定最大允許紋波來確定,最大允許紋波對于配電網絡(PDN)設計至關重要。知道最大允許紋波閾值后,就可以采用各種方法來設計優化電源。如果最大允許紋波具有良好的裕度,則PDN不會降低高速模擬信號處理器件的動態性能。

2021-06-16 09:18:18

在DSP系統中如何去避免出現噪聲和EMI問題?

2021-04-26 06:32:23

基于DSP和FPGA的高速串行通信系統設計

2015-03-16 15:47:04

摘要: 介紹了一種基于DSP 的智能電源管理系統設計和實現方案。本系統以TI 公司的TMS320LF2407A DSP 為控制核心,主要由信號采集模塊,電路調理模塊,DSP 處理模塊,顯示模塊

2018-09-26 16:02:51

電腦與擴音器),這種情況下有很大的噪聲,該如何解決?用什么規格的帶通濾波器合適?如果音頻信號的頻率范圍內還摻雜著電源噪聲又該如何解決?我加上濾波器后試了一下(什么型號不清楚)噪聲低了,聲音也低了。

2014-09-30 14:07:22

摘要:紋波噪聲是衡量dcdc電源模塊一個重要指標,一個好的dcdc電源模塊必須要把輸出紋波噪聲控制在一個合理的范圍內。但一般有哪些行之有效的降低紋波噪聲的對策呢?下面由小編為您講解一下具體的方法。1

2018-08-09 13:58:12

如何降低步進電機的噪聲?

2021-02-22 06:45:32

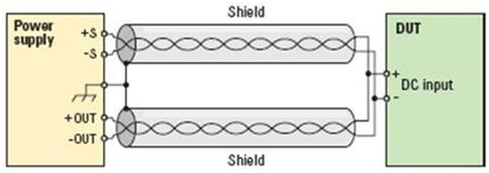

這篇應用指南為負責建造測試系統的工程師編寫。它介紹在把商用開關產品和測量儀器集成至測試系統時,如何降低噪聲耦合問題。

2019-07-22 12:09:22

:熱噪聲、散彈噪聲和低頻噪聲(1/f噪聲)等,在這里我們不予討論。外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。

常見

2023-11-21 06:27:27

、散彈噪聲和低頻噪聲(1/f噪聲)等,在這里我們不予討論。外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。 常見外部噪聲

2018-12-29 10:10:32

,在這里我們不予討論。外部的噪聲通常指電源噪聲、空間耦合干擾等,通常通過合理的設計可以避免或減小影響。降低外部噪聲的影響對發揮低噪聲運放的性能至關重要。常見外部噪聲源 電源紋波在全波整流的線性穩壓供電的電路

2017-10-19 23:34:27

進行適當的測試并解決噪聲問題,這些減緩就有可能避免。當涉及偏置模擬電路時,電源噪聲會導致系統性能低下,可能會降低產品的最終客戶價值。仔細想想某些傳感器模擬信號路徑上的電源問題。在這類系統中,噪聲將

2018-09-20 16:01:26

電路設計過程中非常關鍵的一個環節。 因此PCB板的設計質量相當重要,它是把最優的設計理念轉變為現實的惟一途徑。下面討論針對在高速DSP系統中PCB板可靠性設計應注意的若干問題。 一、電源設計 高速

2017-12-04 14:19:43

降低開關電源輸出紋波與噪聲的常用方法

2021-03-16 13:50:26

什么是電磁干擾?有什么方法可以降低DSP系統的電磁干擾嗎?

2021-04-23 06:10:26

電源噪聲。只有確定與電源頻譜輸出相匹配的閾值才可能實現優化電源系統設計。如果確保電源噪聲低于其最大規格值,則優化電源不會降低每個模擬信號處理器件的動態性能。電源噪聲對模擬信號處理器件的影響應了解電源

2021-06-21 09:26:33

本帖最后由 siyugege 于 2015-12-30 15:09 編輯

我們要怎么降低電源輸出紋波噪聲?紋波噪聲是衡量電源的一個重要指標,一個好的電源必須要把輸出紋波噪聲控制在一個合理

2015-12-30 11:30:42

本文介紹了一種基于PCI總線的高速噪聲檢測系統,介紹了采用PCI 9052作為PCI總線接口芯片的數據采集部分的設計原理,并說明了數據采集卡的高速采樣和速率可變的實現原理,給出了底層硬件同上層軟件的連接實現。

2021-04-09 06:21:14

高速DSP系統PCB板的特點有哪些?設計高速DSP系統中的PCB板應注意哪些問題?

2021-04-21 07:21:09

如何降低測試系統開關噪聲?

2021-04-14 06:06:47

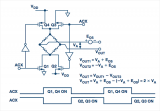

的時鐘參考。 2降低電源噪聲,提高轉換效率的通用方法 耗電系統無法避免電源噪聲。 一般而言,系統設計者應盡可能的嘗試使用低噪聲線性電源。然而,過高的管耗通常阻止了線性穩壓器的應用。當使用線性設備

2018-09-26 14:33:58

基于定點DSP的實時噪聲消除系統:介紹了一個基于16 位定點數字信號處理芯片ADSP-2187L 的實時音頻噪聲消除器,采用89C51作為控制單元協調輸入,輸出接口電路和DSP 處理電路的工作。

2009-09-08 09:13:08 19

19 如何避免在DSP 系統中出現噪聲和EMI 問題關鍵詞:噪聲 dsp 數字電路摘要:在任何高速數字電路設計中,處理噪聲和電磁干擾(EMI)都是一個必然的挑戰。處理音視頻和通信信

2010-01-14 18:48:46 15

15 基于DSP的線列陣流噪聲數據采集系統,針對拖曳線列陣聲吶的特點,為了能測試到對其性能影響最大的流噪聲,采用先進的DSP+CPLD結構,實現對多通道聲吶信號的檢測并對其分時采樣,然后

2010-07-21 17:11:49 18

18 摘要:本文介紹了高速DSP系統PCB板的特點以及可靠性設計應注意的幾個問題,包括電源設計、軟硬件抗干擾設計、電磁兼容性設計、散熱設計以及高速電路重要信號線的布線方法,使各

2010-12-13 21:59:24 0

0 如何避免在DSP系統中出現噪聲和EMI問題

在任何高速數字電路設計中,處理噪聲和電磁干擾(EMI)都是一個必然的挑戰。處理音視頻和通信信號的數字信號處理(DS

2008-07-27 23:33:03 304

304

在任何高速數字電路設計中,處理噪聲和電磁干擾(EMI)都是一個必然的挑戰。處理音視頻和通信信號的數字信號處理(DSP)系統特別容易遭受這些干擾,設計時應該及早

2009-04-22 11:47:20 609

609

電源完整性與地彈噪聲的高速PCB仿真原理及設計

高速數字電路板設計者所遇到的問題在幾年前看來是不可想象的。對于小于1納秒的

2010-03-13 15:11:50 1747

1747

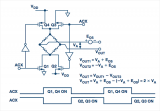

為復雜的DSP處理器設計良好的電源是非常重要的。良好的電源應有能力應付動態負載切換并可以控制在高速處理器設計中存在的噪聲和串擾。DSP處理器中的不斷變化的瞬態是

2010-07-02 11:56:12 1714

1714

隨著高速DSP技術的廣泛應用,相應的高速DSP的PCB設計就顯得十分重要。由于DSP是一個相當復雜、種類繁多并有許多分系統的數、模混合系統,所以來自外部的電磁輻射以及內

2010-09-30 09:41:48 727

727

開關電源的特征就是產生強電磁噪聲,若不加嚴格控制,將產生極大的干擾。下面介紹的技術有助于降低開關電源噪聲。

2011-12-19 16:28:34 2240

2240 為測試電子和機電器件設計開關系統所遇到的問題和設計產品本身一樣多。隨著器件中高速邏輯的出現以及與更靈敏模擬電路的連接,使得降低測試開關系統中的噪聲比以前任何時候更

2012-05-07 14:49:38 702

702

在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。 1、電源的紋波與噪聲圖示 紋波和噪聲即:直流電源輸出上疊加的與電源開關頻率同頻的波動為紋波,高頻雜音為噪聲。

2016-11-09 02:08:11 8958

8958

如何降低電源紋波噪聲的分析與應用

2017-02-08 01:27:55 16

16 基于DSP的通信電源監控系統的設計_俞斌

2017-03-19 11:45:23 2

2 基于雙DSP和雙FPGA的高速圖像處理系統設計_吳雷

2017-03-16 09:28:51 2

2 本文闡釋1/f噪聲是什么,以及在精密測量應用中如何降低或消除該噪聲。

2018-07-11 07:30:00 61482

61482

高速PCB設計之DSP系統的降噪技術

2017-08-28 08:53:38 9

9 基于FPGA和DSP的高速圖像處理系統

2017-10-19 13:43:31 19

19 引起的噪聲使音頻、視頻、圖像和通信功能降低并對達到FCC/CE商標認證造成問題。為了降低電源噪聲,對于高速DSP系統設計人員來講,識別和找出可能的噪聲原因以及采用良好的高速設計實踐是關鍵。本文說明交擾、鎖相環(PLL)、去耦/體電容器在降低噪聲中

2017-10-26 15:35:25 8

8 引起的噪聲使音頻、視頻、圖像和通信功能降低并對達到FCC/CE商標認證造成問題。為了降低電源噪聲,對于高速DSP系統設計人員來講,識別和找出可能的噪聲原因以及采用良好的高速設計實踐是關鍵。本文說明交擾、鎖相環(PLL)、去耦/體電容器在降低噪聲中

2017-10-29 10:47:33 0

0 隨著微電子技術的高速發展,新器件的應用導致現代 EDA 設計的電路布局密度大,而且信號的頻率也很高,隨著高速器件的使用,高速 DSP(數字信號處理)系統設計會越來越多,處理高速 DSP 應用系統

2017-11-07 11:00:43 0

0 如何利用高速dsp和準pid控制的數字控制電源?

2018-04-09 11:15:09 24

24 開關電源的特征就是產生強電磁噪聲,若不加嚴格控制,將產生極大的干擾。下面介紹的技術有助于降低開關電源噪聲,能用于高靈敏度的模擬電路。

2018-10-14 10:43:00 4471

4471 當高速DSP系統中的噪聲無法根本消除時,則應該將其減到最小。電子元器件內部都有噪聲,故仔細地選擇器件特性,并選用適當的器件是至關重要的。除了器件的正確選擇外,還有兩種通用的技術,即PCB布線和回路

2019-06-06 14:50:50 574

574

對于高速DSP而言,降低噪聲是最重要的設計準則之一。來自任何噪聲源的過大的噪聲,都會導致隨機邏輯和鎖相環(PLL)失效,從而降低可靠性。還會導致影響FCC認證測試的輻射干擾。此外,調試一個噪聲很大的系統是極端困難的;因此,要消除噪聲-如果能夠徹底消除的話-則要求在電路板設計中花費大量的功夫。

2019-05-30 14:44:39 2624

2624

紋波噪聲是衡量電源的一個重要指標,但有多少人知道紋波和噪聲其實是兩個性能指標,降低紋波和噪聲的方法是有一定區別的,本文將與大家一起探索如何降低紋波和噪聲。

2019-06-20 14:27:08 11684

11684

高速DSP系統PCB板設計首先需要考慮的是電源設計問題。在電源設計中,通常采用以下方法來解決信號完整性問題。

2020-01-03 15:13:35 1344

1344 降低開關電源的紋波噪聲(通信電源技術雜志訂閱)-?降低開關電源的紋波噪聲,非常好的資料一、什么叫紋波??紋波(ripple)的定義是指在直流電壓或電流中,疊加在直流穩定量上的交流分

量;

它主要有

2021-09-27 09:41:41 28

28 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。那么模塊的紋波噪聲該如何降低?下文為大家從紋波噪聲的波形、測試方式、模塊設計及應用的角度出發,闡述幾種有效降低輸出紋波噪聲的方法

2022-02-11 15:18:00 13

13 在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。紋波噪聲的測試方法對于中小

2023-05-08 09:48:54 472

472

在應用電源模塊常見的問題中,降低負載端的紋波噪聲是大多數用戶都關心的。下文結合紋波噪聲的波形、測試方式,從電源設計及外圍電路的角度出發,闡述幾種有效降低輸出紋波噪聲的方法。

2023-06-20 17:48:24 1184

1184

前篇回顧 如何降低微控制器系統中的噪聲影響(1) 如何降低微控制器系統中的噪聲影響(2) 在本系列文章中,我們研究了噪聲以及它如何干擾基于微控制器的系統的操作。本篇作為系列內容的最后一篇,我們將看看

2023-08-09 12:05:02 439

439

如何降低微控制器系統中的噪聲影響(2)

2023-10-25 17:41:55 241

241

降低電源紋波噪聲的方法與實例

2023-10-24 17:37:22 261

261

在電子設備和系統中,電源噪聲是一個普遍存在的問題。電源噪聲會影響設備的性能、穩定性、可靠性和安全性。為了降低電源噪聲,我們可以采用各種方法,其中一種非常有效的方法是利用電源濾波器。那么,電源濾波器是怎么降低電源噪聲的?跟著電源濾波器維愛普小編一起來看一下。

2023-09-25 12:35:08 428

428 電源濾波器是怎么降低電源噪聲的? 隨著現代電子設備的發展,我們的生活變得越來越依賴電力。但是,這些設備所使用的電力并非完美的直流電,往往會受到來自外部環境的各種噪聲干擾,例如電源中的高頻噪聲,通常

2023-10-25 15:38:29 488

488 噪聲是包括電源在內的測試系統中多余的但卻無法避免的問題。一部分的噪聲總是由電源(除了電池是低噪聲的電源)產生或者傳送的。

2023-11-15 15:40:54 314

314

降低電源適配器的輸出紋波和噪聲可以采取以下幾種方法

2023-11-22 15:02:51 437

437 降低開關電源噪聲

2023-11-24 15:39:50 186

186 電源濾波器是怎么降低電源噪聲的? 電源濾波器是一種電子裝置,用于減少或消除電源中的噪聲。噪聲是電力系統中的一個常見問題,它可以由各種因素引起,包括電源脈動、電源雜散、電磁干擾等。這些噪聲不僅會對

2023-12-15 14:37:56 374

374 如何降低開關電源輸出紋波與噪聲

2024-03-12 19:49:03 53

53

電子發燒友App

電子發燒友App

評論