英特爾公司最近宣布他們將退出嵌入式市場。在1970年代,英特爾通過引入8048 μC創(chuàng)造了嵌入式市場,隨后8051μC的普及應用極端火爆。但是,該公司將停止生產(chǎn)8051、251、8096/196、188/186、i960、所有版本的386 (包括386EX)和486,總計起來,大約700種器件型號正在停產(chǎn)。采用基于ASIC的μC/μP (微控制器/微處理器)的客戶預期,其它的供應商也將做出器件過時的宣告,特別是那些最近被私人股權(quán)投資公司收購的、要減產(chǎn)特定的μC/μP的供應商,他們可能導致所提供的產(chǎn)品被合并。

大多數(shù)設計工程師都關(guān)注器件的過時問題,在工業(yè)、科學、汽車和醫(yī)療市場的工程師對此問題更為關(guān)注。因為這些市場的產(chǎn)品生命周期長,基于ASIC的μC/μP可能是開發(fā)一個產(chǎn)品的成本極高的方法;因為假如μC/μP停產(chǎn),那么,它就可能涉及對PCB、軟件接口、板級支持封裝(BSP)開發(fā)、驗證、測試和對整個最終產(chǎn)品進行多次質(zhì)量認證的再一次工程努力。

大多ASIC供應商確實提供諸如最后一次購買(LTB)和硅晶圓購買計劃之類的替代解決方案,但是,兩種選擇的成本都是高昂的。很難預測(更合適的說法是“猜測”)在產(chǎn)品生命周期中需要采購和存儲多少μC/μP,與此同時,庫存管理正試圖避免在貨架上把巨大數(shù)量的元器件存放幾個月或幾年。

軟性、靈活的“生命終止”解決方案

當與軟處理IP核相結(jié)合時,可編程嵌入式平臺提供獨一無二的優(yōu)勢。采用一種軟處理IP核及幾個現(xiàn)成的FPGA系列,你可以利用嵌入式行業(yè)中范圍廣闊的不同應用的優(yōu)勢以及跟分立器件市場相關(guān)的不確定性。

回避退化風險的一種最佳解決方案是利用在硅器件層上的靈活FPGA構(gòu)造及具有定制外設的軟IP處理器。賽靈思為英特爾以及其它供應商的生命終止器件提供多種解決方案。

這些解決方案依賴于你現(xiàn)有的軟件代碼基礎。如果它是采用匯編語言編寫的,一種選擇是把代碼與C語言對接;如果這種辦法不可行,你可以試用Xilinx® AllianceCORE?合作伙伴網(wǎng)絡提供的像186和8051一樣成熟的μC/μP IP模塊。這將包括把外設集成到你特定的生命終止器件型號并進行驗證和測試。

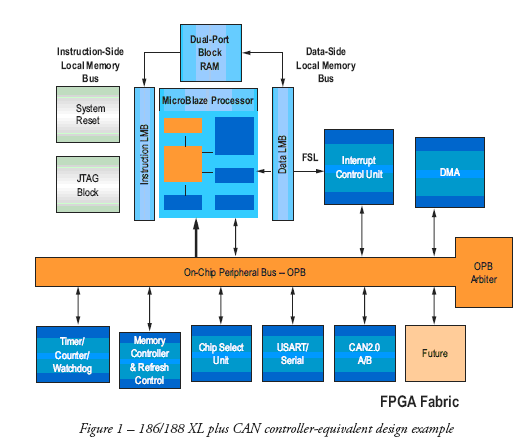

圖1:設計選項。

? ???Intel 188/186 Features 英特爾188/186功能

MicroBlaze with Memory Controller 具有存儲控制器的MicroBlaze

CPU Static No Cache (12, 20, 25 MHz) CPU靜態(tài)沒有高速緩沖存儲器

MicroBlaze CPU Core with 16K Cache (104 MHz) 具有16K高速緩沖存儲器的MicroBlaze CPU核

Clock Generator 時鐘發(fā)生器

DCM on Xilinx FPGA 在Xilinx FPGA上的DCM

Two Independent DMA Channels for External Memory and I/O

? ?? ? 用于外部存儲器和I/O的獨立DMA通道

OPB Central DMA Controller OPB中央DMA控制器

Three Programmable 16-Bit Timers 三可編程16位定時器

OPB Timer/Counter (Four)材OPB定時/計數(shù)器

Local Bus Controller 本地總線控制器

OPB Bus Interface OPB總線接口

DRAM Refresh Control Unit DRAM刷新控制單元

OPB Memory Controller Interface OPB存儲控制器接口

Programmable Interrupt Controller 可編程中斷控制器OPB Interrupt Controller OPB中斷控制器

Programmable Wait State Generator 可編程等待狀態(tài)發(fā)生器

State Machine or an OPB Timer/Counter (Included Above) 狀態(tài)機或OPB定時器/計數(shù)器(包括上面)

Chip Select Logic 片選邏輯

OPB GPIO片上外設總線 (OPB) 通用IO (GPIO)

System-Level Testing Support 系統(tǒng)級測試支持

OPB JTAG UART

如果現(xiàn)有的軟件代碼采用C語言編寫,賽靈思已經(jīng)在Spartan?、Virtex? FPGAs、PowerPC? μP 32位 RISC嵌入式Virtex FPGA系列以及流行的MicroBlaze? 軟IP處理器中提供了真正的不會過時的解決方案。

MicroBlaze軟處理器是一種具有5級管道執(zhí)行以減少每條指令占用的時鐘數(shù)(CPI)的32位RISC處理器。該產(chǎn)品的供貨已經(jīng)有5年時間,最新的版本是MicroBlaze v5.0,它是100%二進制向下兼容的。二進制向下兼容性意味著可以運行較老的MicroBlaze版本或不需要軟件對接就能在MicroBlaze v5.0系統(tǒng)上運行以前的代碼。這就確保了基于MicroBlaze的μC設計真正不會過時。隨著未來版本的MicroBlaze軟IP處理器的推出,用戶將不需要考慮任何過時問題就能夠從較新的功能集上獲益。

當對性能進行了配置之后,MicroBlaze v5.0處理器以210 MHz的速度運行在Virtex-5 LX器件上。賽靈思在嵌入式開發(fā)工具套件(EDK)包中向客戶免費提供MicroBlaze軟處理器許可證,此外,不存在單位版稅,所以,不論你銷售的是一片或是一百萬片芯片,你都可以擁有你自己特定的MicroBlaze設計。

為了使你能夠開發(fā)一種針對你自己應用的特殊、靈活和獨一無二的解決方案,賽靈思已經(jīng)開發(fā)了稱為Platform Studio的集成開發(fā)環(huán)境(IDE)。Xilinx Platform Studio (XPS) IDE和工具套件被包含在EDK包之中。XPS 提供讓你在系統(tǒng)的軟件和硬件層中定制各種解決方案的真正靈活的工具。XPS的組成部分包括:一套稱為基本系統(tǒng)構(gòu)建器的快速IP生成工具(BSB);一套基于GNU/GCC的軟件開發(fā)工具;一套稱為XMD的處理器除錯引擎;一套稱為SDK的基于Eclipse的軟件開發(fā)套件;一套處理IP外設模塊的擴展庫;MicroBlaze 32位RISC處理器。

賽靈思嵌入式處理器獲得了由RTOS(實時操作系統(tǒng))中間件、除錯和電子系統(tǒng)級(ESL)工具供應商組成的生態(tài)系統(tǒng)的支持,他們也將有助于你定制自己的產(chǎn)品。

平臺IP

賽靈思利用MicroBlaze處理器、外設、SDRAM和閃存控制器提供一種等效于“生命終止”器件的設計。這種來自英特爾公司和其它供應商的針對“生命終止”器件的預集成參考設計解決方案被稱為Platform IP,這種解決方案使你能夠快速地開發(fā)并部署真正不過時的方案。

例如,對于英特爾公司的186/188XL系列,表1列出了在這些產(chǎn)品上的外設和它們的賽靈思等效IP模塊。

圖1:186/188XL加上等效于CAN控制器的設計例子,該方案的組成部分包括:

?一個Spartan-3E FPGA平臺;

?一個以104 MHz速度運行在Spartan-3器件上的MicroBlaze 32位RISC CPU;

?等效于186/188XL的通用外設;

?內(nèi)部存儲器SDRAM和閃存控制器;

? CAN (控制器區(qū)域網(wǎng)絡)2.0 A/B MAC

這種靈活的系統(tǒng)設計可以減少各種風險,因為你可以把任何將來的要求以新的定制邏輯模塊、DSP、外設或第三方IP的形式添加到FPGA之中。 此外,該系統(tǒng)還可以被方便地重新配置。

在表2中的設計表示的是對FPGA構(gòu)造的有效使用。賽靈思的Platform IP以參考設計的形式為英特爾公司和無數(shù)其它供應商的“生命終止”產(chǎn)品提供解決方案,使你能夠快速地部署針對你的過時器件的解決方案。

圖1:186/188XL加上等效于CAN控制器的設計例子

Instruction-Side Local Memory Bus 指令側(cè)本地存儲器總線

Dual-Port Block RAM 雙口模塊RAMData-Side Local Memory Bus 數(shù)據(jù)側(cè)本地存儲器總線

System Reset 系統(tǒng)復位

JTAG Block JTAG模塊

MicroBlaze Processor MicroBlaze處理器

Instruction LMB 指令LMB

Data LMB 數(shù)據(jù)LMB

FSL快速單工連接

Interrupt Control Unit 中斷控制單元

DMA 直接存儲器存取

On-Chip Peripheral Bus –片上外設總線 (OPB)

OPB Arbiter OPB仲裁器

Timer/Counter/Watchdog 定時器/計數(shù)器/看門狗

Memory Controller & Refresh Control 存儲控制器和刷新控制

Chip Select Unit 芯片選擇單元

USART/Serial USART/串行口

CAN2.0 A/B

Future 將來的需求

FPGA Fabric FPGA構(gòu)造

表2:針對實例設計的FPGA構(gòu)造要求。

=====================

? ?? ? Xilinx MicroBlaze Processor with Internal SDRAM Controller

? ?? ?具有內(nèi)部SDRAM控制器的賽靈思MicroBlaze處理器

Slices 邏輯片

LUT 查找表

FF觸發(fā)器

Block 模塊

RAM隨機存取存儲器

MicroBlaze CPU Core with 16K Cache 具有16K高速緩沖存儲器的MicroBlaze CPU核

DCM on Xilinx FPGA 在Xilinx FPGA上的DCM

OPB Central DMA Controller OPB中央DMA控制器

OPB Timer/Counter (Four) OPB定時器/計數(shù)器

OPB Bus Interface OPB總線接口

OPB SDRAM Controller OPBSDRAM控制器

OPB Interrupt Controller OPB中斷控制器

State Machine or an OPB Timer/Counter (Included Above) 狀態(tài)機或一個OPB定時器/計數(shù)器(包括上面的)

OPB GPIO片上外設總線 (OPB) 通用IO (GPIO)

OPB JTAG UART

Peripherals 外設

Internal Memory Controller (SDRAM Controller) 內(nèi)部存儲控制器(SDRAM控制器)

OPB Interrupt Controller OPB中斷控制器

Flash Controller 閃存控制器

Total Slices, LUT FF, Block RAM Required 總的邏輯片,LUT FF,所需要的模塊RAM

Spartan-3E Family Products Spartan-3E系列產(chǎn)品

XC3S500E

Utilization 利用率

XC3S1200E

Utilization 利用率

XC3S1600E

Utilization 利用率

=========================

結(jié)論

所有的芯片制造商都將在某一個時間點對某些產(chǎn)品實施停產(chǎn),但是,F(xiàn)PGA是可編程、可再編程且可現(xiàn)場升級的。因此,作為一個FPGA用戶,當你為利用成本、密度和功耗趨勢而在FPGA平臺系列上進行代碼移植時,你可以確信你花費多人年所做的軟件開發(fā)可以被安全地投資到一個嵌入式目標設計之中,該嵌入式目標設計可以繼續(xù)運行同你第一天編制的代碼一樣的軟件代碼,即使它可能正在新的硬件上運行。

賽靈思處理核使客戶能夠有效地利用FPGA構(gòu)造并有效地管理成本。當MicroBlaze和PicoBlaze 處理器(后者是采用匯編語言編寫的8位參考設計)被嵌入到FPGA構(gòu)造之中時,通過你現(xiàn)有和配置的穩(wěn)定的平臺,可以消除處理器過時的問題。隨著Spartan系列到Virtex 系列FPGA的應用范圍向商用和汽車級工業(yè)領(lǐng)域的跨越,軟處理器成為防止設計過時的理想解決方案。你不僅僅能夠獲得可編程邏輯所提供的靈活性、一體化和可升級性,而且可以獲得專門滿足你的設計要求而定制的處理器。

MicroBlaze處理器的軟件本質(zhì)意味著它可以被例示到無數(shù)的平臺FPGA器件之中,覆蓋廣泛的器件配置和價格點。完全采用軟處理器核和可定制IP就可以替代你的過時器件。因為MicroBlaze解決方案是軟處理器IP核,你的設計永遠不會因一個處理器芯片的“生命終止”而過時,后續(xù)版本將保持100%的二進制向下兼容性。此外,源代碼許可協(xié)議是現(xiàn)成的。

電子發(fā)燒友App

電子發(fā)燒友App

評論