一、引言

在概念上,電磁兼容性(EMC)包含系統本身的電磁敏感性(EMS)以及電磁雜音發射(EME)兩個部分。EME描述的是器件在測試(DUT)的情況下是噪聲源,而EMS描述的是器件在 DUT的情況下是噪聲受害者。在大多數系統設計中,EMC變得越來越重要。如果設計的系統不干擾其它系統,也不受其它系統發射影響,并且不會干擾系統自身,那么所設計的系統就是電磁兼容的。

在電磁兼容設計中,“受害方”的概念通常指那些由于設計缺乏EMC考慮而受到影響的部件受害部件可能在基于MCU的PCB或者模組的內部,也可能是外部系統通常的受害部件是汽車免持鑰匙入車(Keyless-Entry)模組中的寬帶接收器或者是車庫門開啟裝置接收器,由于接收到MCU發出的足夠強的雜訊,這些模組中的接收器會誤認為接收到了一個遙控信號。

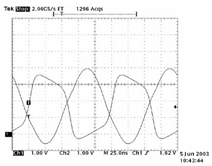

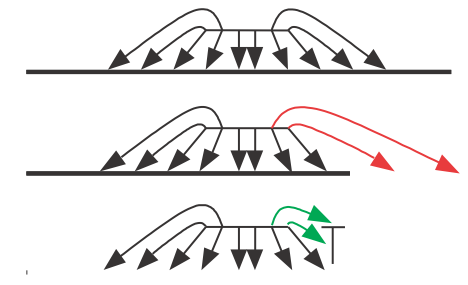

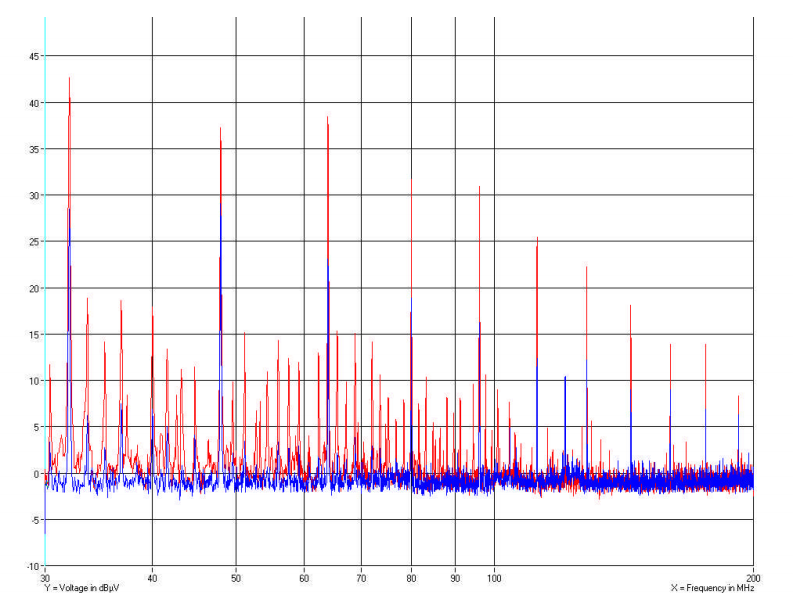

從長遠角度來看,電磁環境噪聲在一個給定的空間內是增長的,如圖1曲線所示,當在電子設備的抗干擾性高于電磁環境噪聲任何點時,電子設備的功能都不將受影響,遺憾的是,現在電子系統大部分具有較高的工作頻率和較低的電平開關門限(由于較低工作電源),防噪聲能力逐漸下降,如圖1中的曲線2。

?

圖1∶環境噪聲長遠發展趨勢

二、MCU中存在的EMC

MCU一般包括通用型和專用型兩類,大部分都采用了各種不同形式的EMC技術,其中在用戶端無任何措施的情況下,有些技術是還是有效的,其它則需要適當的留心PCB設計。因此可以說,雜訊來源主要有兩部分∶MCU的內部噪聲,MCU傳播到外面的噪聲。

MCU內部存在四種主要的噪聲源∶內部匯流排和節點同步開關產生的電源和地線上的電流;輸出管腳信號的變換;振蕩器工作產生的雜訊;開關電容負載產生的片上信號假像。根據經驗,實際應用中高頻率的窄帶雜訊比寬帶雜音能耗高,所以以下主要介紹窄帶雜訊。

1、主要噪聲源

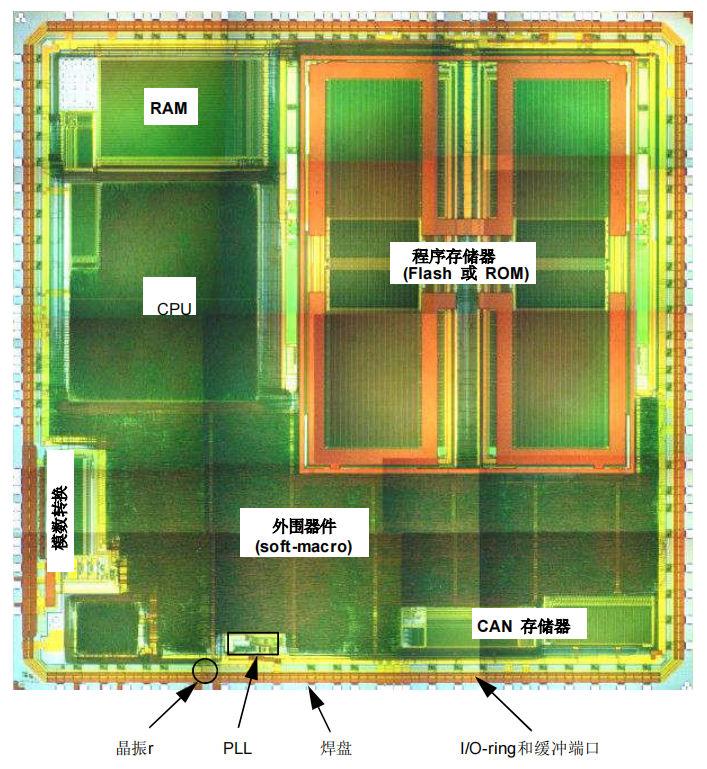

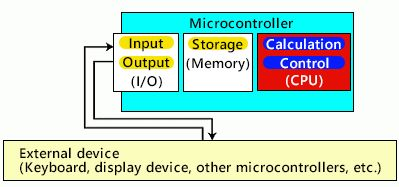

除AD轉換器、振蕩器和I/Oring之外,所有內部邏輯被列為內核。典型的內核和外部引腳是沒有關聯的,但電源引腳除外。例如,在圖2中內核包含CPU、鎖相環、程序記憶體、RAM及周邊器件包括CAN記憶體。 I/Oring包括帶有埠緩沖的電源和地面通道系統以及保護電路。所以,大多數MCU的I/Oring電源和內核電源是分開的。

?

圖2∶典型的MCU布局

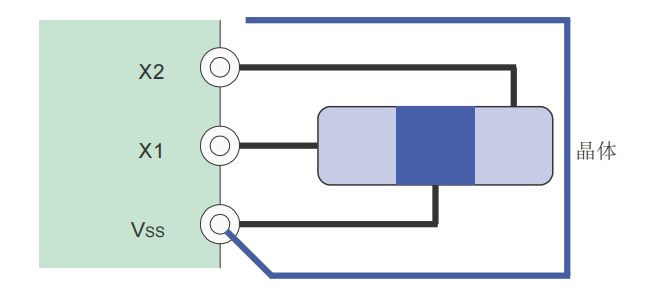

(1)振蕩器

當涉及到時鐘和窄帶雜訊,大家自然而然地就會想到振蕩器。圖3顯示了NEC公司典型MCU的石英振蕩器信號X1和X2的措施。雖然信號不是完全的正弦波形,但比較接近。事實上,根據頻譜分析僅能表示少數一些諧波。此外,和MCU的總功耗相比,振蕩器的功耗是相當較低的,因此MCU的石英振蕩器引起的噪音輻射相當低。然而,信號形狀和其頻譜可能大大有別于其它類型的振蕩器,例如RC振蕩器。

?

圖3∶MCU的石英振蕩器引起的噪音

(2)內核、PLL和時鐘樹

正弦時鐘不能使用在如MCU等內部是數位邏輯的器件上,因此,在CMOS型MCU上,振蕩器時鐘被整形為矩形,并且通過時鐘樹分布在內部裝置中。由于時鐘具有多種用途,到時鐘樹的各分支具有傳播延遲,必須調整時鐘邊緣到各地裝置大約在同一時間。所有開關型核心組件的電流幾乎是在同一時間內,由此內核的脈沖電流是一個主要的內核噪聲源。

MCU通常使用兩種邊緣的時鐘,由此內核電流的窄帶頻譜在內核的運行頻率及其諧波頻率上呈現電流峰值,呈現的最高頻率一般是內核運行頻率的兩倍。由于MCU通常包括一個或多個時鐘分頻器,因此低頻諧波也必須考慮。最后,內部資料操作等在低電平時提供一些寬帶雜訊。一方面,振蕩器之前的外擴也是一個小的噪聲源,另一方面,內核電流是和內核的運作頻率相關的。

如果內核頻率是一樣的,利用一個較慢的振蕩器和鎖相環(例如4MHz×4=16MHz)或使用較快振蕩器(例如16MHz),這樣應當引起相似級別的輻射。

(3)外部記憶體接口

外部記憶體接口包括地址匯流排,資料匯流排和一些控制信號。地址匯流排由MCU輸出,由于非線性存取順序提供的是非周期信號,因此,從EME角度講,地址匯流排相當于寬帶雜訊,低地址位通常比較高的地址位具有更多的開關頻率,所以這些都是較為重要的信號。

如果外部記憶體是唯讀或Flash記憶體,資料匯流排由記憶體驅動,即便記憶體是RAM,讀取周期也通常占主導地位。因此,資料匯流排的電磁輻射主要是決定于記憶體。

對于控制信號的電磁輻射,是記憶體接口上最應當注意的部分。最關鍵的信號是系統和/或記憶體的時鐘驅動器(SDRAM),因為它可產生巨大的窄帶雜訊,在啟動狀態下,即使引腳是開路的,它的噪聲也是較大的(參見到 I/O埠串擾的說明),因此無論任何地方,時鐘驅動器都應該被關掉。最后,由于這些開關信號(RAS、CAS、ASTB等)常常無規律的反復跳變,所以它們是潛在的噪聲源。

(4)I/O-ring上的通用埠

這些引腳的電磁輻射無法估計,由于這些引腳一般由用戶配置。靜電或偶爾開關引腳應不會造成重大的輻射,而頻繁開關切換的引腳已被視為潛在噪音來源。重復的切換引腳由于其窄帶特性可能比非重復引腳包括較高的雜訊,例如系統時鐘或CSI時鐘,還有CSI資料輸出或CAN資料輸出。

2、雜音傳播到非開關引腳

開關引腳是很明顯的噪聲源,更糟糕的是,它會對不相連的引腳產生輻射影響。

供應系統一般是由一個或多個電源引腳以及相對應的地引腳組成,MCU一般提供幾種隔離供電系統,不同的電源以及相對應的地是彼此相互隔離的,每個供電系統必須至少有一個去耦電容,在較寬的頻率范圍提供所需低阻抗電源。

在MCU內部,任何組件都直接或間接地連接到至少一個供電系統上,這樣,MCU內部任何轉換都會引起電流流動。電流輻射是與電流流動的環路面積成正比的,因此,這些回路要設計盡可能小,在這?最佳示例是MCU與去耦電容之間的電流回路。

任何電源都具有非0Ω的源阻抗,特別是在頻率較高的情況下,導線電感阻抗變得很大時,因此脈沖電流會將紋波疊加到直流電源上以至引起輻射,所以提供給MCU低阻抗的電源,可減少這種輻射。

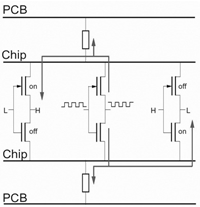

(2)內核到I/O口的串擾噪聲

(a)共同阻抗耦合∶任何兩個電路在它們的供電時共享同一阻抗,彼此之間將會產生串擾雜訊。這個雜訊是由與壓降相關的核電流引起的,這?的壓降是通過粘合線和引腳自感引起的,在圖4中以電阻的形式表示。即使PCB的電源電壓系統是遠離各種紋波電壓,但片內電源也是有噪聲的。因為埠緩沖區和內核是同一種內部電源,雜訊通過啟動的電晶體傳遞到每個輸出接腳,這不僅影響輸出管腳,還影響輸入引腳,輸入引腳被影響取決于芯片內部的寄生電容(例如保護電路)。在對EME敏感的情況下,可能需要對每一個引腳濾波,至少對于多引腳的MCU,這是基于成本和空間的原因。如圖4的右半部分是內核隔離供電系統的例子,通過此辦法耦合到外部。為了有效避共同阻抗耦合的弊端,應該從電源和地面兩方面的隔離來考慮,這樣,內核的I/O埠關聯輻射可大大改善。

?

圖4∶共享與隔離電源的串擾

(b)容性和感性耦合∶共同阻抗耦合是引起從內核到I/O埠的串擾的重要原因,不過,容性和感性耦合在芯片內部或者包裝上也會發生。由于具有相當高的源阻抗,電容耦合應該不會有太大問題。只要一個高頻電流在另一條導線邊流過,就會發生電感耦合,在芯片內部,通過優化走線已經把這一效應降至最低,但是粘合線難以優化,因為它是一個高度連接結構,因此與內核電源和地引腳附近的引腳,必須要考慮內核關聯噪聲。

(3)I/O埠間的串擾

如上所述,由于共同阻抗耦合的串擾效應一般也發生在I/ O埠之間。顯然,不是每一個I/O埠可以被提供獨立的供電系統。雖然串擾的影響可以通過芯片設計措施減到最低,但不能避免。比如,應用方面可以利用的對策是降低頻率或對影響最嚴重引腳進行濾波。通常輸入的串擾比輸出的串擾低,重新配置輸入和輸出可以幫助解決這個問題,不必要的開關信號也應該避免,例如,如果系統時鐘驅動器沒有被使用(引腳開路)但處于活動狀態,只要對其它 I/O埠的串擾稍高,就不符合EME的苛刻要求。

?

圖5∶I/O埠間的串擾

三、MCU的片上EMC措施

多年來,CMOS技術MCU集成了各種EMC技術,雖然片上電容和倍頻時鐘發生器是有效的,但對PCB的設計方面卻沒有任何措施。

1、片上電容

EME優化退耦目標是通過一個或更多的去耦電容提供一個最高所需高頻電流。高頻電流存放在片上的開關電路中環路越多和電容越低對其它供電電路影響較大。為優化連接線路的阻抗,通常電容盡可能接近MCU的供電引腳。為減少電流環路輻射,應當減少環路面積。僅用PCB設計技術難以實現最大程度的改善。因此,慣用對策是將部分去耦電容放到芯片內部從而減少連接阻抗,并且適當的考慮電流回路面積,這些片上電容太小以至不能提供整個芯片去耦,所以PCB上的電容仍是必要的,然而,對于較高的頻率范圍,它們可以很好地減少輻射。

2、擴展時鐘產生器頻譜(SSCG)

高頻窄帶輻射相對寬帶輻射更重要。窄帶頻譜僅僅是部分離散頻率,而在中間顯示環境噪音,糟糕的是,只要有一個高峰值超過限額,應用系統就不能通過測試,而寬頻帶地區可能會距離限制較遠,通過調節CPU的運行頻率,高頻能量分布在較廣泛的頻率范圍,從而減少尖峰能量。

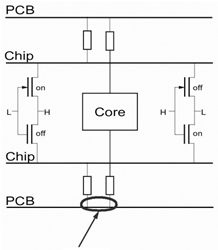

3、多種隔離電源

廣泛的使用電源隔離,可以有效減低MCU內核和I/O埠之間的串擾。更有甚者,類比電路、時鐘發生器和外部匯流排界面可單獨供電。為獲得最好的效果,通常在電源和地面處隔離,即便這會引起相當高的內部ESD保護效應。除了保護效果之外,這一措施的運用被引腳的實際可行性限制,特別是在具有少數引腳的小封裝上。另一方面,多引腳的器件可能具有多個電源引腳為同一個系統供電,以減少 PCB和片上供電系統之間的連接阻抗。

當然,在內核和I/O驅動器或其它隔離電路之間也有一些內部控制信號。雖然是隔離供電,但為了保持兩種供應系統具有相同的地電勢,PCB的地之間必須通過低阻抗連接。

?

圖6∶關注地面阻抗

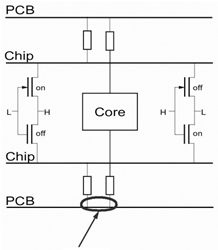

4、鄰近的電源和地引腳

大多數MCU封裝都有相鄰電源引腳,這些引腳使PCB設計者能更輕易地減少MCU與退耦電容之間的電流環路面積。當然,要最小化環路面積,每相鄰電源引腳對之間要有一個電容,不僅降低了環路面積,也減少了退耦電容的連接阻抗。

在PCB設計時需要引起注意的是,盡可能地靠近供應引腳放置退耦電容,把每條線當成具有阻抗的導線考慮,尤其是去耦電路和供電系統板之間的連接應慎重考慮。

?

圖7∶鄰近的電源引腳

四、總結

根據以上介紹,現將MCU使用中,一些有效的PCB設計方法介紹如下∶

(1)直接半導體遠場輻射可以忽略,因為片內結構很小以至不能形成有效的天線。MCU產生電流和電壓影響PCB布局和電纜連接,而PCB和導線形成的天線結構影響微控制器EMC特性,因此遠場輻射主要是電流,電壓和阻抗的問題。

(2) 頻率提高時,任何導線都會有電感,形成明顯的阻抗,尤其是在濾波電路中任何線路的阻抗是必須考慮的。

(3) 高頻窄帶雜訊通常比寬帶雜訊明顯得多。與器件的工作頻率相關的輻射主要是內核的地面電流輻射,振蕩器的噪聲影響是相當低的,外部記憶體接口的最關鍵信號是系統及記憶體的時鐘驅動器

(4) 對于頻繁切換的I/O信號特別是重復信號,必須考慮它對應用系統的輻射。系統時鐘驅動器不應該用于對EME敏感的應用設備中。

電子發燒友App

電子發燒友App

評論