?

目前,大多數(shù)高端嵌入式SoC都屬于異質(zhì)芯片在單純地提高時(shí)鐘速度的方法退出主流之后,保持這種單線程的編程抽象,迫使通用的單處理器設(shè)計(jì)工程師采用雙處理器或四處理器的一致性系統(tǒng)(coherent system)。具有豐富軟件的高性能嵌入式系統(tǒng)也是如此,只是情況稍有不同。

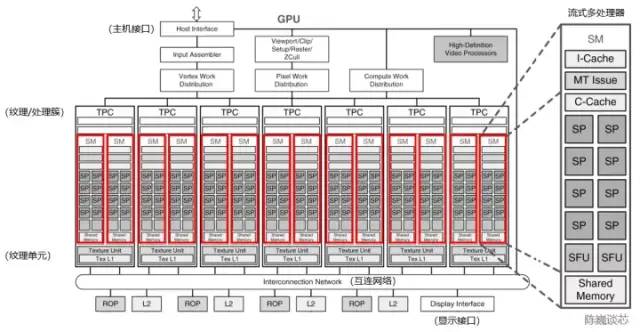

這些SoC中的處理器通過非一致性(noncoherent)共享內(nèi)存,以某種形式的消息傳遞進(jìn)行通訊。在第三代蜂窩電話中,通過雙端口SRAM和中斷進(jìn)行通訊的經(jīng)典RISC/DSP組合,就是這些簡單機(jī)制的一個(gè)很好例子。 未來的高性能SoC將是處理器的分層和異質(zhì)系統(tǒng),即在層次結(jié)構(gòu)中嵌入由同質(zhì)多處理器組成的一致性處理器集群。這種轉(zhuǎn)變已經(jīng)出現(xiàn)在一個(gè)特定的高性能嵌入式市場中,即以一致性網(wǎng)絡(luò)多處理器實(shí)現(xiàn)的聯(lián)網(wǎng)市場。

目前,對于未來嵌入式芯片多處理器(CMP)的準(zhǔn)確特性仍存在爭議。CMP是屬于異質(zhì)型,還是用同質(zhì)處理器以分層方式實(shí)現(xiàn)的異質(zhì)型還不明確。但對于許多CMP而言,使共享內(nèi)存保持一致性至關(guān)重要。

定義和基本概念

對于一個(gè)帶有緩存的多內(nèi)核共享內(nèi)存系統(tǒng)而言,如果由任何處理器發(fā)布的任何“載入”操作所返回的值總是在該內(nèi)存位置最新“存儲(chǔ)”的值,則認(rèn)為該系統(tǒng)是緩存一致的。為了明確術(shù)語“最新存儲(chǔ) (latest Store) ”的定義,我們需要探討一下內(nèi)存模型。

借助于順序一致性(SC)模型這個(gè)常用的內(nèi)存模型進(jìn)行闡述。在SC系統(tǒng)中,可以根據(jù)一個(gè)并行程序的任何一次執(zhí)行的結(jié)果,對在一個(gè)位置完成的所有操作(主要是“載入”和“存儲(chǔ)”)建立全局串行順序。因此,“一致性”意味著:(1)每個(gè)處理器發(fā)出的“載入”和“存儲(chǔ)”操作順序,以同樣的方式出現(xiàn)在該系統(tǒng)的全局串行順序中,該處理器按照全局串行順序把這些操作傳給內(nèi)存系統(tǒng);(2)在該系統(tǒng)中,處理器每次所讀取的操作所返回的值,就是在全局串行順序中上次寫入到該位置的值。

因此,術(shù)語“全局串行順序”是由系統(tǒng)實(shí)現(xiàn)的內(nèi)存一致性模型(簡稱內(nèi)存模型)的結(jié)果,在非正式場合中以“強(qiáng)”和“弱”來定義。內(nèi)存模型與單處理器的指令集架構(gòu)(ISA)有關(guān),ISA定義了編譯器和硬件之間的操作約定。

ISA為多處理器系統(tǒng)(一般稱為多線程系統(tǒng))定義了程序員和內(nèi)存系統(tǒng)之間的操作約定。因此,Java等多線程語言也明確給出了內(nèi)存模型。在本文,大多數(shù)的“多處理”都可以用“多線程”代替。

順序一致性(SC)、總體存儲(chǔ)順序(TSO)和處理器一致性(PC)是一些常用的機(jī)器級內(nèi)存模型(從強(qiáng)到弱)。模型更強(qiáng),意味著在并行內(nèi)存系統(tǒng)的實(shí)現(xiàn)器中加入了更多約束,從而簡化了由并行中間件或系統(tǒng)庫寫入器執(zhí)行的任務(wù)。

但從單處理器的角度來看,SC卻是內(nèi)存一致性最弱的方式,因?yàn)樗惶峁┖侠淼膬?nèi)存系統(tǒng)所必需的約束,而不再對內(nèi)存操作進(jìn)行限制。簡言之,強(qiáng)的內(nèi)存模型確保并行內(nèi)存系統(tǒng)在“讀出最新存儲(chǔ)操作返回的值”的約束基礎(chǔ)上,還提供其它約束,從而更有利于程序員編程。這些附加的約束通常可用于在線程或處理器之間形成高效的同步機(jī)制。

為實(shí)現(xiàn)一致性,系統(tǒng)必須具備幾個(gè)基本特點(diǎn)。首先,在系統(tǒng)中的某一點(diǎn)處,向某個(gè)特定的內(nèi)存位置寫入信息的操作必須是串行化的。請注意,串行化是一個(gè)邏輯概念。對于一些探索性的高性能實(shí)現(xiàn),串行化只是對于在提交(commit)階段應(yīng)如何返回事務(wù)給出了一個(gè)指導(dǎo)性方針,它類似于“無序”處理器,這種處理器保持一個(gè)臨時(shí)狀態(tài)和一個(gè)由提交點(diǎn)(commit point)分隔的“架構(gòu)狀態(tài)”。

一致性系統(tǒng)的另一個(gè)特點(diǎn)是“寫入”傳播,它表示“寫入”操作需要最終傳播到需要這個(gè)新值的所有代理程序(agent)。第三個(gè)重要特點(diǎn)是“寫入”原子性,它是內(nèi)存模型而不是一致性的結(jié)果,它表示在所有處理器被串行化后,需要將寫入操作全部傳播至系統(tǒng)中的所有處理器。

這里將只討論一致性協(xié)議的常見分類方法。這種分類方式基于系統(tǒng)中緩存的穩(wěn)定狀態(tài),常見的狀態(tài)被稱為“MOESI”,即修改、自有、互斥且干凈、共享且干凈,以及無效。這些術(shù)語的意義是自我解釋的,詳細(xì)解釋很容易在教科書中找到。

基于狀態(tài)的協(xié)議分類主要區(qū)分協(xié)議是基于“更新”還是基于“無效(invalidate)”。在基于“無效”的一致性協(xié)議中,系統(tǒng)中的一條緩存線僅有一個(gè)所有者,而在基于更新的系統(tǒng)中,所有緩存線的副本都是根據(jù)“寫入”操作來更新的。

串行化

許多較老的對稱式多處理(SMP或非CMP)系統(tǒng),以總線廣播方式將事務(wù)廣播給系統(tǒng)中所有的代理程序。因此,這些代理程序可以“窺探”它們的狀態(tài),然后采取適當(dāng)?shù)膭?dòng)作使數(shù)據(jù)項(xiàng)副本無效并對其進(jìn)行更新。這種方式在一個(gè)事務(wù)的不同階段之間的重疊是最小的,并被限制為有序串行化(管道化)。

由于受到帶寬可擴(kuò)展性、速度和總線可擴(kuò)展性的限制,這些嚴(yán)格的監(jiān)聽總線機(jī)制逐漸演變成一些新的一致性機(jī)制。高端系統(tǒng)(仍與嵌入式CMP有關(guān),盡管原因并不相同)常采用基于目錄的機(jī)制。當(dāng)已經(jīng)存在低級別的多處理時(shí),通常優(yōu)先采納監(jiān)聽“虛擬總線”機(jī)制。

監(jiān)聽虛擬總線串行化使用樹型開關(guān)或?qū)哟苇h(huán)等專用的更高性能互連架構(gòu),特別是在事務(wù)的請求階段。在這些系統(tǒng)中,互連負(fù)責(zé)建立全局串行順序,同時(shí)從受限的、基于物理總線的互連轉(zhuǎn)換到更高性能(如串行)的點(diǎn)到點(diǎn)信令鏈路。

另一方面,基于目錄的機(jī)制在一個(gè)稱為目錄的新結(jié)構(gòu)上完成串行化。這個(gè)目錄通常駐留在內(nèi)存模塊中,用來存儲(chǔ)系統(tǒng)中各種緩存行的狀態(tài)。一般而言,這些系統(tǒng)與監(jiān)聽總線機(jī)制(虛擬或其它形式)相比,其在串行化和有序化方面對網(wǎng)絡(luò)的依賴程度大大降低。由于目錄機(jī)制不廣播消息的數(shù)目,所以它們可用在非常大的系統(tǒng)中。

影響片上嵌入式多處理器一致性的另一個(gè)趨勢是,為降低復(fù)雜性,帶有多個(gè)處理器的下一代SoC將把通訊與計(jì)算分開。這種趨勢已經(jīng)促使了基于網(wǎng)絡(luò)級芯片(NoC)的設(shè)計(jì)方法學(xué)的誕生,以及從電路交換NoC向分組交換NoC的轉(zhuǎn)移。任何一種片上嵌入式多處理器的一致性機(jī)制都需要關(guān)注深亞微米SoC中的這個(gè)重要變化,并在分組交換網(wǎng)絡(luò)底層上對一致性協(xié)議進(jìn)行分層。

嵌入式SoC帶來了成本、功耗、實(shí)時(shí)操作、知識產(chǎn)權(quán)(IP)所有權(quán)以及異質(zhì)處理器等一系列問題,因此,選擇嵌入式SoC的一致性機(jī)制與通用SoC有所不同。系統(tǒng)功耗低,系統(tǒng)成本就低,而系統(tǒng)成本是SoC的一個(gè)敏感因素。此外,如果SoC用于移動(dòng)應(yīng)用,低功耗要求的確是必需的。

正像緩存進(jìn)入DSP領(lǐng)域需要一個(gè)過程一樣(周期準(zhǔn)確的處理器和系統(tǒng)仿真器是加快這個(gè)轉(zhuǎn)變過程的關(guān)鍵工具),一致性設(shè)計(jì)也是如此。為將軟件移植到實(shí)時(shí)系統(tǒng)中,一致性/SoC設(shè)計(jì)工程師必須確保有周期足夠準(zhǔn)確且快速的仿真器可用于應(yīng)用程序/中間件端口。這個(gè)問題在高性能嵌入式SoC中更加嚴(yán)重,因?yàn)榕c通用多處理器相比,程序員需要更多地接觸硬件。對于通用多處理器,僅是有限的“系統(tǒng)”(中間件、庫和操作系統(tǒng))程序員需要接觸到這個(gè)接口。

IP所有權(quán)是嵌入式SoC的一個(gè)特點(diǎn)。大多數(shù)通用CMP供應(yīng)商的設(shè)計(jì),在內(nèi)存級(與一致性相關(guān)的級別)未采用任何外部IP。但對嵌入式SoC的積分器來說,外部IP的使用非常普遍。甚至連許多高性能嵌入式SoC中的互連(如OCP-IP),也是外部IP供應(yīng)商提供的一個(gè)IP模塊。此外,高性能嵌入式SoC有時(shí)也會(huì)受益于以一致性方式共享相同內(nèi)存的異質(zhì)ISA內(nèi)核,例如一個(gè)RISC內(nèi)核和一個(gè)DSP。

從這些趨勢來看,監(jiān)聽虛擬總線一致性機(jī)制與CMP的相關(guān)性是顯而易見的:有限的可擴(kuò)展性、大量的片上帶寬、點(diǎn)到點(diǎn)信令、更低開銷和更低延遲。但有趣的是,通常認(rèn)為僅適用于大型服務(wù)器級機(jī)器的目錄機(jī)制,經(jīng)過適當(dāng)修改后也適用于嵌入式SoC,這是因?yàn)槟夸洐C(jī)制可以與無序互連、異質(zhì)ISA、低功率單播事務(wù)等協(xié)同工作。

第一代嵌入式CMP或許只能采用監(jiān)聽虛擬總線機(jī)制,但預(yù)計(jì)混合型監(jiān)聽目錄機(jī)制可能成為實(shí)現(xiàn)嵌入式一致性的新趨勢,這是因?yàn)樵O(shè)計(jì)工程師將開始意識到目錄機(jī)制的模塊化所帶來的好處。

死鎖/活鎖

除了選擇串行化方法和一致性協(xié)議的類型之外,在給定的有限資源/緩存情況下,緩存一致性協(xié)議設(shè)計(jì)工程師必須保證該協(xié)議是無死鎖和無活鎖的。對于基于互連的分組交換型一致性協(xié)議,這點(diǎn)尤其重要。

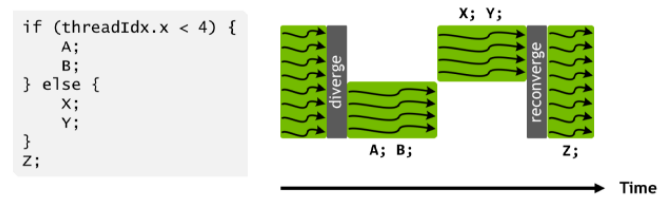

這里存在兩類死鎖,即互連死鎖和協(xié)議死鎖。這兩種死鎖通常都是由于分組交換互連中的緩沖區(qū)限制引起的。在設(shè)計(jì)一致性協(xié)議時(shí),應(yīng)該仔細(xì)考慮協(xié)議死鎖(圖3a)。防止死鎖的常用機(jī)制包括:將事務(wù)的請求路徑與回復(fù)/響應(yīng)路徑分開(圖3b);保證在任何狀態(tài)下緩存或內(nèi)存代理程序都對請求給出響應(yīng)。

如圖3b所示,設(shè)計(jì)工程師通常使用虛擬通道來完成上述第一個(gè)機(jī)制。在任何虛擬通道中流動(dòng)的事務(wù)都遵循先進(jìn)先出(FIFO)順序,而且信息流中的阻塞事件可引起一個(gè)能一直追溯到阻塞根源的背壓(backpressure)流控。因此,只要(事務(wù))接收器(sink)在向前移動(dòng)(forward progress),系統(tǒng)就不會(huì)阻塞。

如果在向前移動(dòng)的過程中出現(xiàn)停頓,分布式系統(tǒng)將出現(xiàn)活鎖現(xiàn)象。在處理器上,這將在沒有向前發(fā)展的“載入/存儲(chǔ)”的程序計(jì)數(shù)器中得到反映。當(dāng)多個(gè)緩存試圖獲得緩存線的所有權(quán)失敗時(shí),這種情況常常發(fā)生。如果在該系統(tǒng)中適當(dāng)?shù)亟⒁粋€(gè)全局串行順序,則每個(gè)代理程序就可以按照這個(gè)順序來處理請求。必須按照公平方式來建立全局串行順序,并且公平地將各種資源(端口、總線、緩沖器)分配給多線程/多處理器。

另一個(gè)與防止活鎖有關(guān)的問題是流量控制。系統(tǒng)的流量控制將限制資源的分配。以ad-hoc方式實(shí)現(xiàn)的流量控制可能導(dǎo)致活鎖,而常見的一種情況就是在響應(yīng)請求的同時(shí),過度地使用重試或否定應(yīng)答(NACK)。

其它設(shè)計(jì)考慮

除了死鎖和活鎖之外,設(shè)計(jì)工程師還應(yīng)該考慮以下的問題:

緩存層次和DMA:當(dāng)事務(wù)穿過緩存層次時(shí)將產(chǎn)生死鎖問題。通常,我們可以采納在更廣泛的協(xié)議中使用的相同機(jī)制,以便在單獨(dú)的(虛擬或真實(shí))通道/FIFO中保留請求和回復(fù)。

另一個(gè)問題是確定增強(qiáng)一致性的緩存級別(L1緩存、L2緩存或L3緩存),以及I/O應(yīng)在哪個(gè)位置上從一致性域進(jìn)入和提取緩存線。通常情況下,包含(inclusion)問題的相關(guān)解決機(jī)在很大程度上依賴于具體的應(yīng)用或系統(tǒng)。通過在一致性系統(tǒng)的事務(wù)集合包含線索(hint),可一致性系統(tǒng)中使用線索來進(jìn)行預(yù)取和數(shù)據(jù)放置。一個(gè)顯而易見的例子就是路由。在路由系統(tǒng)中,需要把外來IP包的頭文件與一個(gè)表進(jìn)行匹配,以該IP包的目標(biāo)緩沖器/接口。通過利用線索對事務(wù)進(jìn)行分類(如讀出/寫入、命中/不命中策略),可以將這些頭文件放在靠近較低緩存級別的位置。

同步和屏障(barrier)操作:許多ISA提供各種必須映射到一致性系統(tǒng)的原子語義(atomic primitive)。較弱的內(nèi)存系統(tǒng)要求一種被稱為屏障的安全網(wǎng)落,它可以在發(fā)送敏感代碼序列期間,強(qiáng)迫發(fā)生某種行為(通常在處理器或線程發(fā)出的“存儲(chǔ)”和“載入”操作之間)。這種屏障一般通過插入ISA支持的專用屏障指令來實(shí)現(xiàn)。一致性系統(tǒng)可能需要通過動(dòng)態(tài)地停滯某些事務(wù)來對這些操作作出響應(yīng),以支持這些行為。

電子發(fā)燒友App

電子發(fā)燒友App

評論