引言

PDA即Personal Digital Assitant(個人數字助理)的縮寫,是近年來繼尋呼機和移動電話之后,在國內市場迅速崛起的便攜式電子產品。本PDA系統除了具備傳統PDA的個人名片管理、辭典檢索、信息速記功能外,更重要的是提供交通領域的民航各種航班查詢和全國鐵路列車的刻表查詢,通過傳呼系統及時廣播鐵路和民航行業應用方面的如航班晚點、車次晚點、剩余票額等相關行業信息。 PDA系統屬于便攜式電子產品。這類產品, 性能指標日益向實用化、方便化發展。產品不僅要求功能完備,用戶界面友好,操作方便簡潔,而且要求產品壽命長,功耗低。 產品低功耗設計一般從硬件和軟件兩個角度來考慮。本文重點闡述該PDA系統所采用的降低系統功耗的各種措施。

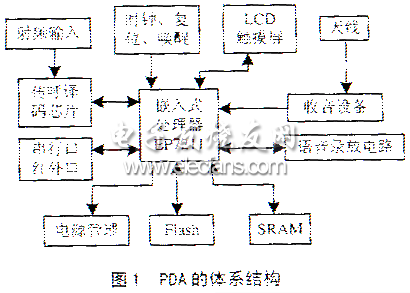

1 鐵路交通信息系統PDA的體系結構

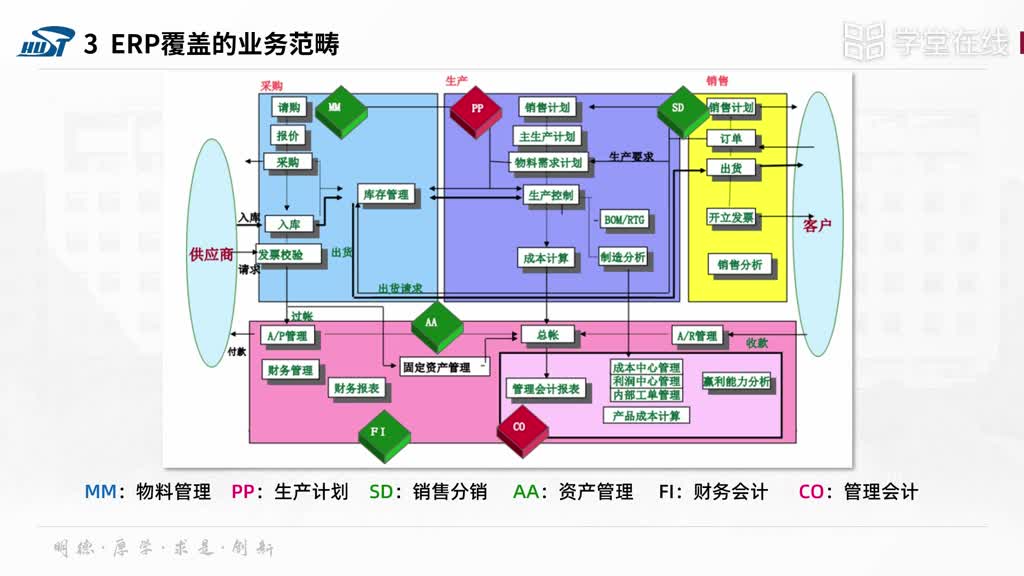

在分析本PDA系統的功能性和非功能需求,充分了解市場硬件行性的基礎上,設計了本PDA系統,其硬件體系結構框圖如圖1所示。

?

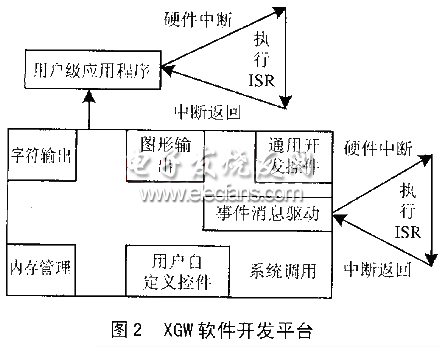

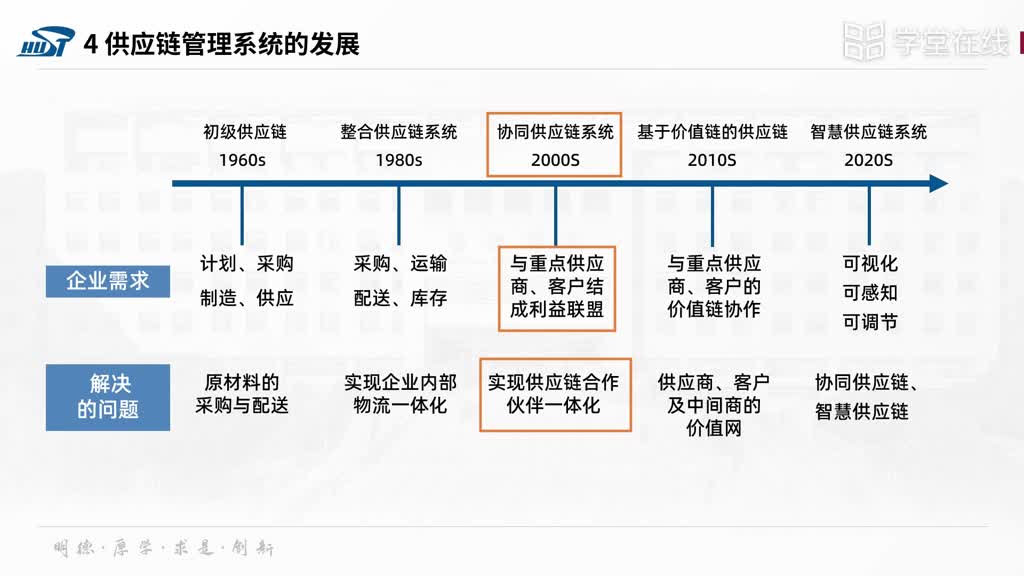

嵌入式處理器EP7211(核心模塊)進行數據處理,傳呼譯碼芯片接收傳呼信息并根據傳呼協議自動譯碼;LCD提供數據顯示輸出,觸摸屏提供用戶輸入接口;Flash用來存儲可執行應用程序和數據;SRAM為程序運行提供內存空間;語音錄放電路完成快速語音記憶功能;串口和紅外口完成相關的數據通信工作;電源電路為嵌入式處理器和各外圍設備提供所需要的工作電壓。 嵌入式處理器EP7211是Cirrus Logic公司專門為低成本、超低功耗的嵌入式應用設計。它包含基于RISC體系結構的ARM7TDMI處理器內核和豐富的外圍接口,如CODEC音頻接口、SPI串行A/D接口、單色LCD接口、RAM接口、串行紅外接口、PWM接口、實時時鐘RTC以及電源檢測接口等。這些豐富的外圍接口,不僅降低了系統的設計難度,同時也提高了系統工作的可靠性。EP7211的內核電路工作在2.5V,而外圍電路工作在3.3V。它可根據具體情況對內核的時鐘進行動態編程控制,可工作在18MHz、36MHz、49MHz和74MHz。另外,EP7211還有三種基本的工作狀態:正常操作(operating)、空閑(idle)和等待(standby)。在等待模式時,主時鐘被關斷,整個CPU及相關外圍(除中斷和RTC)關斷,但可通過觸摸屏中斷、傳呼中斷或復位按鈕來喚醒。 系統軟件開發平臺采用了我們自主開發研制的、專門面向嵌入式應用系統開發的XGW平臺。XGW開發平臺措鑒Windows消息驅動機制,是用C語言開發實現的;它功能強大,模塊化設計,擴展性強,產品升級容易,而且開發人員較為熟悉,開發成本低,其總體框架如圖2所示。

?

圖2全面反應了XGW軟件開發平臺的體系結構,包括事件消息驅動機制(XGW軟件開發平臺中的消息分為鼠標消息、鍵盤消息和定時器消息等三類)、內存管理、字符和圖形顯示輸出、圖形組件庫等。圖形組件庫中的編輯框、列表框、按鈕、進度條等圖形控件為用戶應用程序開發提供了應用編程接口API。不過,XGW平臺對于系統硬件的中斷響應沒有提供統一的入口和出口,需要開發人員單獨處理。

2 硬件低功耗

硬件低功耗主要從芯片制造工藝流程和硬件體系架構的角度出發,基本原理是盡量選用能夠滿足功能要求的功耗低的芯片。不過,芯片自身的功耗參數由制造廠商來決定,此處主要闡述CMOS芯片動態功耗以及動態電源管理兩個方面。 (1)CMOS芯片動態功耗 隨著半導體制造技術的發展,數字電路從TTL工藝轉向CMOS工藝。TTL工藝為電流注入型電路,靜態和動態電流消耗接近。CMOS工藝是壓控型的,理想情況下("0"、"1"的恒定狀態)靜態電流為0,實際情況下也是很小的。動態("0"、"1"間的跳變狀態)電流消耗占絕對主導地位。CMOS動態功耗計算公式為

.jpg)

?

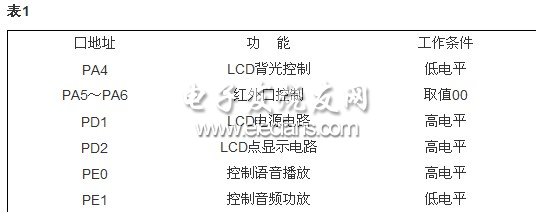

式中: Pd--CMOS芯片動態功耗; Ce--CMOS芯片等效電容; V--CMOS芯片工作電壓; f--CMOS芯片工作頻率或工作狀態的切換頻率。 從式(1)及各參數含義看,CMOS芯片動態功耗的數值正比于工作電壓的平方,同時正比于工作頻率。在滿足系統功能需求的條件下, 降低芯片工作電壓和工作頻率,都可以極大減少芯片的動態功耗。以處理器工作頻率為例,如果工作頻率降低一半,則該芯片動態功耗幾乎也隨之減半。在本PDA系統中,盡管ARM7處理器提供了18MHz、;36MHz、49MHz和74MHz四種工作頻率,但我們采用2.5V為低壓供電,18MHz工作頻率。這些參數在降低系統功耗的同時,也滿足了系統性能的需求。 (2)動態電源管理 動態電源管理技術是指有選擇地將閑置的系統模塊置于低能狀態。一個較為復雜的嵌入式系統,除了處理器外還有很多外設電路模塊,它們協調工作,共同完成系統功能。 但在分析完成系統功能的過程中可以看出,并不是所有模塊在任何時間都處在工作狀態。除了嵌入式處理器外,絕大多數外設模塊都是在執行某項具體功能的時候(它自己的有效操作期間)才需要供電。如音頻模塊,有語音輸入或者輸出時才需要工作;在進行串口通信時,串口芯片需要處在工作狀態;而在更多的時間里,這些芯片都是不需要工作的。 為了系統功耗最小,動態電源管理的原則是系統完成某項功能,只有參與這項功能的模塊才供電,其它模塊設置在電源切斷狀態。在電路設計時,需要充分考慮到這個問題,盡可能為各外設模塊提供切換供電機制的引腳控制信號,而且允許通過軟件編程的措施來完成其電路開關的切換工作。 本PDA系統中,除了嵌入式處理器外,還有異步串口、語音編譯碼芯片、音頻功放、傳呼、LCD、收音機等外部設備。傳呼的接收具有隨機性,需要一直處在工作狀態。串口、語音芯片、功放電路、LCD等可以通過一定口地址的設置來控制電源開關,使之在工作的時候提供電壓,在不工作的時候切斷電源。 各外設模塊電源口地址配置如表1所列。

?

表1 口地址功 能工作條件 PA4 LCD背光控制低電平 PA5~PA6 紅外口控制取值00 PD1 LCD電源電路高電平 PD2 LCD點顯示電路高電平 PE0 控制語音播放高電平 PE1 控制音頻功放低電平

3 軟件低功耗

嵌入式系統開發中除了硬件低功耗措施外,也可以從軟件方面來設計。嵌入式系統軟件低功耗措施一般涉及到處理器工作狀態間的切換、應用模塊軟件算法的選擇和系統整體的數據調度三個方面。

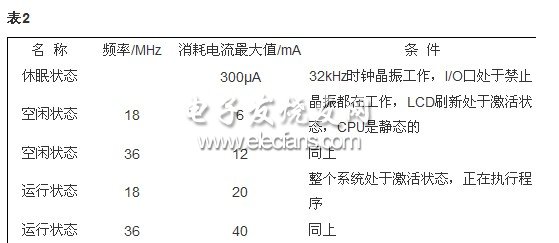

(1)處理器工作狀態 便攜式系統工作過程中,處理器并不是任何時候都一直忙于運行,尤其是PDA來產品。如今的嵌入式處理器(包括EP7211)一般都為應用開發提供了三種工作狀態:運行、空閑和休眠。大量的實際使用表明,更多情況下,大部分時間里系統是處在休眠狀態的,一旦獲得工作信號,會迅速切換到工作狀態。當系統在工作狀態下一定時間內沒有獲得下一次需要處理的信號時,則應該自動切空閑或者休眠狀態。因為在不同的工作狀態,處理器內部工作電路有所變化,功耗大小差別較大。 本PDA系統采用的ARM處理器,在不同工作條件和狀態下的功耗哪表2所列。

?

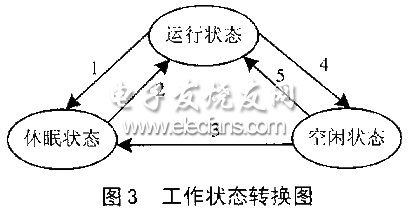

表2 名 稱頻率/MHz 消耗電流最大值/mA 條 件 休眠狀態 300μA 32kHz時鐘晶振工作,I/O口處于禁止 空閑狀態 18 6 晶振都在工作,LCD刷新處于激活狀態,CPU是靜態的 空閑狀態 36 12 同上 運行狀態 18 20 整個系統處于激活狀態,正在執行程序 運行狀態 36 40 同上注:直流供電電壓2.5V 從表2中明顯看出,處理器不同條件和狀態下的功耗參數大小的差別。在18MHz頻率下,運行功耗(20mA)是空閑功耗(6mA)的近4倍,空閑功耗又是休眠功耗300μA的20倍。我們的目的是在不影響系統正常運行的過程中,盡最大可能使系統處在空閑休眠狀態來降低系統功耗;因此,我們應該通過預測系統執行過程的措施來切換處理器的工作狀態。分析式(1)可知,我們又不能頻繁過快地進行處理器狀態切換,中間要留有一定的穩定時間間隔。 XGW軟件開發平臺采用事件消息驅動機制。消息采用查詢方式,能夠實時響應外部中斷。在消息循環過程中,系統需要查詢消息隊列:當有消息出隊時,處理器在運行狀態處理這個消息所對應的事件;如果一這時間間隔(如2s)消息隊列一直是空,系統預測在最近相當長的時間內不會有事件產生,軟件編程措施把處理器從運行狀態切到空閑狀態;如果系統在更長的時間內(如20s)沒有事件產生,則系統預測用戶需要自動軟關機,此時處理器進入休眠狀態。在休眠狀態下,處理器能夠響應實時時鐘匹配中斷、傳呼接收中斷以及復位按鍵;一旦系統捕獲到這類信號,則迅速轉入到正常工作狀態。處理器在運行狀態和空閑狀態間的切換間隔是必需的,如果切換速度過快,并不能達到降低系統功耗的目的。 為了縮短處理器從空閑或者運行狀態切換到休眠狀態的時間,系統同時提供了用戶手動軟關機措施,即通過觸筆直接點擊屏幕某一指定區域來實現。 本PDA系統中,ARM7處理器三種工作狀態的轉換如圖3所示。

?

圖3中各數字含義如表3所列。

.jpg)

?

表3 序 號狀態轉換條件 1、3 系統20s內一直不能捕捉到消息或者人為點擊屏幕某一指定區域 2 實時時鐘匹配中斷、傳呼中斷、按鍵喚醒 4 運行狀態下系統2s內一直不能捕捉到消息 5 產生中斷信號、捕捉到消息事件。

(2)軟件算法的選擇 在應用程序編程實現過程中,求解同一個問題,可以有許多不同的算法。評價一個算法好壞的常用參數是算法時間復雜度、算法空間復雜度和算法的易理解編碼和調試性。算法時間復雜度定義為算法的時間耗費,即算法所求解問題規模(求解問題的輸入量)n的函數。時間復雜度一般用O(n)來表示,當n達到一定規模時,時間復雜度越小,執行效率越高,招待時間越短,系統功耗越低。算法空間復雜度定義為該算法所耗費的存儲空間,它也是問題規模n的函數。 我們總是希望選用一個所占存儲空間小、運行時間短、其它性能也好的算法。然而實際上很難做到十全十美,原因是上述要求有時相互抵觸, 如節約算法執行時間需要以犧牲一定的存儲空間為代價,反之亦然。因此,我們只能根據具體情況有所側重。在本PDA系統中具體硬件配置時,CPU工作頻率不高,存儲空間運行不大;但應用程序數據量大,而且某些應用程序如辭典互譯、時刻表檢索時數據運算量也大。 如要在本PDA系統中實現英漢辭典互譯,首先會想到采用順序檢索法。這種算法對用戶輸入詞匯排列順序沒有要求,編程實現和理解起來都比較簡單,其算法時間復雜度為O(n)=n。當n值較小時,這是可以允許的;但是當系統詞匯量近10 000個時,算法檢索效率不高,表現為當詞語位置偏后時系統檢索延遲過大。為了提高檢索效率,滿足一定的系統反應實時性要求,我們采用了有序表二分搜索算法,其算法時間復雜度O(n)=log2n。假設n=16 384=2 14已經超出系統的數據規模(10 000詞左右)。二分檢索所需要的最壞檢索次數是14次;但是對于順序檢索而言,在最壞查找的情況下,檢索次數是16 384次,故效率提高了16 284/14=1170倍。這個數目是相當可觀的,而且,即使系統數據規模進一步擴大,二分檢索表現出來的所增加的檢索次數也是很小的。辭典互譯實現二分檢索所要做的附加工作,就是將原來無序的辭典數據文件轉換成有序的辭典數據文件。不過,這個轉換工作可以在PC機上完成從而減輕本嵌入式系統的負荷。辭典數據排序和檢索過程中英漢辭典依據ASCII碼進行,漢英辭典根據漢字的區位碼進行。本PDA系統的民航時刻表、鐵路時刻表等應用模塊,也都涉及到了算法選擇問題。

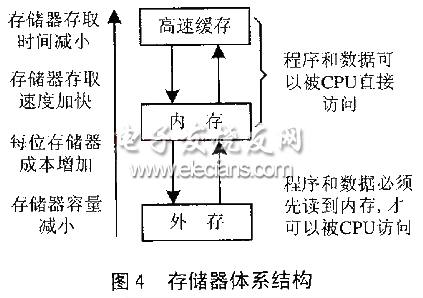

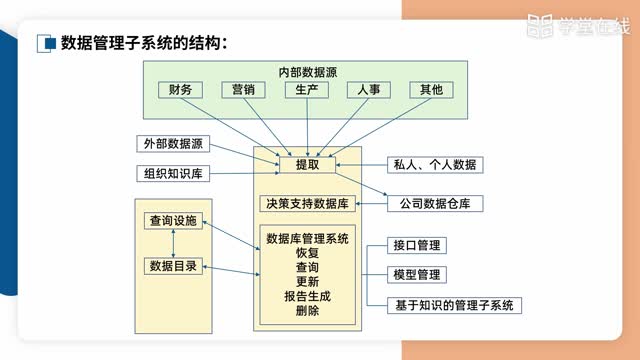

(3)數據調度 在許多應用程序中,存儲器訪問是功耗的主要部分。有資料表明,內存傳輸是迄今為止CPU完成的操作中代價最高的:一次內存傳輸消耗的能量是一次加法運算的33倍多。優化能量消耗的最大收益之一,來源于合理組織內存中的數據和指令:一般措施是盡量做到數據的寄存器訪問和緩存訪問。 隨著存儲技術理論的發展和工藝水平的提高,現在存儲器體系結構一般都是三級,而且支持虛擬存儲技術,如圖4所示。

?

處理器進行數據訪問時,離CPU越近的地方,數據存取速度越快,功耗越低。本PDA系統中,由于Flash存儲器(作為數據存儲器件)寫操作的特殊性(以扇區大小為單位、執行時間長、執行功耗大),要求盡量少地進行。基于這種策略,本PDA系統在數據安排方面采取了以下一些優化措施: ①LCD幀緩存的安排。EP7211內置38 400字節大小的RAM空間,LCD分辨率是320%26;#215;240,每像素4級灰度用2比特位表示,故顯存大小為320%26;#215;240%26;#215;2/8=19 200字節,被安排在內置RAM空間的前19 200字節。這樣安排,加快了顯示速度,減少了處理器訪問片外SRAM空間。 ②個人傳呼信息、公共傳呼信息接收頻度大,不需要永久存儲;傳呼接收過程需要開臂兩塊緩沖區,這些空間都被安排在內部RAM后19 200字節,其目的是減少了CPu對片外SRAM的訪問。 ③部分系統信息資源,如字庫信息,在系統啟動后直接從Flash存儲區拷貝到固定位置的SRAM區,這樣字符輸出時直接從內存讀取數據,而不需要訪問Flash。 ④為減少Flash寫操作執行次數,在電話簿、記事本、日程以及系統設定等編輯修改后,首先改動的信息是在內存中直接保存,等到用戶是退出當前整個應用模塊時,才進行一個性Flash寫操作。 ⑤在進行復雜數據查找過程中,為減少數據訪問量,可以通過建立若干級索引表方式加快數據檢索速度。如在辭典文件的詞匯排序過程中,同時建立了每個單詞位置的數據索引,而且作為索引文件定改Flash。在查找過程中,索引項的存在能夠減少檢索次數,從而快速確定單詞起始位置以及整個單詞項目長度,供顯示輸出。不過在增加索引時,也會增加一定的空間復雜度。 另外,系統還可以通過代碼壓縮減少總線上的傳輸量;編譯器優化,消除冗余代碼;消除編程中的遞歸過程調用、減少函數調用的開銷;有效使用寄存器等措施來降低系統功耗。

4 低功耗設計綜合闡述

以上分別從硬件和軟件兩方面闡述了嵌入式系統開發中低功耗設計的一些原則及在本產品中的某些具體體現。本PDA產品除了提代外接電源供電電路,同時還提供內置可充鎳氫雙電池供電系統。設單節電池容量是500mA,則系統待機時間是1000小時/8=125小時,基本上可以滿足實際應用的需要。

電子發燒友App

電子發燒友App

評論