為了提高PCI總線與AVR單片機之間的數據傳輸速度,利用雙口RAM通過共享的方式實現PCI總線與AVR單片機之間的高速數據交換。利用有限狀態機方法將PCI接口芯片局部端邏輯轉換為雙口RAM讀寫控制信號和地址數據信號,并通過仿真工具Modelsim Se對接口電路進行了驗證,得出的仿真波形符合要求;利用乒乓操作方法實現PCI接口芯片和AVR單片機交替讀/寫數據存儲區,有效提高了PCI總線與AVR單片機之間的數據傳輸速度。實踐證明該設計方法是解決高低速設備的傳輸瓶頸問題的有效途徑。

1 PCI9052和IDT7006

1.1 PCI9052簡介

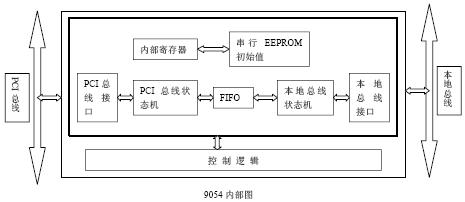

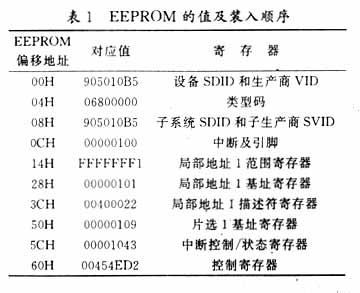

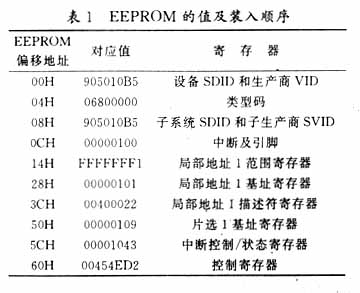

PCI9052是PLX公司為擴展適配板卡推出的低價位PCI總線目標接口芯片,低功耗,符合PCI V2.1規范,它的本地總線(Local Bus)可以通過編程設置為8/16/32位的復用或非復用總線。其主要性能特點如下:

(1)異步操作。PCI9052的Local Bus與PCI總線的時鐘相互獨立運行,兩總線的異步運行方便了高、低速設備的兼容。Local Bus的時鐘頻率范圍為0~40 MHz,TTL電平;PCI的時鐘頻率范圍0~33MHz。

(2)可編程的局部總線配置。PCI9052支持8位、16位或32位Local Bus,它們是復用或非復用。PCI9052有4個字節允許信號(LBE[3:0]#),26條地址線(LA[27:2])和32位、16位、8位數據線(LAD[31:0])。

(3)直接從(目標)數據傳送模式。PCI9052具有雙向FIFO,可用于零等待狀態突發操作,支持從PCI總線到Local Bus的存儲器映射空間的突發傳送和I/O訪問。Local Bus能被設置成突發或持續單周期。

(4)4個局部片選。PCI9052提供4個片選,每個片選的基地址和范圍被E2PROM或主機編程成唯一的。

(5)5個局部地址空間。PCI9052提供5個局部地址空間,每個局部地址空間的基地址和范圍可以被E2PROM或主機編程成惟一的。

1.2 IDT7006簡介

IDT7006是美國IDT公司開發研制的高速16K×8 B雙口靜態RAM。該雙口RAM提供兩個獨立的具有控制、地址和I/O引腳的端口。其主要性能特點如下:可同時訪問雙端口同一存儲器空間;高速存儲訪問,訪問速度最高可達到15 ns;低功耗運行;雙片選,允許不需要外部邏輯的深度擴展;使用級聯和主從選擇引腳可以擴展IDT7006的數據總線寬度到16位或更寬;具有硬件仲裁方式、中斷仲裁方式和信號燈仲裁方式,來防止訪問沖突。

2 PCI9052和IDT7006的時序轉換

為將PCI9052的局部信號邏輯轉換為雙口RAMIDT7006的讀/寫控制信號邏輯,采用有限狀態機的方法來實現它們之間的邏輯轉換。在可編程器件設計中,狀態機的設計方法是應用最廣泛的設計方法之一,它是一種簡單、結構清晰、設計靈活的方法,易于建立、理解和維護,特別應用在具有大量狀態轉移和復雜時序控制的系統中,更顯其優勢。設計中用VerilogHDL描述的狀態機來實現接口的時序轉換。

2.1 硬件連接

硬件上采用可編程邏輯器件MAXⅡ(EPM240)來實現PCI9052和IDT7006的接口電路,PCI9052采取非復用、8 b局部總線寬度和單周期讀/寫方式,信號連接關系如圖1所示。

?

2.2 有限狀態機

PCI9052局部總線有4個基本的狀態:空閑狀態、地址狀態、數據/等待狀態和恢復狀態。一旦局部總線的主設備擁有總線并需要開始一個總線訪問,則進入地址狀態,

有效,此時一個有效的地址出現在地址/數據總線上;數據傳輸是在數據/等待狀態進行的,

或者內部等待產生器用來在此狀態插入等待狀態;

在最后的數據/等待狀態有效,用來申明最后的數據傳輸;在地址/數據復用的模式下,所有數據傳輸完畢后,總線會進入恢復狀態;隨后總線回到空閑狀態,等待下一次的總線訪問。

?

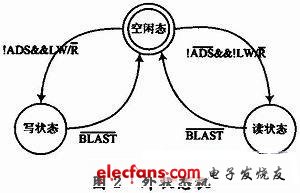

整個狀態機分為外狀態機和內狀態機兩個大的部分,外狀態機識別PCI9052的讀周期和寫周期,并轉移到相應的內部狀態機,然后內部狀態機再進行讀/寫的內部狀態轉移,通過不同的狀態輸出不同的雙口RAM讀/寫控制等信號,達到時序轉換的目的。外狀態機狀態轉移圖如圖2所示。

?

內狀態機中寫狀態機有5個狀態:S0,寫空閑狀態;S1,寫開始;S2,寫等待;S3,單周期寫;S4,寫結束。具體的狀態轉移圖如圖3所示。

?

當系統復位后,狀態機輸出雙口RAM的片選信號

,輸出使能

,狀態機處于空閑狀態。

?

寫操作的狀態機轉移過程是:當狀態機處于空閑狀態時,在每次時鐘的上升沿采樣到

有效和

=1,并且如果雙口RAM的片選信號

有效,狀態機進入寫開始狀態,輸出

和

有效,并將9052的局部有效地址輸出給雙口RAM;當采樣到

有效時,狀態機進入寫等待狀態,輸出

;當采樣到

且BUSYL=1、

時,狀態機進入單周期寫狀態,輸出

,將有效數據輸出到雙口RAM;當采樣到

無效,狀態機進入寫結束狀態,輸出

,

,

;之后如果采樣到

有效就進入下一次的寫操作循環,如果采樣到

無效且

無效,狀態機回到空閑狀態。

?

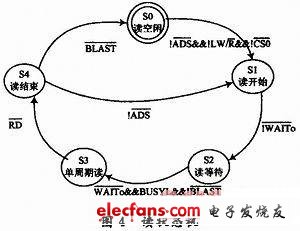

讀狀態機也有5個狀態:S0,讀空閑狀態;S1,讀開始;S2,讀等待;S3,單周期讀;S4,讀結束。具體的狀態轉移圖如圖4所示。

?

讀操作的狀態機轉移過程是:當狀態機處于空閑狀態時,在每次時鐘的上升沿采樣到

有效和

=0,并且雙口RAM的片選信號

有效的話,狀態機進入讀開始狀態,輸出

和

有效,并將9052的局部有效地址輸出給雙口RAM;當采樣到

有效時,狀態機進入讀等待狀態,輸出

;當采樣到

且BUSYL=1,

時,狀態機進入單周期讀狀態,輸出

,將有效數據輸出到PCI9052;當采樣到

無效,狀態機進入讀結束狀態,輸出

,

,

;之后如果采樣到

有效就進入下一次的讀操作循環,如果采樣到無效且無效,狀態機回到空閑狀態。

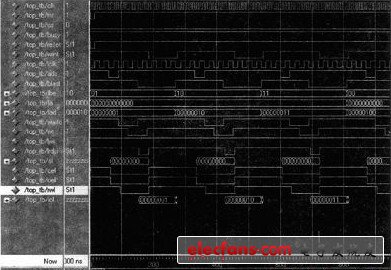

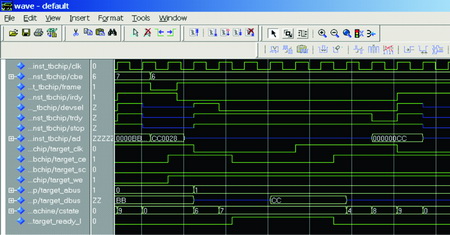

2.3 仿真結果

在ModelsimSE仿真平臺下,實現了PCI9052讀/寫雙口RAM的讀/寫過程,讀操作仿真波形如圖5所示,寫操作仿真波形如圖6所示。從仿真波形可以看出,該代碼可以實現將PCI9052的讀/寫控制信號轉換成雙口RAM的讀/寫控制信號,完成時序的匹配。

?

3 雙口RAM的讀/寫程序

為了達到用低速模塊處理高速數據流的效果,在雙口RAM的程序處理上采用乒乓操作的技巧。乒乓操作的最大特點是通過“輸入數據選擇單元”和“輸出數據選擇單元”按節拍、相互配合的切換,將經過緩沖的數據流沒有停頓地送到“數據流運算處理模塊”進行運算與

處理。把乒乓操作模塊當作一個整體,站在這個模塊的兩端看數據,輸入數據流和輸出數據流都是連續不斷的,沒有任何停頓,因此非常適合對數據流進行流水線式處理。所以乒乓操作常應用于流水線式算法,完成數據的無縫緩沖與處理。

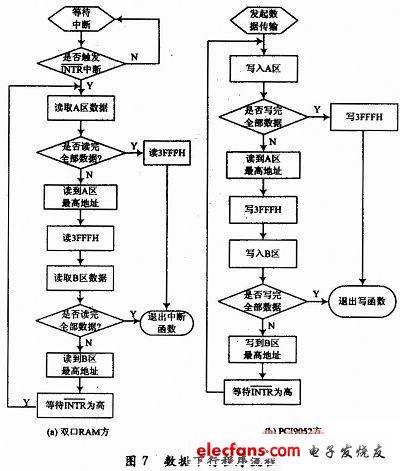

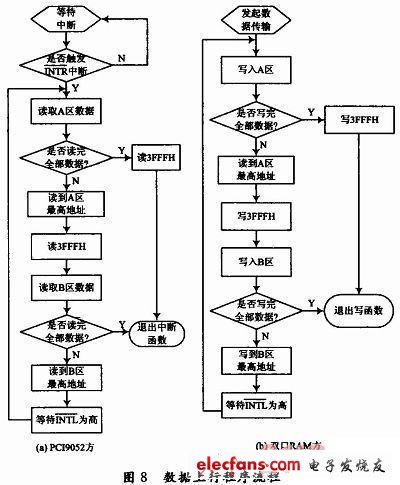

設計中將雙口RAM分為A,B兩個部分,各占8 KB空間。通過9052和AVR交替對兩個存儲器進行讀/寫操作到達交換數據的目的。在雙口RAM的仲裁方式選擇上選取中斷和硬件仲裁結合的方式,中斷仲裁在硬件電路設計上比較簡單,只要將雙口RAM兩側的INT引腳連接到AVR和PCI90 52的中斷引腳上,軟件設計上只要編寫雙口RAM操作程序和中斷服務程序兩部分。具體過程是:

(1)數據下行(PCI9052寫,AVR讀)。在首次發起數據傳輸時,通過握手信號告訴AVR本次數據傳輸共多少個字節。然后發起本次數據傳輸,如果數據傳輸長度小于8 KB,9052向雙口RAM的A區寫入數據,并在數據全部寫完之后對地址3FFFH(右端口信箱)執行一個寫操作,這樣

引腳變為低電平,觸發AVR的一個中斷響應程序,該程序就是雙口RAM讀寫程序中的讀函數,該函數讀取雙口RAM A區中事先約定長度的數據,并在操作的最后對地址3FFFH(右端口信箱)執行一個讀操作以恢復

引腳為高電平,隨后退出中斷響應程序。

?

如果數據傳輸長度大于8 KB,9052寫完A區后,立即對地址3FFFH(右端口信箱)執行一個寫操作,這樣

引腳變為低電平,觸發AVR的中斷響應程序,該程序讀取全部A區的數據,然后對地址3FFFH(右端口信箱)進行一個讀操作,使

恢復為高電平,之后繼續讀取B區的數據;這時9052如果在B區完成了全部數據的寫入,則AVR在B區讀到約定長度的數據后結束本次數據傳輸;如果9052在B區沒有寫完全部數據,則它查詢

是否為高,如果為高則繼續把剩下的數據寫入A區;AVR在讀完全部B區數據后進入暫停狀態,直到接到再次中斷信號繼續讀取A區數據;9052在A區的地址結束時繼續觸發

中斷使得AVR繼續讀取A區數據,A區沒完接著讀B區,這樣循環下去,直到完成約定數據的全部傳輸。具體的流程如圖7所示。

?

?

(2)數據上行(PCI9052讀,AVR寫)。雙口RAM讀/寫程序中的寫函數會將數據寫入雙口RAM的A區,并在最后一步對左端口信箱3FFEH地址執行一個寫操作,引腳變為低電平,該引腳連至PCI9052的局部中斷引腳,通知9052讀取寫入的數據,9052在讀取數據之后會對左端口信箱3FFEH地址執行一個讀操作,這樣引腳恢復為高電平,使之退出中斷響應程序。整個數據傳輸程序流程和下行相似,具體的流程如圖8所示。

?

?

4 結語

實踐證明本文的設計方法是解決高低速設備的傳輸瓶頸問題,提高PCI總線與AVR單片機之間的數據傳輸速度的有效途徑。

電子發燒友App

電子發燒友App

評論