SP430 系列單片機基礎(chǔ)時鐘主要是由低頻晶體振蕩器,高頻晶體振蕩器,數(shù)字控振蕩器(DCO),鎖頻環(huán)(FLL)及 FLL+等模塊構(gòu)成。由于 430 系列單片機中的型號不同而時鐘模塊也將有所不同。雖然不同型號的單片機的時基模塊有所不同,但這些模塊生出來的結(jié)果是相同的。在MSP430F13、 14中是有TX2振蕩器的, 而MSP430F11X,F(xiàn)11中是用LFXT1CLK來代替XT2CLK時鐘信號的。在時鐘模塊中有3個(對于F13,F(xiàn)14)時信號源(或 2個時鐘信號源,對于F11X、F11X1):

1-LFXT1CLK: 低頻/高頻時鐘源。由外接晶體振蕩器,而無需外接兩個振蕩電容器常使用的晶體振蕩器是32768HZ。

2-XT2CLK: 高頻時鐘源。由外接晶體振蕩器。需要外接兩個振蕩電容器,較常的晶體振蕩器是 8MHZ。

3-DCOCLK: 數(shù)字可控制的 RC 振蕩器。

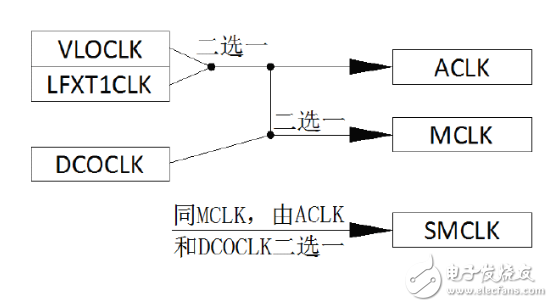

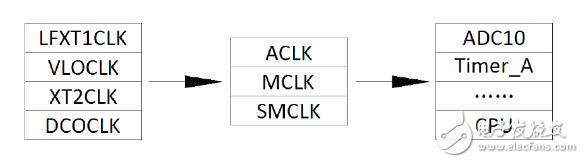

在這三個時鐘源的獨立工作或是在三個時鐘源相互協(xié)調(diào)配合(是可以通過軟件配置的)下為2553系統(tǒng)提供了系統(tǒng)時鐘ACLK、MCLK和SMCLK。ALCK、MCLK、SMCLK是和CPU或者外設(shè)連接起來的,而LFXT1CLK、XT2CLK、DCOCLK、VLOCLK這四個又是和ALCK、MCLK、SMCLK連接起來的,也就是說LFXT1CLK、XT2CLK、DCOCLK、VLOCLK是通過ALCK、MCLK、SMCLK和外設(shè)連接起來的。

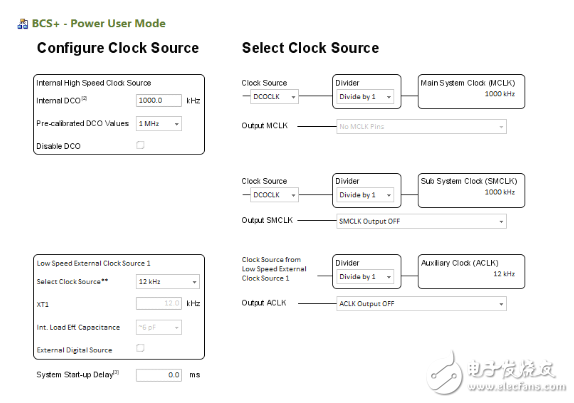

上電后,系統(tǒng)默認使用的主系統(tǒng)時鐘MCLK和子系統(tǒng)時鐘SMCLK是同為DCOCLK產(chǎn)生的1MHz時鐘,而輔助時鐘ACLK則為內(nèi)部VLOCLK產(chǎn)生的12KHz時鐘。G2553上電后時鐘的初始狀態(tài)我們可以用Grace來查看:

可以看出MCLK和SMCLK都是DCOCLK產(chǎn)生的1MHz的時鐘,ACLK則是VLOCLK產(chǎn)生的12KHz的時鐘。

DCO時鐘:

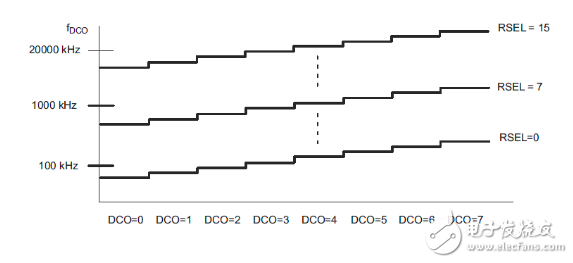

DCO時鐘源產(chǎn)生的頻率可以通過DCOCTL寄存器來設(shè)置寄存器來設(shè)定,通過設(shè)定DCOCTL中的高三位(其名字為DCOx),BCSCTL1基本時鐘控制寄存器低四位(其名字為RSELx)就可以控制DCO振蕩器產(chǎn)生100K~20M不等的時鐘頻率。設(shè)定時應(yīng)盡量居中,以保持穩(wěn)定

1.DCOCTL,DCOControlRegister

DCOxDCO頻率選擇寄存器,通過該位設(shè)置DCO的頻率。

MODx模式選擇位。

2.BCSCTL1,BasicClockSystemControlRegister1

XT2OFFG2553該位無效,詳細請參閱官方技術(shù)文檔。

XTS LFXT1,模式選擇位

0低頻模式。

1高頻模式。

DIVAx

分頻寄存器,分頻后給ACLK提供時鐘00/1。01/2。10/4。11/8。

RSELx DCO頻率選擇寄存器,通過該位設(shè)置DCO頻率。

3.BCSCTL2,BasicClockSystemControlRegister2

SELMx

MCLK時鐘源選擇

00DCOCLK。

01DCOCLK,與00效果一樣。

10G系列單片機該位無效。

11低頻外部時鐘。

DIVMx

時鐘源分頻寄存器,選擇時鐘源后經(jīng)過該位分頻后提供給MCLK

00/1。01/2。10/4。11/8。

SELS

SMCLK時鐘源選擇寄存器

0DCOCLK。

1外部晶振。

DIVSx

時鐘源分頻寄存器,選擇時鐘源后經(jīng)過該位分頻后提供給SMCLK

00/1。01/2。10/4。11/8。

DCOR 該位保留。

4.BCSCTL3,BasicClockSystemControlRegister3

XT2SxG系列單片機該位無效

LFXT1Sx

對G系列單片機,當BCSCTL1寄存器中XTS=0時,該位的設(shè)置才有效

00外部接的是32768HZ的晶振。

01保留位。

10選擇超低頻外部時鐘(VLOCLK)

11數(shù)字外部時鐘源。

XCAPx

振蕩器電容選擇寄存器,當XTS=0時該位有效,假如XTS=1或者LFXT1Sx=11,

XCAPx應(yīng)該設(shè)置為00

00~1pF。01~6pF。10~10pF。11~12.5pF。

XT2OF 對G系列單片機該位無效

LFXT1OF

LGXT1晶體振蕩器故障狀態(tài)寄存器

0沒有故障。

1有故障。

5.IE1,InterruptEnableRegister1中斷使能寄存器

OFIE

晶體振蕩器故障使能寄存器

0禁止中斷

1使能中斷

MSP430G22x0不支持該位。

6.IFG1,InterruptFlagRegister1

OFIFG

晶體振蕩器故障標志寄存器

0沒有發(fā)生中斷。

1有中斷事件發(fā)生。

MSP430G22x0不支持該位。

MSP430 單片機時鐘模塊提供 3個時鐘信號輸出,以供給片內(nèi)各部電路使用。

1-ACLK: 輔助時鐘信號。由圖所示,ACLK 是從 FLXT1CLK 信號由 1/2/4/8 分頻器分頻后所得到的。由BCSCTL1 寄存器設(shè)置DIVA相應(yīng)為來決定分頻因子.ACLK可用于提供CPU外圍功能模塊作時鐘信號使用。

2-MCLK: 主時鐘信號。由圖所示,MCLK 是由 3 個時鐘源所提供的。他們分別是LFXT1CLK,XT2CLK(F13、F14,如果是 F11,F(xiàn)11X1 則由 LFXT1CLK 代替),DCO 時鐘源信號提供.MCLK主要用于MCU和相關(guān)系統(tǒng)模塊作時鐘使用。同樣可設(shè)置相關(guān)寄存器來決定分頻因子及相關(guān)的設(shè)置。

3-SMCLK: 子系統(tǒng)時鐘,SMCLK 是由 2 個時鐘源信號所提供。他們分別是XT2CLK(F13、F14)和DCO,如果是F11、F11X1則由LFXT1CLK代替TX2CLK。同樣可設(shè)置相關(guān)寄存器來決定分頻因子及相關(guān)的設(shè)置。

BCSCTL1 基本時鐘系統(tǒng)控制寄存器1

7 6 5 4 3 2 1 0

XT2OFF TXS DIVA.1 DIVA.0 XT5V Rsel.2 Resl.1 Resl.0

XT2OFF 控制XT2振蕩器的開啟與關(guān)閉。

TX2OFF=0,XT2振蕩器開啟。

TX2OFF=1,TX2振蕩器關(guān)閉(默認為TX2關(guān)閉)

XTS 控制LFXT1 工作模式,選擇需結(jié)合實際晶體振蕩器連接情況。

XTS=0,LFXT1 工作在低頻模式(默認)。

XTS=1,LFXT1 工作在高頻模式(必須連接有高頻相應(yīng)的高頻時鐘源)。

DIVA.0 DIVA.1 控制ACLK分頻。

0 不分頻(默認)

1 2分頻

2 4分頻

3 8分頻

XT5V 此位設(shè)置為0。

Resl1.0,Resl1.1,Resl1.2 三位控制某個內(nèi)部電阻以決定標稱頻率。

Resl=0,選擇最低的標稱頻率。

……。。

Resl=7,選擇最高的標稱頻率。

BSCCTL2 |= DIVM_x (x=0,1,2,3)MCLK分頻(x=0,不分頻;x=1,2分頻;x=2,4分頻;x=3,8分頻)

DIVS_0

BCSCTL2 基本時鐘系統(tǒng)控制寄存器2

7 6 5 4 3 2 1 0

SELM.1 SELM.0 DIVM.1 DIVM.0 SELS DIVS.1 DIVS.0 DCOR

SELM.1 SELM.0 選擇MCLK時鐘源

0 時鐘源為DCOCLK(默認)

1 時鐘源為DCOCLK

2 時鐘源為LFXT1CLK(對于MSP430F11/12X),時鐘源為XT2CLK(對于MSP430F13/14/15/16X);

3 時鐘源為LFTXTICLK。

DIVM.1 DIVM.0 選擇MCLK分頻

0 1分頻(默認)

1 2分頻

2 4 分頻

3 8 分頻

SELS 選擇SMCLK時鐘源

0 時鐘源為DCOCLK(默認)

1 時鐘源為LFXT1CLK(對于MSP430F11/12X),時鐘源為XT2CLK(對于MSP430F13/14/15/16X)。

DIVS.1 DIVS.0 選擇SMCLK分頻。

0 1分頻

1 2分頻

2 4分頻

4 8分頻

DCOR 選擇DCO電阻

0 內(nèi)部電阻

1 外部電阻

PUC信號之后,DCOCLK被自動選擇MCLK時鐘信號,根據(jù)需要,MCLK的時鐘源可以另外設(shè)置為LFXT1或者XT2。設(shè)置順序如下:

[1] 復(fù)位OscOff

[2] 清除OFIFG

[3] 延時等待至少50us

[4] 再次檢查OFIFG,如果仍然置位,則重復(fù)[3]、[4]步驟,直到OFIFG=0為止。

低功耗設(shè)置的技巧問題:

1、LPM4:在振蕩器關(guān)閉模式期間,處理機的所有部件工作停止,此時電流消耗最小。此時只有在系統(tǒng)上電電路檢測到低點電平或任一請求異步響應(yīng)中斷的外部中斷事件時才會從新工作。因此在設(shè)計上應(yīng)含有可能需要用到的外部中斷才采用這種模式。否則發(fā)生不可預(yù)料的結(jié)果。

2、LPM3:在DC發(fā)生器關(guān)閉期間,只有晶振是活動的。但此時設(shè)置的基本時序條件的DC發(fā)生器的DC電流被關(guān)閉。由于此電路的高阻設(shè)計,使功耗被抑制。注:當從DC關(guān)閉到啟動DC0要花一端時間(ns-us)

3、LPM2:在此期間,晶鎮(zhèn)振和DC發(fā)生器是工作的,所以可實現(xiàn)快速啟動。

4、LPM1:在此振蕩器已經(jīng)工作,所以不存在啟動時間延時問題。

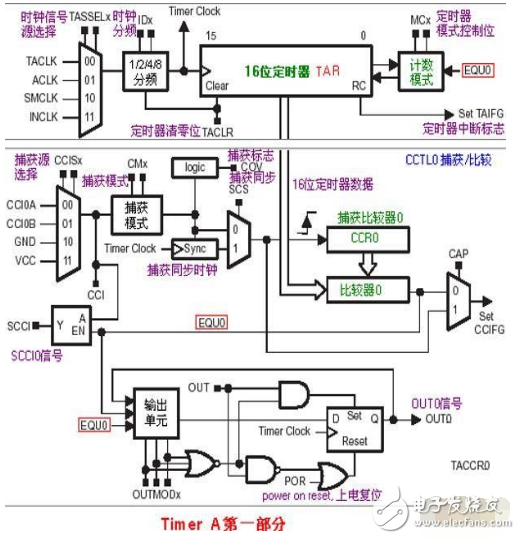

Timer_A的寄存器

寄存器 縮寫 讀定類型 地址 初態(tài)

Timer_A控制寄存器 TACTL R/W 160H POR復(fù)位

Timer_A計數(shù)器 TAR R/W 170H POR復(fù)位

捕撈/比較控制寄存器0 CCTL0 R/W 162H POR復(fù)位

捕撈/比較寄存器0 CCR0 R/W 172H POR復(fù)位

捕撈/比較控制寄存器1 CCTL1 R/W 164H POR復(fù)位

捕撈/比較寄存器1 CCR1 R/W 174H POR復(fù)位

捕撈/比較控制寄存器2 CCTL2 R/W 166H POR復(fù)位

捕撈/比較寄存器2 CCR2 R/W 176H POR復(fù)位

中斷向量寄存器 TAIV R/W 12EH POR復(fù)位

時鐘發(fā)生器的原理說明:

問題的提出:

1、高頻、以便能對系統(tǒng)硬件請求和事件作出快速響應(yīng)

2、低頻率,以便將電流消耗降制至最少

3、穩(wěn)定的頻率,以滿足定時器的應(yīng)用。

4、低 Q值振蕩器,以保證開始或停止操作沒有延時

MSP430 采用了一個折衷的辦法:就是用一個低頻晶鎮(zhèn)振,將其倍頻在高頻的工作頻率上。一般采用這種技術(shù)的實用方法有兩種,一個是說、鎖相環(huán)、 一個是鎖頻環(huán),而鎖相環(huán)采用模擬的控制容易引起“失鎖”和易引起電容量的改變。而TI 采用的是鎖頻環(huán)技術(shù),它采用數(shù)字控制器DCO和頻率積分來產(chǎn) 生高頻的運行時鐘頻率。

TIMER_A有多個捕獲比較模塊,每個模塊都有自己的控制寄存器CCTLx

CAPTMOD1-0 選擇捕獲模式

00 禁止捕獲模式

01 上升沿捕獲

10 下降沿捕獲

11 上升沿與下降沿都捕獲

CCISI1-0 在捕獲模式中用來定提供捕獲事件的輸入端

00 選擇CCIxA

01 選擇CCIxB

10 選擇GND

11 選擇VCC

SCS 選擇捕獲信號與定時器時鐘同步、異步關(guān)系

0 異步捕獲

1 同步捕獲

異步捕獲模式允許在請求時立即將CCIFG置位和捕獲定時器值,適用于捕獲信號的周期遠大于定時器時鐘周期的情況。但是,如果定時器時鐘和捕獲信號發(fā)生時間競爭,則捕獲寄存器的值可能出錯。

在實際中經(jīng)常使用同步捕獲模式,而且捕獲總是有效的。

SSCIx 比較相等信號EQUx將選擇中的捕獲、比較輸入信號CCIx(CCIxA,CCIxB,Vcc和GND)進行鎖存,然后可由SCCIx讀出。

CAP 選擇捕獲模式還是比較模式。

0 比較模式

1 捕獲模式

注意:同時捕獲和捕獲模式選擇

如果通過捕獲比較寄存器CCTLx中的CAP使工作模式從比較模式變?yōu)椴东@模式,那么不應(yīng)同時進行捕獲;否則,在捕獲比較寄存器中的值是不可預(yù)料的,推薦的指令順序為:[1]修改控制寄存器,由比較模式換到捕獲模式。

[2]捕獲

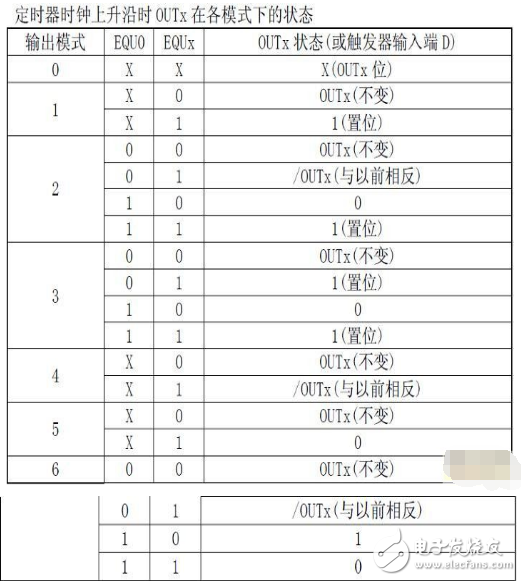

OUTMODx 選擇輸出模式

000 輸出

001 置位

010 PWM翻轉(zhuǎn)/復(fù)位

011 PWM置位/復(fù)位

100 翻轉(zhuǎn)/置位

101 復(fù)位

110 PWM翻轉(zhuǎn)/置位

111 PWM復(fù)位/置位

CCIx 捕獲比較模的輸入信號

捕獲模式:由CCIS0和CCIS1選擇的輸入信號通過該位讀出。

比較模式:CCIx復(fù)位。

OUT 輸出信號

0 輸出低電平

1 輸出高電平

如果OUTMODx選擇輸出模式0(輸出),則該位對應(yīng)于輸入狀態(tài)。

COV 捕獲溢出標志

0 輸出低電平

1 輸出高電平

[1]當CAP=0時,選擇比較模式。捕獲信號發(fā)生復(fù)位,沒有使COV置位的捕獲事件。

[2]當CAP=1時,選擇捕獲模式,如果捕獲寄存器的值被讀出再次發(fā)生捕獲事件,則COV置位。程序可檢測COV來斷定原值讀出前是否又發(fā)生捕獲事件。讀捕獲寄存器時不會使溢出標志復(fù)位,須用軟件復(fù)位。

CCIFGx 捕獲比較中斷標志

捕獲模式:寄存器CCRx捕獲了定時器TAR值時置位。

比較模式:定時器TAR值等于寄存器CCRx值時置位。

#include

void main(void)

{

WDTCTL = WDTPW + WDTHOLD; //停止看門狗定時器

P1DIR |= 0x01; // 設(shè)P1.0為輸出

TACTL = TASSEL_1 + MC_2 + TAIE; // ACLK, 定時器A計數(shù)模式,且開中斷功能

_BIS_SR(LPM3_bits + GIE); //進入LPM3 低功耗模式和開總中斷允許

}

// Timer_A3中斷向量(TAIV)處理程序

#pragma vector=TIMERA1_VECTOR

__interrupt void Timer_A(void)

{

switch( TAIV ) //應(yīng)用switch語句來處理多中斷源的向量

{ //向量列表通過case語句來分多中斷源的入口

case 2: break; // CCR1比較/捕獲寄存器的中斷入口,

//本例子未用到。

case 4: break; // CCR2比較/捕獲寄存器的中斷入口,

電子發(fā)燒友App

電子發(fā)燒友App

評論