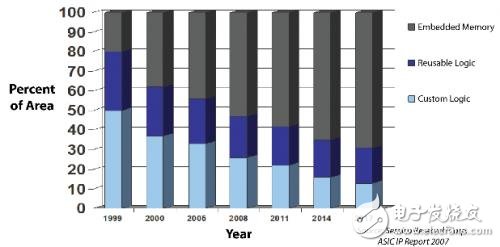

在傳統的大規模ASIC和SoC設計中,芯片的物理空間大致可分為用于新的定制邏輯、用于可復用邏輯(第三方IP或傳統的內部IP)和用于嵌入式存儲三部分。

當各廠商為芯片產品的市場差異化(用于802.11n的無線DSP+RF、藍牙和其他新興無線標準)而繼續開發各自獨有的自定義模塊,第三方IP(USB核、以太網核以及CPU/微控制器核)占用的芯片空間幾乎一成未變時,嵌入式存儲器所占比例卻顯著上升(參見圖1)。

圖1:當前的ASIC和SoC設計中,嵌入式存儲器在總可用芯片空間中所占比例逐漸升高。

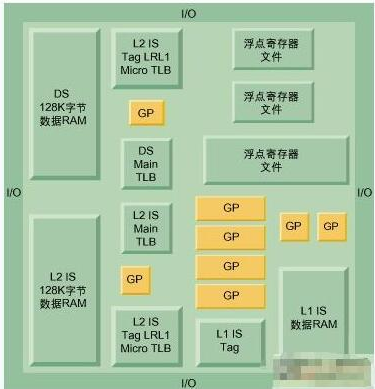

Semico Research 2013年發布的數據顯示,大多數SoC和ASIC設計中,各式嵌入式存儲器占用的芯片空間已超過50%.此外,許多大規模SoC嵌入式存儲器的使用目的和主要性能也各不相同,如圖2所示。

圖2:多核SoC的各種嵌入式存儲器IP.

由于可以根據設計目的,通過采用正確的SoC存儲器類型來優化設計,因此,對于設計師來說,利用各種存儲器IP具有非常重要的意義。設計師可通過恰當分配各種存儲器IP所占比例,實現速度、功耗、空間(密度)以及非易失性等各種性能參數的優化。

嵌入式存儲器的主要設計標準

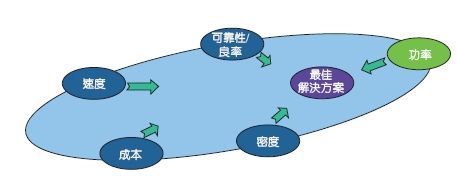

各種應用設計中,最佳存儲器IP的確定主要基于以下5個驅動因素,如圖3所示:

1功率

2速度

3可靠性/良率

4密度

5成本

圖3:確定存儲器IP的主要因素。

通過對上述各性能決定要素進行權衡,可得到最優解決方案。許多情況下,存儲器編譯器可根據輸入存儲器設計生成流程中的各種驅動因素,自動生成性能經過優化的特定存儲器IP.同樣重要的是,存儲器IP的支持性結構應適用可靠的驗證方法,且生成的IP良率最高。最后,為實現產量與質量的最優化,存儲器編譯器還應直接生成GDSII,無需人工干預或調整。其他要素還包括良好的設計余量控制、對自動測試圖形向量生成和內建自測試(BIST)的支持。此外,最好具備通過BIST的單步執行進行硅片調試的功能。

功率

強大的編譯器加之先進的電路設計,可極大地降低動態功耗(CV2f),并可通過利用多芯片組、先進的計時方法、偏置方法、晶體管Leff特征控制以及多重供應電壓(VT)優化等技術最大限度地降低泄露功率。設計師可綜合運用這些存儲器技術,通過電壓和頻率的調整以及多電源域的利用,得到最理想的結果。

速度

為獲得一流的存儲器性能,先進設計技術的充分利用至關重要。設計師可利用存儲器編譯器對速度(比如存取時間或循環時間)、空間、動態功耗以及靜態功耗(泄露功率)等因素進行權衡,得到所需要的最優組合。在通過多種VT技術、多芯片組以及多種存儲單元等的綜合選用,改進存儲器塊的同時,輔以節能設計技術,同樣可以獲得較高速度。

可靠性與良率

晶體管體積和能耗的大幅下降,雖然使噪聲容限明顯減小,但也對極深亞微米芯片的可靠性帶來了影響。因此,為提高良率,改善運行的可靠性,需采用ECC和冗余技術。

由于現在SoC的位元數已十分龐大,因此,嵌入式存儲器便成為了決定SoC良率的最重要因素。在提高存儲器良率方面,由于可減少批量生產時間,控制測試與修復成本,因此專有測試與修復資源具有重要作用。采用一次可編程存儲技術制造的存儲器IP,在芯片制造完成后,發生存儲信息失效時,其內置自修復功能便可對存儲器陣列進行修復。理想情況下,為在生產測試過程中,快速進行修復編程,存儲器編譯器的修復功能需與硅片測試工具緊密集成。

對于設計師來說極其重要的是,可根據需要選擇由晶圓代工企業制造位單元,或者進行自我設計。需進行定制設計時,與理解定制設計且可為各流程節點提供硅片數據的嵌入式存儲器供應商進行合作,具有極大的幫助作用。有了先進的設計技術,即使不需要額外的掩膜和流程修正,亦可最大限度地提高良率和可靠性。

密度

在存儲器IP的選擇上一個重要的考慮因素是,能否為各流程節點選擇不同的存儲器密度。先進的存儲器編譯器允許設計師在密度與速度之間進行權衡,比如,是選擇高密度(HD)位單元還是選擇高電流位單元。

設計師還可借助靈活的列多路復用等功能,通過控制存儲器占用形狀(可變寬度、可變高度,或正方形),優化SoC布局規劃,進而最大限度地減小存儲器對芯片整體大小的影響。部分存儲器編譯器還支持sub-words(位和字節可寫)、功率網格生成等功能,可最大限度地優化功率輸出。此外,靈活的端口分配(一個端口用于讀或寫,第二個端口用于讀和寫)亦可節省SRAM、CAM和寄存器文件的占用空間。

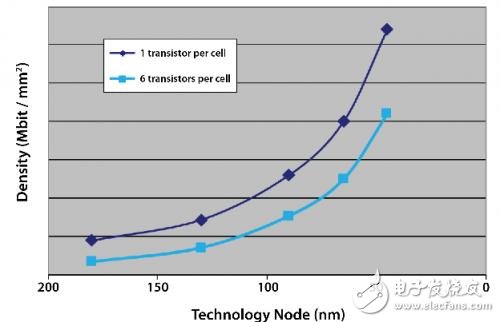

兩種嵌入式存儲器IP架構的密度關系如圖4所示。與6晶體管(6T)位單元相比,位容量一定時,單晶體管(1T)位單元最多可減少50%的芯片空間。在設計中,對速度要求較低而密度要求較高時,1T式架構是較為理想的選擇。由于可采用批量CMOS流程,省卻了額外的掩膜環節,因而有益于成本壓縮。在高速應用方面,設計師可采用6T甚至8T位單元來滿足其速度要求。

圖4:存儲器密度與不同嵌入式存儲器IP架構的比例關系。

成本

對于SoC/ASIC來說,為最大限度壓縮成本,與次優IP(常稱為“免費IP”)相比,設計師更愿選擇“節省空間”的IP參數。盡管有許多存儲器IP參數可供設計師免費選用,但在產品的整體收益性上,卻并不總是存在經濟性最好的解決方案。在很多情況下,與“免費”存儲器IP相比,通過改善獲批的嵌入式存儲器IP的密度與性能來壓縮制造成本,其效果更為顯著。

在產品的整個壽命過程中,存儲器體積的優化對量產成本的影響如表1所示。本表中,存儲器IP所占用的芯片空間以百分比表示。可通過芯片成本、量產效率以及產品壽命,計算高密度存儲器的成本壓縮效果。節省的IP空間根據圖4得出。從圖中可以看出,1T和6T存儲器的密度增量比值約為2:1.

表1:高密度IP與成本節約。

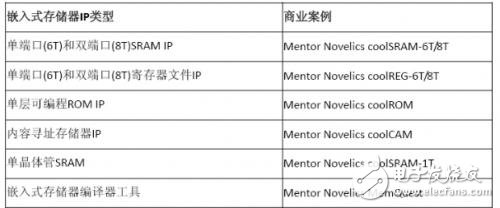

嵌入式存儲器IP選用指南

為讓您對存儲器設計中的可選要素有一個了解,現將帶有部分最先進功能的收費嵌入式存儲器類型總結如下。

單端口(6T)和雙端口(8T)SRAM IP:

由于這類存儲器架構大多適用于主流CMOS制造流程,無需額外的流程環節,因此基于傳統6T存儲單元的靜態RAM存儲器塊已成為ASIC/SoC制造中的主流。6T存儲單元采用了經過實踐檢驗的由晶圓代工廠生產的可用于高速度、低功耗設計的6T/8T位單元,是大規模程序或數據存儲器塊的理想器件。6T存儲單元可用于存儲能力從幾位到幾兆位的存儲陣列。

根據設計師是采用針對高性能還是針對低功耗優化的CMOS流程,采用此種結構的存儲陣列,經過設計,可滿足多種不同的性能需求。經高性能CMOS流程制造的SRAM塊,在功耗得到降低的同時,在40nm和28nm等高級流程節點的存取時間可降低到1ns以下。隨著流程節點的推進,外形尺寸的縮小,采用傳統6T存儲單元構建的靜態RAM,其單元尺寸將更小,存取用時也更短。

SRAM存儲單元的靜態特性使其可保留最小數目的支持電路,只需要對地址進行解碼,并向解碼器、傳感和計時電路的設計提供信號即可。

單端口(6T)和雙端口(8T)寄存器文件IP:

對于快速處理器緩存和較小的存儲器緩沖(最高約每個宏塊72Kbit)來說,這類寄存器文件存儲器IP是個不錯的選擇。寄存器同時具備占用空間最小、性能最快等特點。

單層可編程ROM IP:

這種結構功耗和速度均相對較低,特別適用于空間有限的微碼的存儲,固定數據的存儲,或體積穩步遞增的應用程序的存儲。這類IP可支持多芯片組和不同長寬比,既縮小了芯片體積,又獲得了最佳速度。為加快設計周期,部分IP還提供了用以驅動存儲器編譯器的編程腳本語言。

內容尋址存儲器IP:

由于速度更快,能耗更低,且與用于執行大量搜索任務的應用程序的算法途徑相比,占用芯片空間更小,因此這類IP大多作為TCAM(三進制)或BCAM(二進制)IP,用于搜索引擎類應用程序。通常情況下,搜索可在單個時鐘周期內完成。TCAM和BCAM通常用于包轉發、以太網地址過濾、路由查詢、固件搜索、主機ID搜索、存儲器去耦合、目錄壓縮、包分類以及多路高速緩存控制器等。

單晶體管SRAM:

這種結構雖然速度有所下降,但密度極高,可用于180 nm,160 nm,152 nm,130 nm,110 nm,90 nm以及65 nm流程。尤其適用于需要大量片上存儲空間——大多大于256Kbit,但不需要極高的存取速度的ASIC/SoC程序,以及空間有限且存儲器塊存在泄露電流的設計。本結構可生成與SRAM工作原理相似的存儲器陣列,但其基礎為單晶體管/單電容(1T)存儲單元(如動態RAM所用)。

由于采用了6T存儲陣列,因此在相同的芯片空間上,單晶體管SRAM陣列的存儲能力更強,但需要在系統控制器和邏輯層面,了解存儲器的動態特性,并在刷新控制的提供上發揮積極作用。在某些情況下,為使其看起來像簡單易用的SRAM陣列,也可能對DRAM及其自身控制器進行集成。通過高密度1T宏塊與某些提供刷新信號的支持邏輯的整合,可使存儲單元的動態特性透明化,設計師可在實施ASIC和SoC解決方案時,將存儲器塊作為靜態RAM對待。

作為可獲得許可IP,1T SRAM可從晶圓代工廠獲得。但是,由于某些此類IP需要額外掩膜層(除標準CMOS層外),增加了晶圓成本,因而限制了晶圓代工廠的可選制造空間。為使額外的晶圓加工成本物有所值,芯片上采用的總DRAM陣列大小,通常必須大于50%的芯片空間。大部分可用DRAM宏均為硬宏單元,大小、長寬比以及接口的可選空間有限。

有一種單晶體管SRAM的特殊變體,采用了可通過標準批量CMOS流程制造的架構,因此,它既無需修改掩膜,也無需額外的流程步驟。此類IP宏塊具有更高的成本效益(流程成本可節省15-20%),并且可在任何工廠進行加工,也可出于成本或生產能力等原因,改換加工工廠。這種解決方案提供了多種尺寸、長寬比和接口,可逐一指定相應的存儲器編譯器。對于系統的其余部分來說,生成的存儲器塊接口看起來就像靜態RAM,但其密度(位/單元空間)是基于6T存儲單元的存儲器陣列的2倍(經過對作為空間計算一部分的全部支持電路的平均)。對于大型存儲器陣列來說,支持電路所需全部空間所占百分比較小,存儲器塊的空間利用率也更高。

存儲器編譯器工具:

嵌入式存儲器編譯器的職責是,針對特定存儲器應用程序的確切需求,量身定做基本的IP存儲器宏單元。若適用范圍足夠廣,編譯器可允許設計師選擇最優架構,自動生成存儲器陣列,并精確確定優化程序所需的速度、密度、功率、成本、可靠性以及大小等因素。通過編譯器的自動化操作,可降低非經常性工程成本,并可減少手動陣列優化相關的潛在錯誤。編譯器不但可使客戶的內核大小、接口以及長寬比均達到最理想數值,而且還可幫助他們最大限度地縮短上市時間。作為編譯流程的一部分,編譯器還可向設計師提供存儲器陣列的電氣、物理、仿真(Verilog)、BIST/DFT模型以及綜合視圖。

表2:嵌入式存儲器IP的商業案例。

結論

為新的ASIC/SOC選擇最優嵌入式存儲器IP是設計決策的關鍵。設計師應了解適用于其特定應用程序的最佳存儲器特性的所有關鍵參數,其尋求的存儲器IP應具有足夠的適應性,可滿足目標SoC的各種需求。盡管有現成的免費存儲器IP可供使用,但與可為特定應用程序提供更好特性的收費IP相比,它并不能總是提供最佳解決方案。

經過充分調試的存儲器IP具有體積小、泄露功率低、動態能耗低、速度快等特點,可使設計師的解決方案進一步優化,不但可在產品的整個壽命周期內,帶來上百萬美元的結余,而且也使其芯片在競爭激烈的ASIC/SOC市場上,得到更好的差異化。

電子發燒友App

電子發燒友App

評論